作者 史兴荣 何进 张九柏 张子骥 贺雅娟 电子科技大学电子科学与工程学院(成都 610054)

史兴荣 (1990-),男,硕士研讨生,研讨方向:低功耗数字集成电路规划

贺雅娟 (1978-),女,副教授,研讨方向:专用集成电路与体系、超低压超低功耗数字集成电路规划等。

摘要:依据对0.18 μm规范CMOS工艺的研讨,本文规划了一套齐备的电源电压为0.4 V的亚阈值数字规范单元库。规划流程包括工艺研讨与方案规划、单元规划与物理完结、库文件的提取以及单元库验证。提出了传统沟道宽度调理与沟长偏置相结合的尺度调整战略,有用增强PMOS管驱动并减小漏电流,提高库单元稳定性。使用ISCAS基准测验电路完结亚阈值规范单元库的验证,0.4 V电压下,相同规划,依据亚阈值数字规范单元库的规划的比较于依据商用库的规划,能耗减小20%以上,数据延时也有所减小,即亚阈值规范单元库功用显着优于商用库比较。

0 导言

跟着集成电路工艺技能的不断开展,工艺线宽不断减小以寻求高集成度与高速度,带来的最大问题便是功率密度的不断增大,功耗过高问题逐步成为约束集成电路开展的重要原因。近年来鼓起的无线传感网络、医疗电子和便携式消费电子等抢手范畴,对功耗要求越来越高,低功耗技能成为工业界和学术界研讨的焦点。

在CMOS数字电路中,体系功耗包括动态功耗和静态功耗,动态功耗与供电电压的平方成正比,静态功耗与供电电压成正比,因而下降供电电压是下降功耗最有用的办法,1970年以来,极低电压规划技能的研讨被广泛打开。其间亚阈值电路规划技能,经过将体系电源电压下降至器材亚阈值区域以取得极低的体系总功耗,归于体系级低功耗技能,能到达更好的下降功耗的作用,因而成为现在研讨的热门。

大规模数字集成电路是依据规范单元库或许门阵列完结规划,要完结大规模亚阈值数字电路的完结,我就需求树立亚阈值数字规范单元库与亚阈值SRAM,针对亚阈值电压,对根本的逻辑门(与门、或门、非门、挑选器、加法器等)以及SRAM单元进行规划和优化,使其在亚阈值下到达最优功用,从而提高全体电路功用。

本文依据0.18 μm规范工艺,首要剖析了亚阈值下NMOS和PMOS失配增大的问题,并依据数字规范单元库规划流程与亚阈值单元库规划规划办法的研讨,提出了传统沟道宽度调理与沟长偏置相结合的尺度调整战略,在此基础上规划了一套电源电压为0.4 V的定制化亚阈值数字规范单元库,依据该亚阈值数字规范单元库完结数字集成电路的规划,并以ISCAS基准测验电路为载体对该亚阈值库与原商用库在0.4 V电压下从头特征化的单元库进行了比照,验证了该亚阈值数字规范单元库的齐备性与功用正确性,并且在功耗和功用方面比较原商用库有很大改进。

1 规范单元库规划流程

数字规范单元库的规划便是依据Foundry供给的工艺库,定制完结根本逻辑单元的电路和地图规划,并提取相应的时序和物理信息构成文件,供归纳东西和物理完结东西调用以完结数字集成电路的规划和剖析。规划流程包括工艺研讨剖析、单元电路和地图规划、单元库建模和库文档生成、和单元库评价验证。

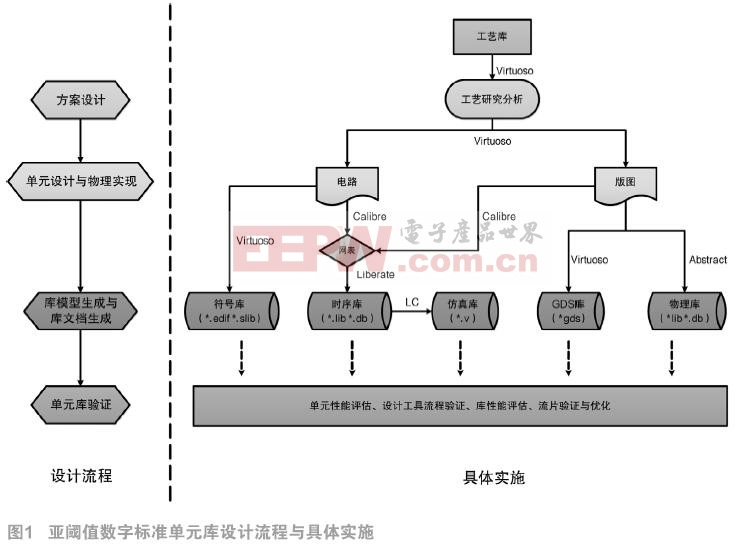

图1所示是本次亚阈值数字规范单元库规划的流程及详细施行示意图,在电路规划前,首要了解和研讨该工艺的根本特性,包括晶体管电流电压特性、器材的漏极电流等参数随沟道长度和沟道宽度的改动状况,以及PMOS和NMOS的驱动强弱等,这些依据Virtuoso完结。其次,依据Virtuoso渠道完结工艺研讨剖析以及电路图地图的规划,并依据Calibre完结单元电路网表的提取。然后,使用Liberate依据单元网表完结时序库建模,依据地图用Abstract完结物理库建模,用Library Compiler完结仿真库文件的生成,以及符号库、时序库和物理库文件的格局转化。最终,用归纳和布局布线东西完结基准电路的规划,完结亚阈值库的验证作业。

2 理论研讨与工艺剖析

2.1 最小能量点理论

亚阈值电路的理论基础便是最小能量点理论,电路总能耗包括动态能耗和动态能耗,动态能耗跟着供电电压的减小呈平方联系减小,静态能耗与时钟周期、漏电流和供电电压成正比,跟着电源电压的减小,尤其是在器材阈值电压下,时钟周期呈指数上升,导致漏电能耗敏捷增大。由此,关于特定工艺下的电路,跟着电源电压的减小,动态能耗不断减小,而静态能耗先增大,存在某一特定电源电压值,使得总能耗最小,即最小能量点,且最小能量点对应的电源电压一般在亚阈区。

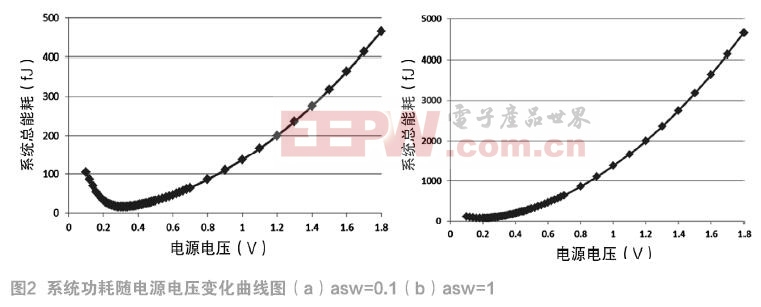

为验证最小能量点理论及确认亚阈值规范单元库的电源电压,针对所触及的工艺,规划了验证电路。验证电路包括10条50级的反相器链,经过给定10条链路不同的输入来操控开关活动性的巨细,巨细能够设定为0.1、0.2、……、1.0。如图2所示,别离是开关活动因子asw等于0.1和1时不同电压下的体系总功耗随电源电压改动曲线,能够看出,最小能耗点散布在电源电压为0.2 V~0.4 V规模内。本规划中,考虑到体系稳定性及数字单元库的适用规模,电源电压设定为0.4 V。

2.2 晶体管电流电压特性

NMOS和PMOS的驱动才能是不一样的,即存在不匹配,在规范电压下(即超阈值电压),NMOS的驱动才能约为PMOS驱动才能的两倍,这得益于电子迁移率为空穴迁移率两倍多,在树立规范单元库时,单元规划时就要考虑到NMOS/PMOS失配,经过尺度调理来完结单元的上拉下拉匹配。可是在亚阈值电压下,由MOS模型剖析可知,NMOS/PMOS失配会增大,因而将商用规范单元库运用到低压电路中,电路功用会严峻下降,会呈现噪声容限下降,抗工艺动摇才能下降,乃至逻辑误判导致电路无法正常作业等。

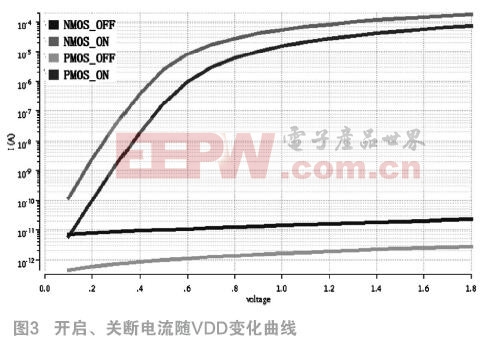

对相同尺度的NMOS管和PMOS管进行仿真,晶体管的敞开电流和关断电流随电源电压的改动曲线,如图3所示,跟着电源电压的不断减小,NMOS管和PMOS管的敞开电流和关断电流都不断减小,可是NMOS与PMOS的敞开电流之比却在不断增大,在电压为0.4 V时,大尺度管PMOS/NMOS敞开电流比已接近于7,而关于最小尺度管,乃至高达20,即PMOS和NMOS存在严峻的不匹配,这给咱们规范单元规划时上拉下拉平衡形成很大困难。

2.3 反短沟道效应

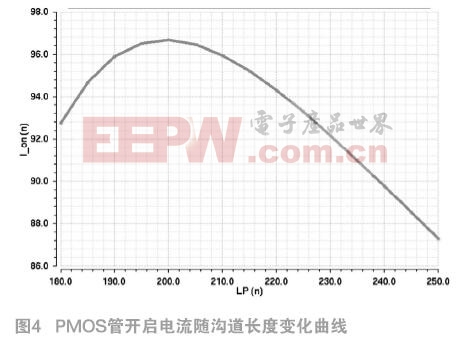

跟着工艺尺度的不断减小,亚阈值电压下,晶体管电流表现出显着的反短沟道效应,跟着沟道长度L的改动,晶体管的敞开电流表现出先增大后减小的改动趋势,即存在最优沟道长度。针对本工艺,经过对NMOS管和PMOS管的仿真发现,NMOS管敞开电流不存在反短沟道效应,而PMOS管敞开电流存在显着的反短沟道效应,即敞开电流I_on跟着沟道长度LP的增大先增大后减小,如图4所示,能够看出NMOS管敞开电流在LP=200 nm时到达最大。进一步研讨发现,最优沟道长度与沟道宽度相关,且增大LP存在面积和漏电流增大的不良影响,因而在实践库单元规划时,咱们将NMOS的沟道长度取值为180 nm,即最小沟道长度,PMOS的沟道长度取值为190 nm,即沟道增量约为最小沟道长度的5%。

3 亚阈值库的规划

3.1 单元类型挑选与结构规划

规范单元库规划中,库单元的和数量影响着归纳东西在映射和优化进程的有用应,库单元品种越丰厚,电路的优化就越充沛。关于亚阈值规范单元库,因为电源电压较低,有些杂乱单元不能作业,有些单元能作业可是稳定性大幅度下降,为确保功用正常且具有满足的稳定性,则需求对这些单元进行挑选。选用扇入比较小的逻辑单元,除掉NAND4、NOR4等扇入大的逻辑,而时序优化单元较杂乱且功耗较大也需求除掉,触发器和锁存器必不可少,可是其品种能够简化,时钟树逻辑单元和物理完结单元必不可少。每种逻辑又包括多种不同驱动才能,也规划了低功耗单元,关于OR2、NOR2等稳定性差的单元,为确保单元稳定性没有规划低功耗单元。

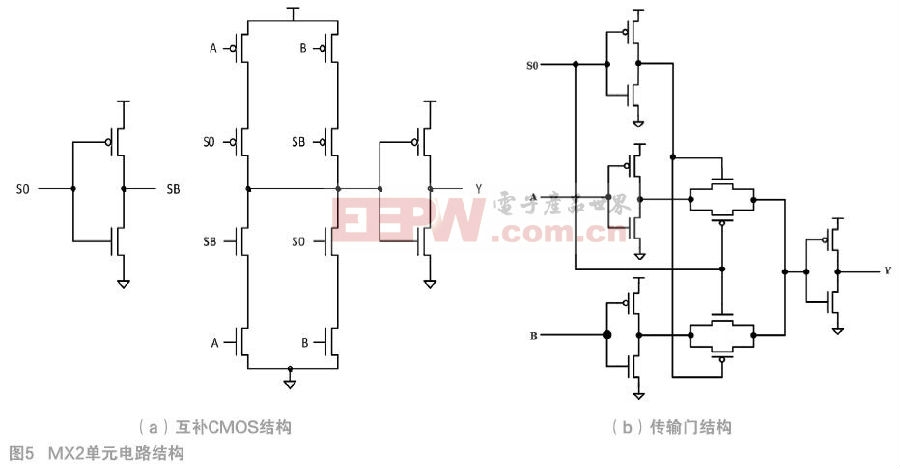

关于INV、NAND2、NOR2等简略的库单元,直接选用传统的静态互补CMOS结构,而关于MX、XOR、XNOR、DFF和LATCH等比较杂乱单元,传统互补CMOS结构在亚阈值电压下稳定性缺乏。因而需求改动结构,选用在低压下功用更好的传输门结构规划。以二选一挑选单元MX2为例阐明传输门结构的优势,图5所示是MX2单元电路结构(a)互补CMOS结构(b)传输门结构。在互补CMOS结构中,有两个PMOS串联的结构,PMOS在低压下驱动很小,相同晶体管尺度会导致单元稳定性较差,且单元延时较大。传输门结构MX2单元由传输门和反相器构成,没有PMOS串联或NMOS串联结构,能够作业在较低电压,稳定性更高。传输门速度由NMOS管决议,延时更小,且能够选用最小尺度晶体管完结规划,功耗小。

3.2 单元尺度规划战略

规范单元尺度规划,便是期望找到最优的尺度组合,以使电路在功用正确的前提下,完结延时、功耗和面积的统筹。依据前面第三章对工艺的剖析可知,本工艺库PMOS管存在显着的电流反短沟道效应,即跟着栅极长度L的增大电流先更大后减小,存在最优L值,所以选用传统栅极宽度W调理战略与栅极长度L偏置相结合的尺度调理战略:

(1)针对PMOS存在电流反短沟道效应,进一步仿真发现最优L值与晶体管栅极宽度W相关,但改动比较小,因而为简化单元仿真量,PMOS管的栅极长度一致设定为190 nm,NMOS管的栅极长度一致设定为180 nm。

(2)依据0.4V电压下的NMOS/PMOS驱动比,和详细单元的结构剖析,以上拉网络和下拉网络的匹配为方针,确认PMOS和NMOS的栅极宽度W的大致规模。

(3)经过剖析单元的功耗、延时和面积等参数,确认单元的优化方针函数为f(P, D)=Pi*D,P是单元功耗,因为功耗与面积正相关,也包括了对面积的考虑,D为单元延时,延时为上升下降延时的平均值,考虑了上拉网络和下拉网络的平衡以及单元稳定性。i为调理系数,用于调理单元功耗和单元延时的比重,此处i取值为1。调整单元中各晶体管栅极宽度W,使得方针函数到达最优,确认出单元的最优尺度。

4 亚阈值库的评价验证

4.1 单元库稳定性评价

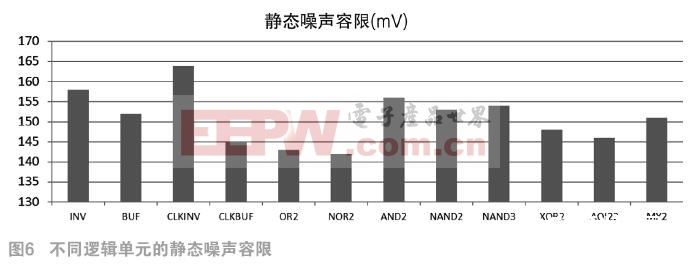

静态噪声容限是衡量单元稳定性的重要参数,丈量不同逻辑单元的静态噪声容限,来评价咱们规划的亚阈值库的单元稳定性。图6所示是不同逻辑单元的静态噪声容限,能够看出因为其PMOS管串联的结构特性,库中NOR2单元的静态噪声容限最小,为142 mV,占电源电压的35.5%,证明咱们的库单元能够作业在很低电压下,单元库具有很好的稳定性。

4.2 单元库的验证

本次为了验证所树立的亚阈值单元库的功用和功用,选用ISCAS85和ISCAS89基准测验电路,选取了典型的五个电路,其间C7552选自ISCAS85是纯组合逻辑电路,其他四个电路选自ISCAS89是时序电路。一起对规范单元的单元库在0.4 V电压下进行从头特征化,记为商用0.4 V库,用于和亚阈值库比照。别离依据亚阈值库和商用0.4 V库,完结上述所选基准测验电路的规划,仿真比照成果如表1所示,表1中显现,依据亚阈值库的规划在延时和功耗方面都要显着优于商用0.4 V库,动态功耗和静态功耗都减小了20%以上,且延时也有所减小,因而电路的功耗延时积PDP减小超越37%。即依据亚阈值单元库的电路功用提高,且功耗大幅度下降,验证了亚阈值单元库的齐备性和杰出的功用,及其低功耗特性。

5 结束语

依据对0.18μm规范CMOS工艺最小能耗点的研讨,以及对亚阈值电压下NMOS和PMOS电流电压特性和PMOS的反短沟道效应的研讨,提出了沟道宽度调理和PMOS沟长调制结合的尺度规划战略,依据数字规范单元库规划流程树立了一套齐备的亚阈值数字规范单元库。亚阈值库单元的噪声容限在电源电压的35%以上,并选用ISCAS基准电路完结单元库的验证。0.4 V电压下,与商用单元库比较,亚阈值单元库功耗减小了20%以上,且功用有所改进。验证了亚阈值规范单元库单元的稳定性,以及单元库的低功耗特性。

参考文献:

[1]Calhoun B H, Wang A, Chandrakasan A. Modeling and sizing for minimum energy operation in subthreshold circuits[J]. IEEE J. Solid-State Circuits, 2005, 40(9): 1778-1786.

[2]Qian Xie, Jun Xu, Yuan Taur. Review and critique of analytic models of MOSFET short-channel effects in subthreshold[J]. IEEE Transactions on electron devices, 2012, 59(6): 1569-1579.

[3]Alioto M. Ultra-Low Power VLSI Circuit Design Demystified and Explained: A Tutorial[J]. IEEE Trans. Circuits Syst. I, Reg. Papers, 2012, 59(1): 3-29.

[4]Gupta K, Raychowdhury A, Roy K. Digital computation in subthreshold region for ultra-low-power operation: A device-circuit-architecture codesign perspective[J]. Proceedings of the IEEE, 2010, 98(2):160-190.

[5]Liu Bo, Ashouei M, Standard cell sizing for subthreshold operation[C]. Proceeding of the 49th Design Automation Conference. San Francisco, USA, 2012: 425-128.

[6]Gibiluka M, Moreira M. A standard cell characterization flow for non-standard voltage supplies[C]. 29th Symposium on Integrated Circuits and Systems Design. Belo Horizonte, Brazil, 2016

本文来源于《电子产品世界》2018年第11期第38页,欢迎您写论文时引证,并注明出处。