RS-485 总线是半双工的通讯总线,因而一般需求MCU操控RS-485收发器的收发状况。为节约MCU的I/O资源,RS-485主动收发型收发器应运而生,但该类收发器或多或少会遇到一些运用问题,这一类问题该怎么处理?本文将从作业原理为你揭晓。

一、主动收发电路简介及运用简析

1、主动收发电路原理

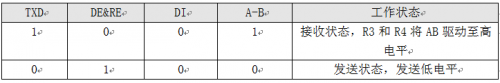

常见的RS-485主动收发电路如图1所示,电路的逻辑真值表如表1所示,当TXD为低电平时,DE和RE为高电平,RS-485收发器处于发送状况,AB处于低电平,即向其他节点发送低电平信号;当TXD由低电平变为高电平时,DE和RE变为低电平,RS-485收发器处于接纳状况,此刻AB引脚处于高阻状况,R3将B引脚拉至GND,R4将A引脚拉至VCC,此刻AB为高电平,即向其他节点发送高电平信号。因为TXD为高电平时,RS-485收发器处于接纳状况,因而只需将TXD坚持为高电平即可接纳数据,即主动收发电路发送高电平时一起也是接纳状况。

图1 RS-485主动收发示意图

表1 主动收发电路示意图

二、主动收发电路常见运用问题及处理方案

1、通讯速度较慢

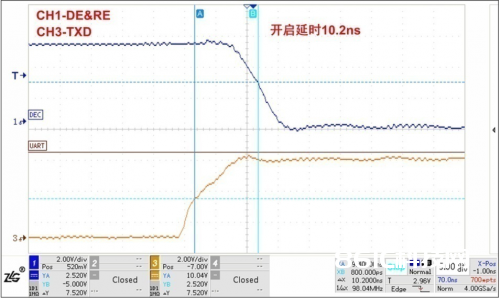

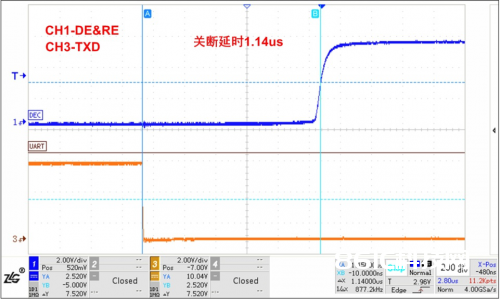

RS-485主动收发通讯速度较慢的原因主要有两个。一是若运用图1所示的主动收发电路,三极管的关断时刻较长(主要是因为三极管关断时的存储时刻较长),图1中所示参数的三极管反相电路,敞开延时时刻如图2所示为10.2ns,关断延时时刻如图3所示为1.14μs,因而若TXD发送低电平,DE&RE引脚较长时刻后才会升至高电平,发送低电平的延时时刻较长,图1所示电路发送低电平信号延时时刻如图4所示为1.468μs。

图2敞开延时时刻

图3 关断延时时刻

图4 发送低电平信号延时

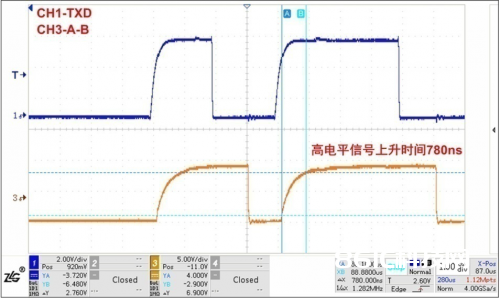

二是主动收发电路发送高电平是经过外部上下拉电阻驱动的,上升沿较缓慢,波形如图5所示,能够看出,发送高电平的上升沿较为缓慢,约束了高速通讯的运用。

图5 发送高电平上升时刻

2、高波特率通讯时存在通讯反常危险

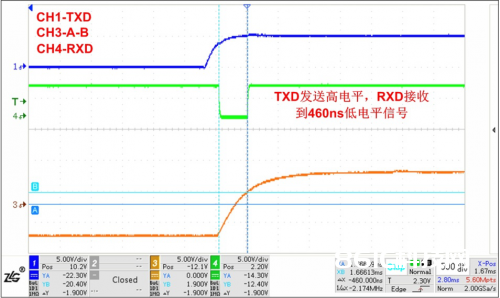

如图6所示,TXD变为高电平,DE&RE引脚降为低电平,AB差分电压缓慢上升,因为此刻RS-485收发器现已处于接纳状况,在AB差分电压上升至RS-485收发器门限电平前RXD引脚会呈现到一段时刻的低电平信号,例如门限电平为-200mV~-50mV的收发器,AB差分电压上升至-50mV前RS-485收发器均可输出低电平,此低电平信号的时刻与AB差分电压上升时刻和RS-485收发器的接纳延时有关。因为串口一般是将每个位分红16份,检测中心的3份的电平信号然后确认此位的信号凹凸,因而若此低电平信号坚持至每个位的信号检测时,则会使MCU接纳到一个开始位,然后接纳到过错的数据,因而这个问题相同约束了高速通讯的运用而且降低了通讯的可靠性。

图 6TXD发送高电平信号,RXD接纳到一段低电平信号

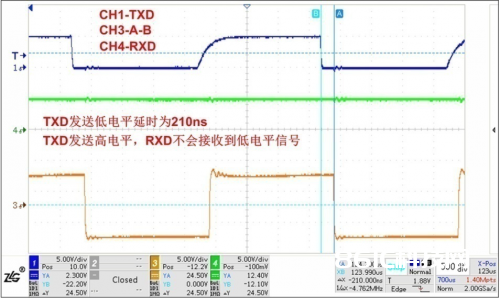

针对此类问题,可选用致远电子的宽压输入贴片式阻隔RS-485主动收发模块SC4450S(如图7),该模块通讯速度高达500kbps,而且不会呈现发送高电平时接纳到一段时刻低电平信号的现象,通讯波形如图8所示,极大地提高了通讯可靠性。

图7 贴片式阻隔RS-485收发器SC4450S

图8 SC4450S通讯波形