3.数字时钟办理模块(DCM)

业界大多数FPGA 均供给数字时钟办理( 赛灵思公司的悉数FPGA 均具有这种特性)。赛灵思公司推出最先进的FPGA 供给数字时钟办理和相位环路确定。相位环路确定能够供给准确的时钟归纳,且能够下降颤动,并完结过滤功用。

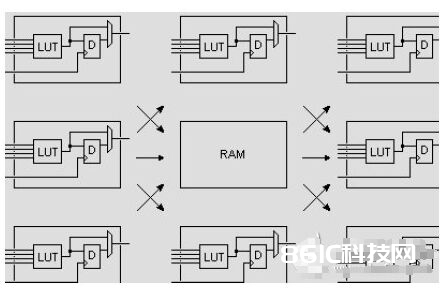

4.嵌入式块RAM(BRAM)

大多数FPGA 都具有内嵌的块RAM,这大大拓宽了FPGA 的使用规模和灵敏性。块RAM 可被装备为单端口RAM、双端口RAM、内容地址存储器(CAM) 以及FIFO 等常用存储结构。RAM、FIFO 是比较遍及的概念,在此就不冗述。CAM 存储器在其内部的每个存储单元中都有一个比较逻辑,写入CAM 中的数据会和内部的每一个数据进行比较,并回来与端口数据相同的一切数据的地址,因而在路由的地址交换器中有广泛的使用。除了块RAM,还能够将FPGA 中的LUT 灵敏地装备成RAM、ROM 和FIFO 等结构。在实践使用中,芯片内部块RAM 的数量也是挑选芯片的一个重要因素。

图2-7 内嵌的块RAM

单片块RAM 的容量为18k 比特,即位宽为18 比特、深度为1024,能够依据需要改动其位宽和深度,但要满意两个准则:首要,修改后的容量( 位宽 深度) 不能大于18k 比特;其次,位宽最大不能超过36 比特。当然,能够将多片块RAM级联起来构成更大的RAM,此刻只受限于芯片内块RAM的数量,而不再受上面两条准则束缚。

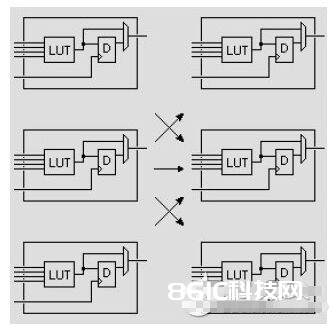

5. 丰厚的布线资源

布线资源连通FPGA 内部的一切单元,而连线的长度和工艺决议着信号在连线上的驱动才能和传输速度。FPGA 芯片内部有着丰厚的布线资源,依据工艺、长度、宽度和散布方位的不同而划分为4类不同的类别。第一类是大局布线资源,用于芯片内部大局时钟和大局复位/ 置位的布线;第二类是长线资源,用以完结芯片Bank 间的高速信号和第二大局时钟信号的布线;第三类是短线资源,用于完结根本逻辑单元之间的逻辑互连和布线;第四类是散布式的布线资源,用于专有时钟、复位等操控信号线。

图2-8 FPGA内部互连布线

在实践中规划者不需要直接挑选布线资源,布局布线器可自动地依据输入逻辑网表的拓扑结构和束缚条件挑选布线资源来连通各个模块单元。从本质上讲,布线资源的使用方法和规划的成果有亲近、直接的联系。