8.3依据NIOSII的开发规划流程

NIOSII运用NIOSIIIDE集成开发环境来完结整个软件工程的修正、编译、调试和下载。在选用NIOS处理器规划嵌入式体系时,一般会依照以下进程。

(1)剖析体系需求阐明,包含功用需求和功能束缚等。

(2)依据剖析成果,挑选片外外设或片内IP(知识产权核)。除此以外,还要对挑选的IP和外设进行开端功能评价,以确保能够满意体系需求。

(3)设定IP和体系参数。

(4)确认体系互联逻辑,分配FPGA的引脚等。

(5)结合NIOS供给的软件开发包进行软件开发。

8.3.1硬件开发流程

首要来看一下NIOS的硬件体系组成。

1.NIOS硬件组成

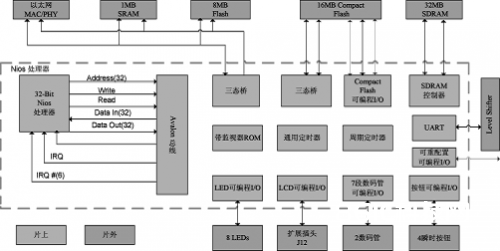

如图8.2所示为典型NIOSII体系的硬件组成。

图8.2NIOSII体系的硬件组成

如图8.3所示为典型NIOSCPU的体系框图。

图8.3NIOSCPU体系框图

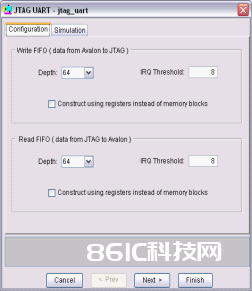

咱们能够将图8.3的体系结构区分如下。

其间,片内逻辑是指完结在FPGA内部的电路规划,体系模块指的是由SOPCBuilder主动生成的规划。

SOPCBuilder会依据用户挑选的IP生成相应的HDL描绘文件(体系模块文件),这些文件与用户逻辑区域内的规划描绘文件一同由Quartus软件归纳,然后下载到FPGA内,这样就构成了体系的硬件根底。

体系模块包含至少一个Avalon主外设和整个Avalon总线模块。体系模块一般还包含一些Avalon从外设,例如UART、PIO和定时器等。SOPCBuilder能够协助规划者从IP库寻觅适宜的IP并很快地集成一个体系,它选用图形用户界面(GUI)显现和安排IP模块,能够主动生成IP模块互连逻辑以及生成用于归纳和模仿的文件,使得规划者能够轻松完结体系规划。

当用户运用SOPCBuilder创立一个新的体系时,SOPCBuilder会为该体系主动生成一个PTF文件,一切的规划信息都存储在该PTF文件里。当运用SOPCBuilder从头翻开一个已有的体系时,SOPCBuilder会从而且只从PTF文件中读取体系详细规划信息。

用户逻辑区内能够包含用户自界说的Avalon外设,以及同体系模块无关的其他的用户自界说逻辑。硬件体系树立起来今后,用户能够运用Altera公司供给的NIOSIIIDE东西结合SOPCBuilder生成的与硬件体系对应的软件开发包来开发用户软件。

下面介绍运用这些规划东西进行NIOSII开发的流程。

2.NIOSII硬件开发流程

下面是NIOSII硬件开发流程的首要进程。

·用SOPCBuilder来挑选适宜的CPU、存储器及外围器材,比方片内存储器、PIO、UART和片外存储器接口。

·运用QuartusII软件选取详细的器材,并对SOPCBuilder生成HDL规划文件进行布局布线;再依据开发板分配I/O管脚;编译完后生成合适方针器材的网表。

·运用下载电缆将装备文件下载到开发板上。当校验硬件或时钟结束后,就能够开端软件开发工作了。

下面这个比方即将增加一个NIOSII体系得一切硬件部分,首要包含以下内容。

(1)挑选CPU。

挑选NIOSII/e经济型处理器,其特点是占用逻辑资源少,编译速度快,不包含缓存,如图8.4所示。

图8.4挑选NIOSII处理器

(2)挑选JTAG调试模块。

挑选第一层JTAG硬件调试模块,如图8.5所示。

图8.5挑选JTAG调试模块

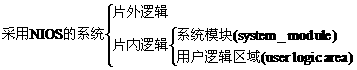

(3)设置JTAGUART接口。

它是NIOSII体系嵌入式处理器新增加的接口元件,经过内嵌在AlteraFPGA内部的联合测验举动组(JTAG)电路,在PC主机和FPGA之间进行串行字符流通讯。特点是在运转时在调试区输入信息能够与FPGA进行交互。

如图8.6所示,运用默许选项即可。

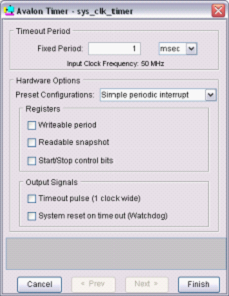

(4)设置定时器。

如图8.7所示,定时器关于HAL体系库中的器材驱动十分有用,比方JTAGUART驱动运用定时器来完结10s的暂停。挑选Intervaltimer在设置导游中周期挑选1msec,预设置(PresetConfigurations)中挑选Full-featured。

图8.6JTAGUART接口 图8.7Avalon总线定时器

(5)增加外部Flash。

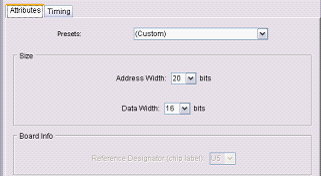

设置Flash地址宽度为20bits,带宽为16bits,如图8.8所示。

图8.8增加外部Flash

图8.8增加外部Flash(续)

假如用户程序和数据比较大,超出了EPCS1的容量,则程序和数据能够保存在一般Flash中。Flash的烧写能够选用NIOSIIIDE的“FlashProgrammer”来烧写,详细操作进程请参阅/altera/kits/NIOS2/documents目录下“ug_NIOS2_flash_programmer.pdf”。

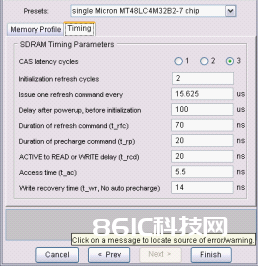

(6)增加外部SDRAM。

一般的体系都需求用户指定一个内存空间,这个内存是指RAM,能够是片上的,也能够是片外的SDRAM或SRAM等。假如用户程序较大,超出了EP1C20所能定制的最大片上RAM容量,则也能够将程序放在SDRAM中运转。

将SDRAM进行如图8.9所示的设置。

图8.9增加外部SDRAM

(7)设置Avalon外部总线。

软件运用Avalon接口来衔接片上元件和Avalon主从端口的。在NIOS开发板上,要完结NIOS体系与FPGA片外存储器通讯,就有必要在Avalon总线和衔接外部存储器的总线之间增加一个桥,这个桥便是Avalon三态总线。

在如图8.10中挑选为Avalon外部总线增加寄存器。

(8)增加串行通讯设备UART。

通用串行总线RS-232协议是咱们最常用的通讯协议,所以把它也增加到咱们的体系里。留意挑选所需的数据帧格局,如图8.11所示。

图8.10设置Avalon外部总线 图8.11增加串行通讯设备UART

(9)增加LCD显现。

运用规范16027字符型液晶显现器。

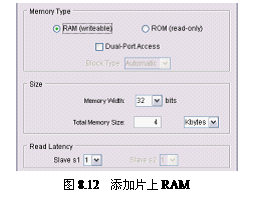

(10)增加片上RAM。

如图8.12所示,为SOPC体系增加片上RAM资源,并设置RAM参数。

(11)增加systemid。

(12)增加8个LED和输入设备按键开关。

以上几个进程包含了一个规范SOPC一般所需求的设备,依据下面信息栏中的提示把RAM的数据线衔接到总线上。接下来指定Flash地址为基地址,主动分配基地址及中止。

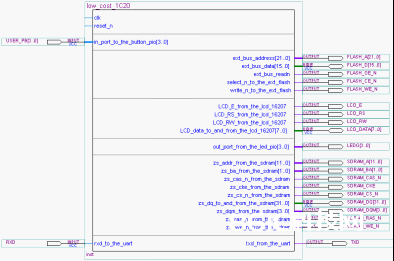

最终完结的SOPC模块如图8.13所示。

接下来就能够在QuartusII中树立完好的体系,参加锁相环、界说管脚等,并进行编译。这部分的内容详见本书其他章节的介绍。

需求留意的是由于Flash与SRAM共用一条数据总线,所以要把SRAM的片选封闭,如图8.14所示。

至此,全体SOPC硬件体系树立结束,其原理图如图8.15所示。

这样一个硬件体系规划现已比较完好了,能够作一些规划,比方Flash读写、液晶显现、串口传输等功用。把这些集合起来就能够用C++软件编写一个简略的图画处理算法。

下面介绍一下SOPC体系的软件开发流程。

图8.13树立的SOPC模块

图8.14封闭SRAM片选

图8.15SOPC体系原理图

8.3.2软件开发流程

体系软件规划详细工作如下。

(1)在用SOPCBuilder体系集成软件进行硬件规划一起,开端编写C/C++软件,比方算法或控制程序。用户能够运用现成的软件库和敞开的操作体系内核加速开发进程。

(2)在NIOSIIIDE中树立新的软件工程时,IDE会依据SOPCBuilder对体系的硬件装备主动定制HAL(硬件笼统层)体系库。这个体系库能够为程序和底层硬件的通讯供给接口驱动程序。

(3)运用NIOSIIIDE编译调试软件。

(4)在硬件逻辑现已下载到开发板的根底大将软件下载到开发板上并在硬件上运转。

下面首要介绍运用SOPCBuilder来为一个NIOSⅡ嵌入式处理器体系进行软件开发的进程,详细完结进程如下。

(1)进行硬件开发,如8.3.1末节所示。

(2)发动NIOSIIIDE。

首要在AlterSOPCBuilder中,单击RunNIOSIIIDE,发动NIOSIIIDE,如图8.16所示。

图8.16NIOSIIIDE界面

(3)新建软件工程。

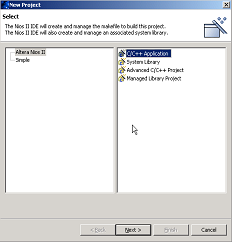

挑选“File”菜单的“New”菜单的“Project”选项,敞开“NewProject”对话框,挑选“C/C++Application”,如图8.17所示。

(4)挑选软件模板。

在新建软件工程对话框中单击“Next”按钮,为SOPC体系挑选软件模板,如图8.18所示。

图8.17新建软件工程 图8.18挑选软件模板

(5)获取SOPC体系信息。

单击“SOPCBuilderSystem”右边的“Browse”按钮翻开目录对话框,从该工程目录下找到“NIOSII_c.ptf”,由于NIOSIIIDE有必要从这个文件获取该体系的相关信息。翻开该文件后,界面显现如图8.19所示。

图8.19新建的软件工程

单击“Finish”按钮,即可树立一个名为Hello_LED_0的软件模板工程。

(6)修正软件代码。

(7)设置工程优化等级。

编译之前咱们先对项目进行一些设置,以使编译器编译出更高效、占用空间更小的代码。右键单击工程称号,在弹出的菜单中挑选“Properties”选项,如图8.20所示。

图8.20设置工程特点

单击后翻开工程特点对话框,在“ConfigurationSettings”点击“General”页面,在“OptimizationLevel”(优化等级)中挑选“Optimizesize(-Os)”,如图8.21所示。

图8.21工程优化等级

(8)设置体系库特点。

右键单击*_syslib[NIOSII_c]工程称号,在弹出的菜单中挑选“Properties”选项,如图8.22所示。

图8.22设置体系库特点

在体系库工程特点对话框中,同样在“ConfigurationSettings”点击“General”页面,在“OptimizationLevel”中挑选“Optimizesize(-Os)”,如图8.23所示。

图8.23体系库工程优化等级

然后,单击该对话框左边的“SystemLibrary”翻开“SystemLibrary”特点页面。将“Maxfiledescriptors:”栏改为4,铲除“Cleanexit(flushbuffers)”和“Linkwithprofilinglibrary”,选上“Reduceddevicedrivers”和“SmallClibrary”,如图8.24所示。

单击“OK”按钮,完结设置。以上设置首要意图是为了优化程序,并削减程序占用内存空间。

图8.24设置体系库其他特点

(9)编译。

右键单击工程,在弹出的菜单中挑选“BuildProject”选项,开端进行软件工程编译(为使编译进程愈加顺畅,此刻最好封闭杀毒软件和其他占用电脑资源较大的软件)。

假如工程规划无误,能够看到以下信息:“Buildcompleted”。假如看到了该条提示,表明软件编译成功,能够看到程序占用空间等信息。

(10)调试。

将ByteBlasterII下载线接到FPGA试验渠道的JTAG口,接上5V电源。挑选“Run”菜单下的“DebugAs”选项,挑选“NIOSIIHardware”,如图8.26所示。

图8.26翻开调试界面

挑选后,NIOSIIIDE会翻开调试界面(DebugPerspective)。能够在程序中设置断点,运转中止在断点处(图8.27的箭头处),如图8.27所示。

图8.27调试至断点

单击持续履行(Resume)按钮,程序就会持续运转。单击暂停按钮,程序暂停运转。单击中止按钮,将退出运转,如图8.28所示。

图8.28调试按钮

如需对程序进行修正,单击中止按钮退出运转,然后单击如图8.29所示的按钮回到C/C++修正界面。

挑选后,即可回来程序修正界面修正代码,然后后再重复上述调试进程。

(11)编译并下载。

编写完软件工程后,咱们还要回到QuartusⅡ里边临整个体系进行编译。挑选“Processing”菜单下面的“StarCompilation”。编译成功今后咱们就能够挑选“Tools”菜单里边的“Programmer”,下载整个装备到FPGA中去了。

至此整个SOPC体系的软硬件开发流程就现已介绍结束。读者能够着手规划自己的SOPC体系了。