1 导言

近年来,因为微电子学和核算机技能的迅速开展,给EDA技能职业带来了巨大的改变。 HDL(hardware description language)硬件描绘言语是一种描绘电路行为的言语,是规划者和EDA东西的界面,规划者经过HDL描绘自己的规划目标。现在比较盛行的HDL主要有Verilog HDL、VHDL、AHDL等,其间Verilog HDL和VHDL因为合适规范化的方面而终究成为IEEE规范。可是Verilog HDL比VHDL更简单把握,而且完结同一功用的Verilog HDL条数一般仅为VHDL的1/3,Verilog HDL 长于描绘更低层规划包含结构级和物理层的规划,而VHDL规划技能很不直观,规划人员需求有EDA编程根底,经过半年左右的专业培训才干把握,所以用Verilog HDL的优越性高一些。作为学习HDL规划办法的入门和根底,是一种值得大力推广的硬件描绘言语。

2 汉明码的基本原理

汉明码是一种可以纠正一个错码且编码功率较高的线性码。在偶数监督码中,不管信息位有多少,监督位只要一位,它使码组中“1”的个数为偶数,在接纳端解码的时分,实践便是核算S= an-1⊕ an-2⊕。。。。⊕a0,若S=0,就以为无错,若S=1,就以为有错。上式称为监督联系式,S为校对子。因为校对子S的取值只要这样两种,它只能代表有错和无错两种信息,而不能指出错码的方位。假如监督位添加一位,即变成两位,或许有四种组合:00,01,10,11,故能表明四种不同虚报许,若用其间一种表明无错,则其他三种就有或许用来指示一位错码 的3种不同方位,同理,r个监督联系式就能指示一位错码的(2r-1)个或许方位.一般说来,若码长为n,信息位数为k,则监督位数r=n-k.假如期望用r个监督位够造出r个监督联系式来指示一位错码的n种或许方位,则要求

2r-1≥n ; 2r≥k+r+1;

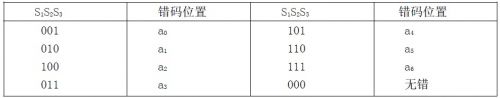

设分组码(n, k)中k=4.为纠正一位错码,要求监督位数r≥3.若取r=3,则n= k+r=7.咱们用a6a5a4…a0表明7个码元,用S1S2S3表明三个监督联系式中的校对子,则S1S2S3的值与错码方位的联系如下表.

由表可知,仅当一错码方位在 a2 a4 a5 a6时,校对子S1为1,不然S1为0.这就意味着a2 a4 a5 和a6 构成偶数监督联系

S1= a2 ⊕ a4⊕ a5⊕a6

同理

S2= a1 ⊕ a3⊕a5⊕a6

S3= a0 ⊕a3⊕a4⊕a6

在发送端编码时,信息位a6 a5 a4和 a3 的值决定于输入信号,因而它们是随机的。监督位a2 a1 和 a0 应依据信息位的取值按监督联系来确认,即监督位应使上三式中的S1S2S3的值为零。

a2⊕a4⊕a5⊕a6=0

a1⊕a3⊕a5⊕a6 =0

a0⊕a3⊕a4⊕a6=0

有上式移项运算,解出监督位

a2= a4⊕a5⊕a6

a1= a3⊕a5⊕a6

a0= a3⊕a4⊕a6

根给定信息位后,可直接核算出监督位,如下表

接纳到每个码组后,先按上式核算出S1 S2 和S3 ,再按上表判别错码状况。例如,若接纳码组为0000110,则核算的S1 =1,S2 =1,S3 =0,因为S1 S2 S3 等于110,可知a5位有一错码。上述办法构成的码称为汉明码。表Ⅱ所列的(7,4)汉明码最小码距是d0=3,这种码能纠正一个错码或检测两个错码。汉明码的编码功率等于k/n=(2r-1-r)/( 2r-1)=1-r/(2r-1)=1-r/n.当n很大时,则编码功率挨近1。可见汉明码是一种高效码。

3 编码电路的完成

本规划的开发渠道是MAX+PLUSⅡ[4], MAX+PLUSⅡ是Altra公司专为本公司出产的PLD的研发和运用开发的软件它的杰出特色在于其强壮的归纳才能和布局布线才能,别的还具有适用范围广、器材结构独立、通用性好、兼容性好、集成度与自动化程度高以及易学易用的特色.

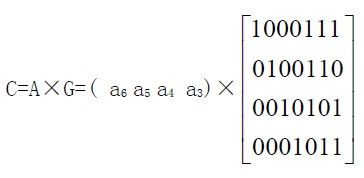

编码器规划的特色是运用了矩阵的乘法,假定A是输入至编码器的数据向量,G是矩阵乘法的产生矩阵,C是汉明码码字,那么依据矩阵乘法核算得到汉明码字。

程序编写如下

module bianma(clk,reset,data_in,dcin,code_out,dcout);

input clk,reset;//时钟和复位信号.

input[3:0] data_in;//输入数据变量,位宽为4bit.

input dcin;//输入有用操控信号,界说1表无效,编码器不输出码字,界说0表有用.

output[6:0] code_out;//编码器输出,位宽为7bit.

output dcout;//输出有用操控信号,界说1表无效.界说0表有用.

reg[6:0] code_out;

reg dcout;

reg[3:0] datareg;

reg dcinreg;

wire c0=datareg[3];

wire c1=datareg[2];

wire c2=datareg[1];

wire c3=datareg[0];

wire c4=datareg[3]^datareg[2]^datareg[1];

wire c5=datareg[3]^datareg[2]^datareg[0];

wire c6=datareg[3]^datareg[1]^datareg[0];

always@(posedge clk or negedge reset)//依据时钟信号和输入使能信号收集数据.

if(!reset)

dcinreg=1;

else

dcinreg=dcin;

always@(posedge clk)//收集是否有用.

if (reset)

datareg=0;

else if(!dcin)

datareg=data_in;

always@(posedge clk)//码字在数据向量收集后一个时钟周期核算得到.

if (reset)

dcout=1;

else

dcout=dcinreg;

always@(posedge clk)//码字输出是否有用.

if(reset)

code_out =0;

else

code_out={c0,c1,c2,c3,c4,c5,c6};

endmodule

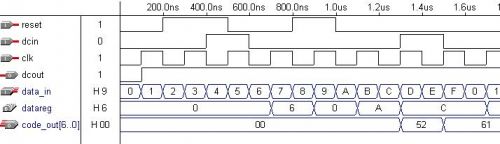

该源程序经过编译和仿真,时序图如下所示,得到成果契合体系功用要求

本规划运用的芯片为MAX3000A系列EPM3032ALC44-4,芯片的输入输出端口的规划选用D触发器组来缓存数据,保证收集数据向量和发送的码字安稳,并于时钟信号严厉同步。

4 结束语

本文经过介绍汉明码的编码原理,进而用Verilog HDL进行汉明码编码器的规划,并经过时序仿真波形图进行逻辑剖析,成果契合实践状况.而Verilog HDL有着相似C言语的编程风格,易于学习和把握,与传统的原理图规划办法相比较, Verilog HDL更合适于规划日益增大的数字体系. Verilog HDL等硬件描绘言语进行数字体系的规划是EDA开展的趋势,在数字体系的规划中有着广泛的空间.