作者 温梓慎1 崔玉龙2 范好亮3 1.河北工业大学 电气工程学院(天津 300130) 2.北京化工大学(北京 100029) 3.河北长孚电气设备有限公司 (河北 保定 071051)

*基金项目:河北省科技型中小企业技能创新资金项目(编号:16C1303121010)

温梓慎(1989-),男,硕士生,研讨方向:电器可靠性及检测技能;崔玉龙,男,博士生,高级工程师,研讨方向:无线电能传输技能,工业电气主动化和电力电子技能使用;范好亮,男,硕士,工程师,研讨方向:无线电能传输设备。

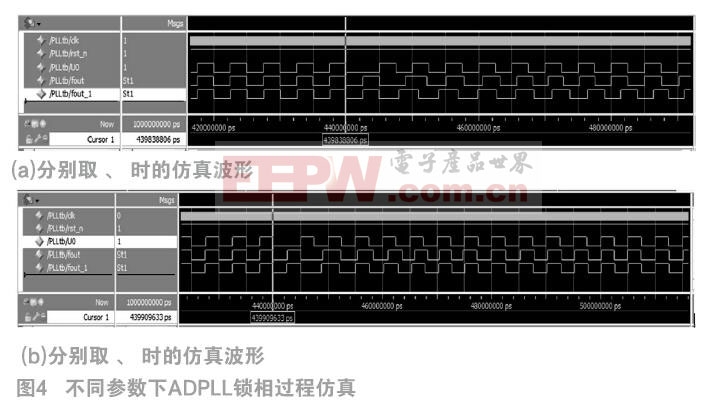

摘要:针对无线电能传输频率盯梢规划中传统锁相环电路规划杂乱、盯梢速度慢、锁相频带窄和无超前滞后环节,独自模块规划修正繁琐等问题,对自变模全数字锁相环进行改善, 与传统的全数字锁相环比较,该锁相环选用可变模分频器,使得中心频率可变,锁相规模增大;经过前馈回路进行鉴频调频,提高了锁相速度;一起,其环路滤波器选用份额积分结构,使得锁相输出无静差且份额积分参数依据相位差主动进行调理;经过参数设置可调理输出信号的相位。使用modelsim进行仿真,并进行什物验证证明了该规划具有宽规模的锁相才能及快速准确的频率盯梢功能。

导言

无线电能传输技能具有非常宽广的远景,是输电方法革命性的严重改动,将为人们灵敏自若、随时随地智能化用电带来巨大便利[1]。磁耦合谐振式无线电能传输体系作业过程中,外界导磁资料的影响、负载的不同、电路器材温度的升高级要素都会引起负载RLC谐振回路参数的改动,进而使高频逆变器的作业频率与负载固有谐振频率不一致,高频逆变器违背最佳作业点,导致电能的传输功率下降[2]。为了改善这种情况,需求高频逆变器的作业频率能够实时盯梢负载的固有谐振频率,锁相环(PLL)便是完成上述操控的重要器材。但是,现在厂家针对无线电能传输频率盯梢大多选用模仿锁相环,模仿锁相环存在着线路规划杂乱、开发周期长、盯梢速度慢、锁相频带窄等许多缺陷。

依据FPGA的数字锁相环具有抗干扰才能强、易于集成等许多长处,因而成为一种新的发展方向。但由于传统全数字锁相环(All Digital Phase Locked Loop)选用的是固定模分频器与份额结构的环路滤波器,因而,锁相速度慢,锁相规模窄,相位输出存在静差。而且,假如输入频率违背中心频率时,ADPLL的输出会存在较大稳态差错和显着的颤动。针对上述问题,单长虹等人提出了一种具有主动变模操控的快速全数字锁相环,有效地处理了捕捉速度和抗噪声功能之间的对立。庞浩等人提出了一种依据份额积分结构的全数字锁相环来消除静态差错,但上述改善都没有处理ADPLL功能受固定中心频率约束的问题。尤波提出的自变模操控全数字锁相环中心频率可变,份额系数可调,但无积分环节体系存在差错。盛臻提出的快速自适应锁相环一方面依据输入信号的频率以及鉴相差错的巨细两个方面进行实时调理,另一方面,当输入信号频率发生较大骤变时,经过对滤波器参数的初始置位,来改动环路的中心频率。但中心频率不是实时改动的,锁相速度遭到必定约束。

本文提出了一种依据FPGA的新式无线电能传输全数字锁相环,该锁相环选用可变模分频器,使得其间心频率可变,锁相规模增大;经过前馈回路进行鉴频调频,提高了锁相速度;一起,其环路滤波器选用份额积分结构,使得锁相输出无静差,输出颤动减小且份额积分系数依据相位差主动进行调理,一起经过参数设置可调理输出信号的相位。依据上述的研讨根底,经过modelsim软件仿真以及FPGA的实践硬件验证,证明了该规划方案的合理性和有效性。

1 ADPLL结构与作业原理

可变模ADPLL由鉴相器、环路滤波器、可变模分频器、自适应操控器、超前模块和滞后模块构成。ADPLL结构框图如图1所示,其间U0为输入信号,fout为输出信号,clk为体系时钟。

该ADPLL选用了双D鉴相器。鉴相器对输入和输出信号的相位进行比较,输出超前或滞后信号。环路滤波器模块具有份额积分调理作用,经过体系时钟clk,将鉴相器的输出调制为脉冲序列,份额环节对脉冲序列以参数1/Kp进行分频并计数,并将成果输出到加法器;积分环节同样是对脉冲序列以参数1/KI进行分频并计数,并将成果输出到加法器,但积分环节的成果不清零,然后消除了份额环节带来的稳态差错。为了约束积分环节的输出,积分环节需设置输出限幅。除N计数器对本地固定频率的高速时钟进行分频。其分频系数来自数字环路滤波器的N比特输出相位差错码。然后完成对输入信号相位的操控[3]。

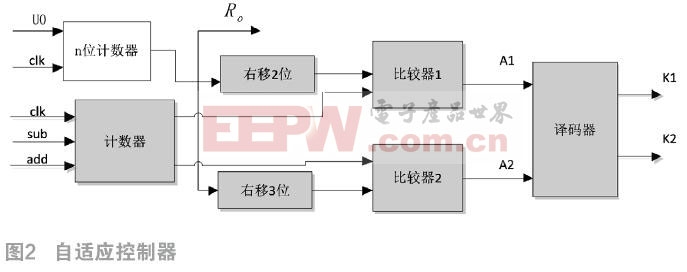

自适应操控模块是依据鉴相差错的相对巨细来进行作业的,它选用了两级比较的电路结构,如图2所示。选用体系时钟clk将输入信号U0调制成一系列脉冲,计数器核算并输出每个输入周期内体系时钟脉冲数目,近似表明了clk与输入信号频率之间的倍数联系。其间的比较器电路,将移位后的值与经高频时钟clk量化计数的相位差错巨细进行比较,并别离输出各自的比较值A1、A2;译码器电路依据A1和A2的值,生成数字环路滤波器的份额积分操控参数K1和K2[4]。

在无线电能传输频率盯梢电路中,电流采样,频率盯梢、MOSFET通断等都需求时刻,导致谐振电流和谐振电压相位不一致,高频谐振逆变器作业在容性状况,因而需求对逆变器进行谐振补偿,使逆变器作业在谐振状况。传统的补偿电路都是模仿器材,简单发生温漂,该文提出的全数字锁相环可进行相位调理。调理超前模块和滞后模块能够调理输出信号的相位。当输出信号稳守时,输出信号超前或滞后输入信号固定的时钟周期,其RTL级电路如图3所示。