AD9577相关信息来自ADI官网,详细参数以官网发布为准,AD9577供给信息可在查IC网查找相关供给商。

产品概况

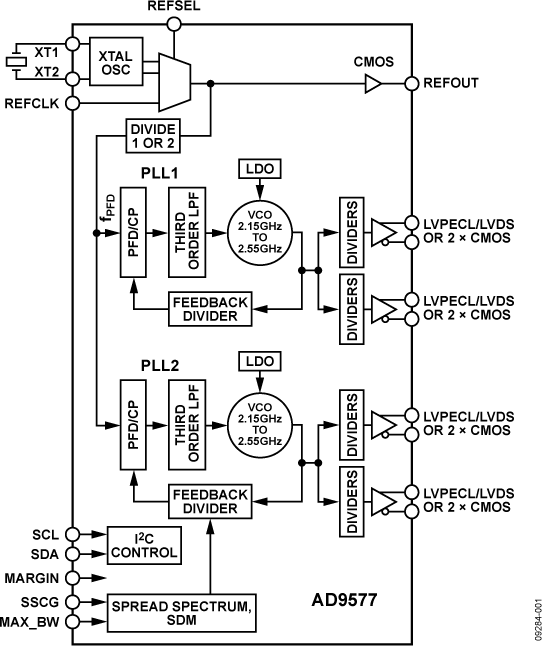

AD9577既供给一个多路输出时钟发生器功用,又带有两个片上锁相环内核PLL1和PLL2,专门针对网络时钟使用而优化。PLL规划根据ADI公司老练的高功用、低颤动频率组成器产品系列,保证完成最高的网络功用。PLL具有I2C 可编程输出频率和格局。小数N分频PLL可支撑扩频时钟功用,下降EMI辐射的峰值功率。两个PLL均可支撑频率余量微调功用。

第一个整数N分频PLL部分(PLL1)由一个鉴频鉴相器(PFD)、一个电荷泵(CP)、一个低噪声电压操控振荡器(VCO)、一个可编程反应分频器和两个独立可编程输出分频器组成。经过将外部晶振或基准时钟衔接至REFCLK引脚,可将最高达637.5 MHz的频率同步至输入基准。针对所需输出速率,每个输出分频器和反应分频器的比率可所以工厂设定或I2C 编程设定。

第二个小数N分频PLL(PLL2)内置一个可编程模块,可组成基准频率小数倍的VCO频率。针对所需输出速率(最高达637.5 MHz),每个输出分频器和反应分频器的比率能够经过工厂编程设定。这个小数N分频PLL还可在整数N分频形式下作业以充沛下降颤动。

最多四个差分输出时钟信号可装备成LVPECL或LVDS信号传输格局。每个输出对也可装备用于最多八个CMOS输出。支撑这类格局的组合。无需外部环路滤波器元件,然后节省了名贵的规划时刻和电路板空间。AD9577供给40引脚6 mm × 6 mm LFCSP封装,选用3.3 V单电源供电,作业温度规模为-40℃至+85°C。

使用

– 低颤动、低相位噪声多路输出时钟发生器,支撑多种数据通信使用,包含以太网、光纤、SONET、SDH、PCI-e、SATA、PTN、OTN、ADC/DAC和数字视频。

– 扩频时钟

优势和特色

- 彻底集成双路PLL/VCO内核

- 1个整数N分频和1个小数N分频PLL

- 接连频率规模:11.2 MHz至200 MHz

— 供给200 MHz至637.5 MHz的大多数频率 - PLL1相位颤动

(12 kHz至20 MHz):

460 fs rms(典型值) - PLL2相位颤动(12 kHz至20 MHz)

– 整数N分频形式:470 fs rms(典型值)

– 小数N分频形式:660 fs rms(典型值)

AD9577电路图

AD9577中文PDF下载地址

AD9577下载链接地址:https://www.analog.com/media/en/technical-documentation/data-sheets/AD9577.pdf