CPLD和FPGA都是咱们常常会用到的器材。有的说有装备芯片的是FPGA,没有的是CPLD;有的说逻辑资源多的是FPGA,少的是CPLD;有的直接就不做差异,把他们都叫做FPGA。那么两者到底有什么差异呢?下面咱们就以Altera公司的CPLD和FPGA为例来说说两者的差异。

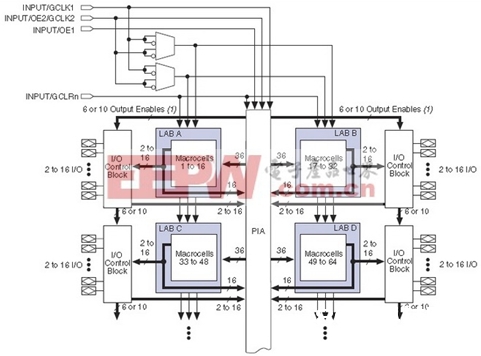

首要咱们看一下CPLD的芯片结构,搞清楚CPLD是由哪几部分组成的。下图是MAX系列CPLD的芯片结构图:

从图中可以清楚的看出来CPLD首要由三部分组成:Macro cell(宏单元),PIA(可编程连线),和IO Control Block(IO操控块)。每个宏单元都与GCLK(大局时钟)OE(输出使能)GCLR(清零)等操控信号直接相连,而且延时相同。各宏单元之间也由固定长度的金属线互连,这样确保逻辑电路的延时固定。其间宏单元模块是CPLD的逻辑功用完成单元,是器材的根本单元,咱们规划的逻辑电路便是由宏单元详细完成的。下面咱们再来看看宏单元的详细结构:

一个宏单元首要包含了LAB Local Array(逻辑阵列),Product-Term Select Matrix(乘积项挑选矩阵)和一个可编程D触发器组成。其间逻辑阵列的每一个交叉点都可以经过编程完成导通然后完成与逻辑,乘积项挑选矩阵可完成或逻辑。这两部分协同作业,就可以完成一个完好的组合逻辑。输出可以挑选经过D触发器,也可以对触发器进行旁路。经过这个结构可以发现,CPLD十分合适完成组合逻辑,再合作后边的触发器也可以完成必定的时序逻辑。