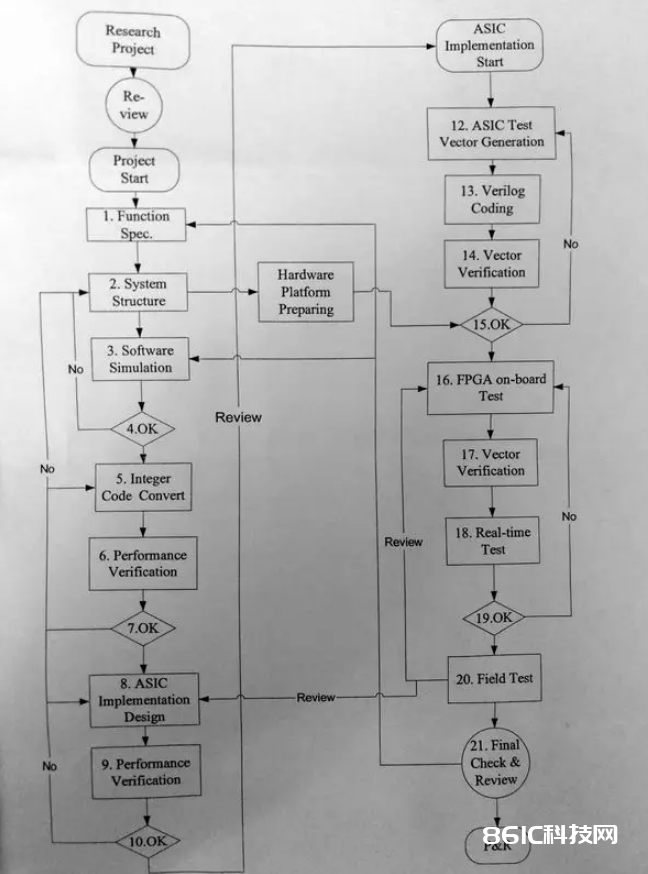

最近拾掇书架,翻出一张多年曾经的ASIC项目开发流程图,一同回忆一下。典型的瀑布式开发流程:

以算法规划为主导

算法C代码手艺转换为RTL

RTL与算法C代码生成的测验向量比照进行验证

依靠FPGA做许多实时、现场测验

合适通讯信号处理,音视频处理产品

1. 算法预研

承认了产品方向之后,算法工程师开端进行调研。

要学习研讨行业界最新的研讨成果、论文,提出创造性的方法来取得最好的功用。要运用实在的测验数据和仿真成果进行评价。终究交给为算法描绘的C言语源码。

算法调研完毕后需求进行审阅(review):承认算法功用,承认体系架构规划,承认是否能够正式立项。审阅进程需求算法规划、RTL规划、软件、硬件体系、商场、管理层一起参加。

正式立项时,需求供给功用spec,以及算法C代码功用仿真环境。与此同时,硬件组需求依据项目需求开端建立硬件FPGA测验渠道。

2. 算法优化

接下来进行算法的优化,首要考虑以下几个方面:

算法复杂度

算法运算量

变量精度

算法规划以及状态机操控要具有自恢复才能

算法代码要满足stable,关于各种滤波器系数和变量要有必定的噪声容忍度。

算法终究承认需求经过审阅:算法架构,算法功用仿真,算法定点化和功用验证。

3. 面向ASIC的C代码完结

在此阶段,算法C仿真代码改变为模块结构代码,分解为若干ASIC功用模块,代码的接口与RTL接口挨近:

简略完结

高效率

节约逻辑

重用现有模块

对带有反应的模块中添加仿真延时

在接口添加仿真延时

终究的C代码中:

主函数只包含衔接联系和子模块

一切子模块以各自的时钟速率调用

接口选用cycle based timing

需求预备以下review和文档:

ASIC模块和接口规划辅导

功用验证陈述

接口变量的时序图和精度描绘

4. C到RTL的完结

RTL规划工程师完结从C代码到verilog的完结。算法工程师担任发生相应的测验向量,包含子模块测验和体系联调测验。要运用各种典型的测验场景数据,以及一些子模块等级的随机测验数据。

依据RTL规划以及归纳成果,能够取得整个体系的时序信息,gate count和die size预估。

5. FPGA on-board test

因为RTL仿真的速度较慢,能够凭借FPGA来进行测验加快。硬件工程师预备FPGA渠道,FPGA工程师进行RTL到FPGA的代码移植,软件工程师帮忙相关测验软件的开发与运用。

在FPGA上能够做到与RTL仿真相同的作用,比方从内存中供给输入,并抓取输出成果,与算法C发生的数据进行比对。需求测验尽可能多的测验用例。

6. FPGA field test

假如项目代码能够在FPGA上跑到与实在运用相同的速度(full

speed),就能够用FPGA代码直接做实时现场测验。在现场测验的任何问题,需求反应给算法组进行剖析处理。

7. Final Check and Review

现场测验经过后,需求做最终的查看和review悉数代码,然后开端芯片后端规划。

站在今日(2018年)的视点看过去上述流程有存在一些问题:

选用算法C到Cycle C再到RTL完结的流程,迭代长,易犯错

RTL验证以直接定向测验为主,短少随机验证,覆盖率不行

依靠FPGA实时测验作为验证首要手法,FPGA渠道开发需求专门的人力资源和硬件渠道,并且FPGA渠道不行灵敏,且简略呈现不稳定的问题。

现在已经有许多新技术能够学习,比方

根据High level synthesis,缩短开发周期

选用各种验证方法学,进步验证覆盖率

运用专用的硬件加快器渠道

最终,以上开发流程简略,出资少,关于算法(大牛)主导的创业型公司,或许以IP开发为主的小型团队,仍是能够运用的。