用户需求更小更廉价的手机,在手持设备中得到快速服务和更多功用。这正在促进业界加快立异处理计划,下降本钱使产品赶快上市。这种外加压力,使制作商重新考虑处理这些问题的技能。

硅技能和集成要害元件单元(如RF 收发器 )能下降产品尺度和本钱。

)能下降产品尺度和本钱。

蜂窝规范(如GSM)的严厉功用要求,曾经约束了RF收发器 集成,迫使选用替代技能(如SiGe BiCMOS或双极)。现在,GSM/GPRS CMOS收发器

集成,迫使选用替代技能(如SiGe BiCMOS或双极)。现在,GSM/GPRS CMOS收发器 普及率添加,使挑选CMOS RF技能添加了老练性。

普及率添加,使挑选CMOS RF技能添加了老练性。

虽然CMOS RF收发器 规划供给有力的、使人服气的长处,但规划工程师在开发手持WCDMA、EDGE、GPRS/GSM规范高集成度多模收发器

规划供给有力的、使人服气的长处,但规划工程师在开发手持WCDMA、EDGE、GPRS/GSM规范高集成度多模收发器 时,有必要战胜结构和电路规划问题。投入时刻和精力选用CMOS开发多模使用的RF收发器是值得的,商场的答复也是必定的。

时,有必要战胜结构和电路规划问题。投入时刻和精力选用CMOS开发多模使用的RF收发器是值得的,商场的答复也是必定的。

多模发展趋势

为使全球经营者包容不同的蜂窝架构,手机制作商把多种无线蜂窝技能 (多模)结合在一个器材中,为特别商场供给最好的买点计划。例如,商场上支撑EDGE的手机数添加,具有向后与GSM/GPRS服务兼容。相同,未来3G手机除EDGE/GPRS/GSM技能外,将支撑WCDMA。全球周游需求5个频段:GSM-850MHz,E-GSM-900MHz,DCS-1800MHz,PCS-1900MHz和UMTS-2100MHz。手机规划师有必要考虑所有这些要求,并满意用户对低本钱和形状因数产品的要求。

硅集成和模块集成促进多模功用。大多数的多模渠道组合独立的无线子体系,例如,支撑GSM/GPRS和WCDMA的多模电话可具有一个带GSM/GPRS收发器WCDMA收发器,以及RF前端和无源元件单元,以便支撑两个形式和频段(见图1)。这种办法最有用,由于GSM/GPRS和WCDMA信道位率是依据不同基准时钟频率(分别为13MHz/26MHz和19.2MHz)。一般的GSM/GPRS发送器结构(如OPLL)不能直接加到WCDMA。在该实例中,下降多模规划元件数和本钱,需求较高的集成度和立异的RF技能。

图1 选用别离3G和2G无线技能的典型3G多模/多频段 RF规划

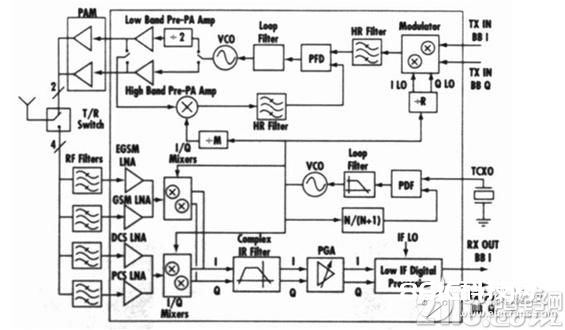

图2 单片4频段GSM/GPRS CMOS收发器框图

多RF前端体系集成计划

4频段GSM/GPRS体系的RF前端规划计划示于图2,用一个高集成度单片CMOS收发器。天线开关模块连接到发送和接纳通路,对每个GSM频段用接纳器SAW滤波器和相关的匹配电路。发送通路至少需求两个PA:一个PA用于GSM-850MHz和E-GSM-900MHz频段,第2个PA用于1.8GHz DCS和1.9GHz频段。

许多可用的集成RF前端模块可下降元件数并简化规划。它们包括带动率扩展器和功率操控逻辑功用(PA模块)的模块和带PA及开关功用发送模块 。在接纳端,由SAW滤波器单元和带多路开关和接纳滤波器的RF前端模块组成。

与图2中的GSM/GPRS体系比较,图1 3G多模体系的更杂乱前端规划支撑2.5G和3G RF信号传输。添加多路转化器是有必要的,由于WCDMA是依据频分双工,发送器和接纳器是一同开关转化。但是,像GSM/GPRS那样,经济定标将带来前端元件集成。

当今蜂窝基站结构分红两种:基带功用分红别离模仿和数字基带芯片或单片高集成CMOS SoC器材(包括完成形式和数字功用)。由于,每种办法具有天壤之别的长处,所以在两种分配办法之间进行挑选,取决于为大多数经济渠道计划挑选未来集成路途等要素。

虽然单片办法节约PCB真实的面积,但用别离的模仿和数字基带芯片,关于集成是最可取的路途,由于它使模仿基带功用与完成数字基带的“纯”数字电路阻隔。两片计划也能使数字基带定标更小的CMOS几许尺度,一同集成其CMOS渠道元件(如使用处理器,图画处理器,存储器)

基带结构的一种趋势是简略地去掉模仿基带芯片,所以使数字基带功用集成最佳,一同简化无线到基带芯片接口规划。此办法在无线和数字基带之间,选用一个高速数字接口。能够规则此接口为串行或并行。串行接口下降了器材引脚数,但添加了高速缓冲器芯片上的晶体管数。并行接口添加引脚数和封装尺度,但在硅中可更有效地完成。

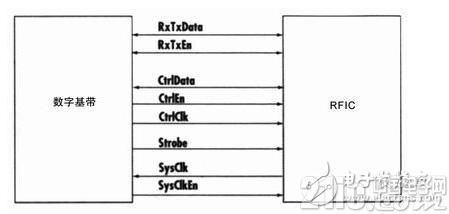

现在,DigRF Standards Body 为2.5G规则了规范高速串行接口规范(见图3)。当支撑数字接口时,无线规划将添加杂乱性。它不只是有必要履行模仿到数字和数字到模仿的转化,并且有必要有接口逻辑来处理基带的数字通信。用CMOS工艺技能比其他工艺更简单、更经济地完成这些功用。

图3 无线和数字基带之间的2G DigRF接口

图4 单片4频段CMOS收发器框图

CMOS长处

用CMOS技能完成收发器有下列长处:

CMOS与SiGe BiCMOS工艺比较,在持平的工艺尺度具有更低晶片本钱结构。

CMOS答使用规范工艺在多个厂家进行芯片制作。

依据Moore规律,CMOS规划能够定标更小工艺尺度。

CMOS能够完成RF功用数字电路,导致高度可编程规划,使其具有小的芯片、高度可制作性,杰出的巩固性。

CMOS收发器能够集成其他功用(如DigRF接口或数字基带功用),然后构成单片RF和基带元件。

CMOS已证明是完成收发器的一种技能,厂家已生产出许多GSM/GPRS、WLAN和蓝牙无线电。

多模GSM/GPRS/EDGE/WCDMA手机选用收发器结构,是一个要害决议。现在,在许多单片CMOS GSM/GPRS收发器中,一般集成VCO、频率组成器、环路滤波器和DCXO,这种集成特别重要。高集成有助于确保杰出的无线功用,这是由于要害功用与外部噪声源屏蔽。

在稳定起伏的GSM/GPRS 阻断器和调幅EDGE或WCDMA阻断器中的接纳器,有必要供给杰出的起伏调制按捺功用。与传统超外差规划比较,最盛行的接纳器结构是低中频或零中频,其间所规划的接纳器和发送器链路不需求外部IF SAW滤波器。

直接变频接纳器,直接改换输入信号为低频信号,便于完成可编程滤波器。直接变频无线电的一个问题是由大阻断器的本地振动器自混频引起DC偏移呈现,因而恶化下变频信号。处理此问题往往需求基带履行DC偏移校对,一般是经过软件来完成。在低中频接纳器中,经过混频和滤波从所期望的下变频信号中去掉DC偏移。此外,低中频规划一般具有集成组成器、环路滤波器和调谐元件来避免外部相位噪声源引起的彼此混频。

关于发送器,线性上变频结构往往最适合于GSM/GPRS、EDGE、CDMA和WCDMA,而极性环路规划首要用于EDGE收发器。线性上变频结构在贯穿发送器链路中(从其带I和Q信号到天线)坚持线性。依据极性环路或极性调制的无线电靠献身附加定标和所需功率操控反应环路杂乱性来供给附加的高功率功率。此外,极性发送器需求一个特别定制的PA,来确保起伏准确匹配和相位推迟。线性发送器不像极性发送器那样,它能够广泛地选用现有PA元件。

单片4频段GSM/GPRS规划

为了成功地开发一款支撑3G和2G服务多模CMOS无线电,收发器IC公司在力求用其他形式组合(如EDGE和WCDMA)规划器材前,有必要证明它有才能为GSM/GPRS使用开发和制作单片多频段CMOS收发器。

图4示出一个4频段GSM/GPRS CMOS收发器规划。4频段接纳器用低中频结构替代零中频,因低中频受1/f噪声、DC偏移和有限接纳器IIP2的影响较小。用片上电感负反应的全差分共源扩展器完成LNA,用于阻抗匹配和增益峰值。LNA也履行低增益形式。

LNA之后,正交混频器下变频所期望的RF为低中频。接纳器的低中频部分由5阶杂乱Butterworth滤波器和PGA组成。每个杂乱滤波器级为GSM阻断器和图画信号供给按捺,并供给所期望信号的可编程扩展。增益散布和滤波器极的定序使总Rx SNR最大。可编程增益IF滤波器与LNA增益结合在一同具100dB可编程增益。DCOC电路避免IF增益级饱满。滤波器I和Q通道之间电阻交叉耦合导致I信道上DC偏移影响Q信道,反之亦然。杂乱滤波器之后,低中频解调电路下变频IF I和Q信号为基带频率(用数字组成时钟)。

发送器结构是依据OPLL基础上的,它包括一个正交调制器和一个彻底集成的低相位噪声RF VCO。由正交调制器把基带I和Q GMSK信号变为IF。一个5阶Gm-C低通滤波器可消除不期望的频率重量。用片上环路滤波器滤波PFD输出,此输出用于驱动RF VCO ,RF VCO含盖GSM-850、GSM-900、DCS-1800和PCS-1900频段。

VCO输出驱动片上发送缓冲器。此缓冲器的RF输出电平可编程到习惯不同的PA模块。单端输出不需求外部平衡—不平衡转化器。片上VCO相位噪声和TX前置PA驱动器噪声一同决议接纳频段的TX输出噪声(这是GSM发送器的最严厉功用指标之一)。为使噪音减小、DC电流耗电削减,从VCO输出到前置PA驱动器,输入坚持在轨到轨信号或后置PA发送带通滤波器,因而,改进了发送器功率功率。

用单频率组成器为发送器和接纳器发生本地振动信号,以此使用GSM的时分双工特性。用3阶△ΣN分组成器来为Tx和Rx形式频率规划供给最大灵活性。用带片上电感器的VCO,来满意Rx和Tx相位噪声所要求的容限。

结语

扩展数字范畴的规划杂乱性,发挥高密度CMOS逻辑的有效性。完成杰出的结构(包括延伸的DSP技能和共用功用单元),是成功和经济规划的最基本要素。

靠处理完成单片4波段GSM/GPRS CMOS收发器问题,RF集成电路规划师能够处理支撑EDGE、WCDMA和其他无线技能的单片无线电开发问题。把高集成前端模块和数字接口基带IC结合在一同,所得到的CMOS收发器能够完成经济、小形状因数多模手机。