作者 / 田元锁1,2 张拂晓1,2 1.我国电子科技集团公司第四十一研讨所(安徽 蚌埠 233000) 2.电子信息丈量技能安徽省要点试验室(安徽 蚌埠 233000)

*基金项目:国家科技严重专项(编号:2016ZX03002002)

田元锁(1983),男,硕士,工程师,研讨方向:移动通讯测验。

摘要:5G试点工作发展顺畅,估计2020年正式商用,峰值速率将到达每秒10 Gb,针对5G新技能,数据传输技能已成为限制体系计划完结的要害因素,提出的高速数据传输技能,选用高功用FPGA、高位宽、高采样率的AD和DA,进行相关接口优化,验证了5Gbps光纤数据传输,为后续5G通讯供给很好的参阅测验、验证。

0 导言

移动通讯网络技能经过多年爆发式增加,阅历了2G、3G 和4G,每一代都有一个十年的展开周期[1]。工信部表明2017年5G技能研制进入第二阶段,现在已经在3.4~3.6 GHz频段展开5G体系技能研制试验。相关的5G通讯测验仪器仪表有必要具有很高的传输才干和核算才干来处理数据传输。

与传统移动通讯技能不同的是,5G的天线增强、波束成型和3D-MIMO等技能带来更大的困难是设备体积越来越小、集成度越来越高。仪器仪表产业链怎么加大技能创新应对这些新的应战,是5G商用发展的要害。测验仪器仪表硬件功用目标,成为限制其信息处理才干的要害因素,跟着元器件功用的不断提高,关于仪器仪表也带来了质的腾跃,所以功用目标的凹凸决议了仪器仪表的中心处理才干 [2-5],本文选用高功用FPGA、高采样率的AD和DA,进行了相关接口优化,验证了5 Gbps光纤数据传输。

1 5G通讯高速数据传输体系

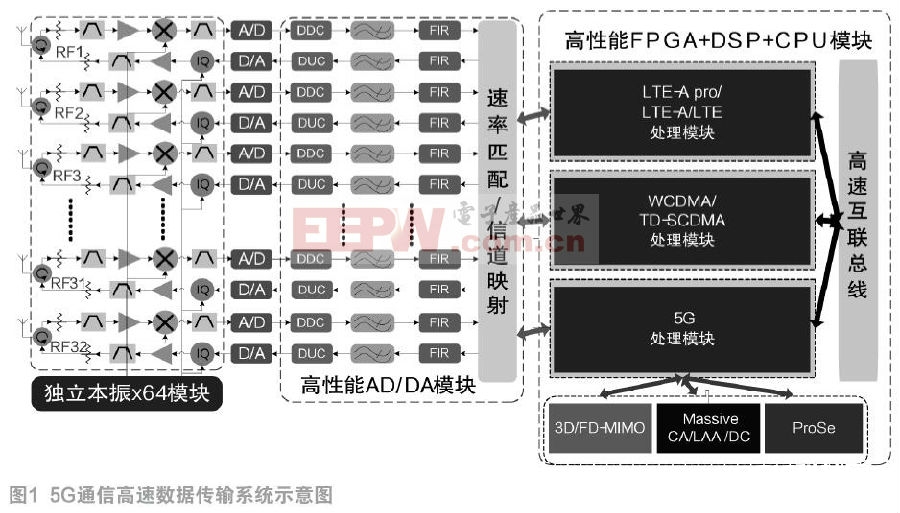

1.1 高速数据传输体系硬件构成

数据传输体系受制于其硬件处理才干[6-9],5G通讯高速数据传输体系硬件渠道首要由独立本振模块、高功用AD/DA模块、高功用FPGA+DSP+CPU模块等组成。图1为5G通讯高速数据传输体系体系框图,规划选用模块化规划办法,在共同硬件与软件渠道上完结和满意不同的测验,单机能支撑现在5G通讯测验,也能够向下兼容多种通讯制式测验,研讨具有稳定性高、共同性好、可扩展性强等特色的高速数据传输体系。

该体系的难点在于:

1)在大带宽情况下怎么确保信号的频率呼应、群时延特性和带外按捺规划目标;

2)将中频信号无差别的解调为IQ数据流准确的规划完结;

3)5G通讯的带宽要求更高的中频以及采样速率,怎么确保在高速采样下的目标和可靠性将是规划的又一应战。

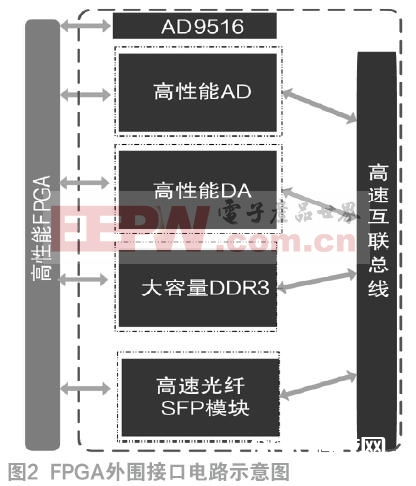

FPGA外围电路接口如图2所示,加载模块、DDR、电源、时钟模块、光纤模块等,时钟模块由AD9516供给,为了坚持信号时钟与本地时钟共同。FPGA用的是Xilinx公司的XC7VX690T,该芯片GTH最高支撑13.1 Gb/s,满意GPRI接口中的9.830 G、6.144 G、3.072 G等速率要求。

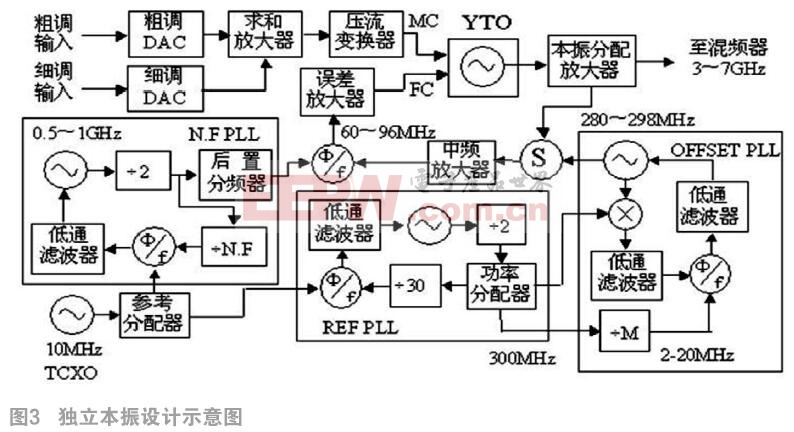

1.2 独立本振规划

本振规划最首要、最困难的是宽带高功用榜首本振规划,整机的相噪目标首要取决于榜首本振。一般以为,只要在变频时不恶化接纳到的通讯信号矢量解调目标,就能满意测验需求,一般只需求榜首本振的相噪优于-90 dBc/Hz@10 kHz,而关于本体系,由于需求剖析多通道信号赋形增益和天线矢量图,所以对相位和时延有严格要求,一起,5G通讯有新标准、新技能计划,对射频通路的信号质量也提出了高相噪要求,所以用于变频的榜首本振信号的相噪就需求很高的相噪目标,才干不带来额定的测验差错和不确定性,所以本体系要求-133 dBc/Hz@10 kHz的超高相噪目标。

本模块规划首要难点是高目标的射频模块规划和微波滤波器规划,射频模块的频率规模在400 MHz~6 GHz内改变,兼容现在5G测验频段,本规划兼容其他通讯制式,为了不影响OFDMA/SC-FDMA信号的质量及IEEE 802.11 a/b/g/n/ac测验的要求,射频信号带宽将大于160 MHz,带内平整度小0.5 dB。高速传输体系收发处理模块如图3所示。

2 高速数据传输的完结

2.1 高速数据接纳通道规划

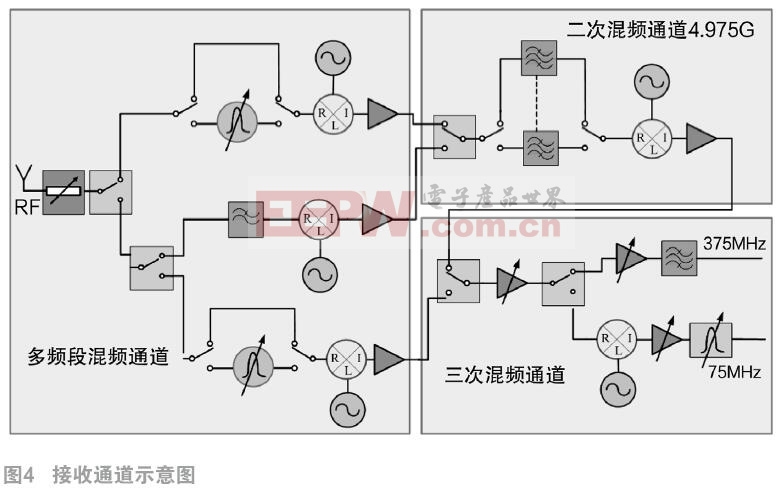

高速数据接纳通道的首要功用是将频率规模在400 MHz~6 GHz的射频信号下变频到适宜的固定中频频率上,以供宽带中频处理模块和信号剖析模块处理。其详细计划如图4所示。射频信号输入首要前置低噪声放大器,提高小信号接纳灵敏度,然后经过一个程控步进衰减器,该衰减器首要功用是可根据信号电平调理衰减量,确保满意后端电路处理要求。这以后,信号经过一个低通滤波器,滤除丈量频率规模以外的搅扰信号,避免引起假呼应。滤波后的信号进入榜首混频器,这儿选用了高中频的上变频计划,可有用处理镜像、走漏等问题,混频后发生榜首中频。相应的榜首本振需求供给宽带高本振信号,该本振信号经过锁相环与10 MHz频率参阅鉴相完结确定。混频后的信号经过一个带通滤波器,滤除混频器发生的其他杂散信号,一起考虑到需求处理的带宽大于160 MHz,其1 dB带宽设定为320 MHz。经过带通滤波器后的信号进入第二混频器,与固定本振频率信号混频,将榜首中频信号下变频到第二中频低中频频率上,经过相关的滤波处理后,再经过一系列杂散按捺、起伏补偿和端口匹配后,输送给信号剖析模块。

射频信号输入首要前置低噪声放大器,提高小信号接纳灵敏度,然后经过一个程控步进衰减器,该衰减器首要功用是可根据信号电平调理衰减量,确保满意后端电路处理要求。这以后,信号经过一个低通滤波器,滤除丈量频率规模以外的搅扰信号,避免引起假呼应。滤波后的信号进入榜首混频器,这儿选用了高中频的上变频计划,可有用处理镜像、走漏等问题,混频后发生榜首中频。相应的榜首本振需求供给宽带高本振信号,该本振信号经过锁相环与10 MHz频率参阅鉴相完结确定。混频后的信号经过一个带通滤波器,滤除混频器发生的其他杂散信号,一起考虑到需求处理的带宽大于160 MHz,其1 dB带宽设定为320 MHz。经过带通滤波器后的信号进入第二混频器,与固定本振频率信号混频,将榜首中频信号下变频到第二中频低中频频率上,经过相关的滤波处理后,再经过一系列杂散按捺、起伏补偿和端口匹配后,输送给信号剖析模块。

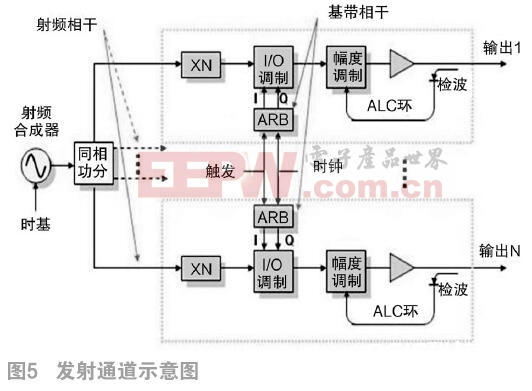

2.2 高速数据发射通道规划

高速数据发射通道的首要功用是由基带发生器模块为当时要完结的调制类型供给相应格局的基带信号,然后送给RF源的调制电路,发生载波400 MHz~6 GHz的OFDMA数字调制信号。

LTE-Advanced下行链路选用OFDM多址方法完结。OFDM技能以子载波为单位进行频率资源的分配,R12版别中载波聚合技能,能够经过聚合多个20 MHz的单元载波完结高达100 MHz的体系带宽。

本文经过MAC会聚来完结最多载波数目的聚合功用,详细完结方法是在高速FPGA处理单元中选用优化的DDC/DUC算法,将各载波的频谱搬移到适宜的方位,然后再进行后续的处理,如图5所示。

射频合成器模块发生400 MHz~6 GHz的载波信号,然后同相功分红多路,确保MIMO 8×4信号同相处理,后送给IQ调制器的LO端口。一起中频基带模块的输出信号送给调制器的基带信号输入端口;调制器输出RF端口为400 MHz~6 GHz的下行调制信号,该信号再经过多波段射频滤波器组和数字稳幅电路,终究传送至天线。因而,宽带IQ调制器完结400 MHz~6 GHz信号调制,功率规模-140~15 dBm的射频调制信号输出。

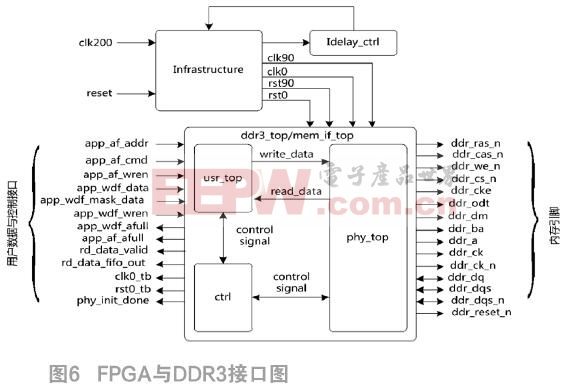

3 DDR3接口优化

大容量的DDR3关于高速数据处理来说,必不可少,为了更好的便于FPGA与DDR3之间数据传输,关于它们之间的接口进行了相关优化,其接口示意图如图6所示。

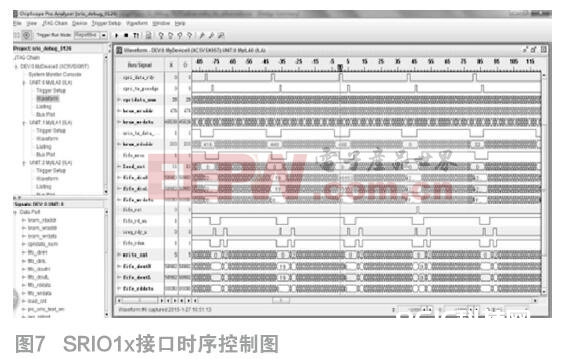

4 相关试验成果

5G通讯高速数据传输测验模块基带收发1 x协议形式与4 x协议形式接口时序图如图7、图8所示。

5 定论

本文完结了5G通讯高速数据传输,经过SRIO1x和SRIO4x接口时序数据成果,得知,选用高功用FPGA、高位宽、高采样率的AD和DA,完结高速数据传输是可行的,特别关于现在5G通讯,为后续5G通讯供给很好的参阅测验、验证。

参阅文献:

[1]余莉,张治中,程方,等.第五代移动通讯网络体系架构及其要害技能[J].重庆邮电大学学报(自然科学版),2004,04:427-433.

[2]唐礼红.5 Gbps高速串行接口电路的研讨与规划[D].国防科学技能大学,2009.

[3]陈陪陪.高速PLL的研讨与规划[D].电子科技大学,2016.

[4]姜漫.10Gpbs/40Gpbs光纤通讯技能研讨与体系完结[D].我国科学院大学,2012.

[5]任柯.高速光纤数据传输线要害技能研讨[D].电子科技大学,2012.

[6]史霏霏.应用于光纤通讯的高速接口的建模与研讨[D].电子科技大学,2014.

[7]莫建强.高速数字电路中的信号完整性剖析[J].电子测验,2011,09:(09)5-9.

[8]王巍.根据FPGA的高速串行数据传输的规划与完结[D].天津工业大学,2016.

[9]李正军,周志权,赵占锋.根据FPGA的高速数据传输体系规划与完结[J].核算机丈量与操控,2016,26(9):188-194.

本文来源于《电子产品世界》2018年第3期第33页,欢迎您写论文时引证,并注明出处。