数字波束构成技能充分运用阵列天线所获取的空间信息,经过信号处理技能使波束获得超分辨率和低副瓣的功用,完结了波束的扫描、方针的盯梢以及空间搅扰信号的零陷,因此数字波束构成技能在雷达信号处理、通讯信号处理以及电子对抗体系中得到了广泛的运用。数字波束构成是把阵列天线输出的信号进行AD采样数字化后送到数字波束构成器的处理单元,完结对各路信号的复加权处理,构成所需的波束信号。只需信号处理的速度足够快,就能够发生不同指向的波束。由于数字波束构成一般是经过DSP或FPGA用软件完结的,所以具有很高的灵活性和可扩展性。本文首要介绍了一个自适应波束构成器的原理及其完结办法,结合当今最先进的可编程芯片,包含数字信号处理器(DSP),现场可编程逻辑门阵列(FPGA)完结了数字波束构成,适用于如3坐标雷达体系等杂乱阵列信号处理体系。其研发作用已运用在多部相控阵雷达中,缩小了我国在这个范畴与其他国家之间的距离,具有重要的经济含义和军事含义。

1 数字波束构成体系的根本结构

选用数字办法对阵元接纳信号加权处理构成天线波束,阵列天线阵元的方向图是全方向的,阵列的输出经过加权求和后,将阵列接纳的方向增益集合在一个方向上,相当于构成了一个波束,这便是数字波束构成的物理含义。数字波束构成器一般由两个首要部分组成,一部分是以数字信号处理器和自适应算法为中心的最优(次优)权值发生网络,另一部分是以动态自适应加权网络构成的自适应波束构成网络。波束构成算法是波束构成的中心和理论基础,他经过接纳的信号和一些先验常识核算出加权因子,然后再对输入的信号在波束构成网络中进行加权处理完结波束构成。

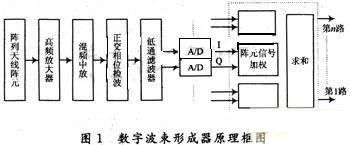

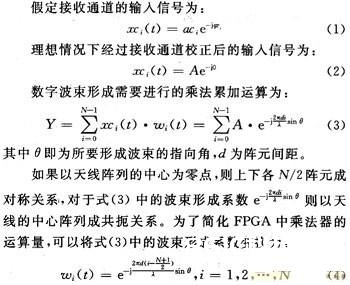

当进行多波束构成时,体系根本构成如图1所示。阵列天线每个阵元收到的信号经过混频、中放和正交相位检波,变为正交视频信号I和Q重量,再别离经由AD变换器转变为数字量I和Q,将数字信号送入波束构成运算器,别离与N组权值进行复数乘法运算,即得到所需的N个波束通道的信号。数字波束构成运算器由FPGA经过编程完结,首要进行权值的存储和把各路波束所需的权值信息存储于FPGA内部的存储模块中,经过进行乘加运算,来完结多波束的发生。

本文选用Altera公司的STRATIX器材,及其仿真软件QuartusⅡ4.1,运用VHDL言语与Altera的megafun-citions模块化函数库相结合编程规划来完结数字多波束构成器。文中举例所用的天线阵为N阵元等距线阵,在数字波束构成部分要完结十路数字波束构成。

2 依据FPGA和ADSP器材的数字波束构成器的完结

2.1硬件组成

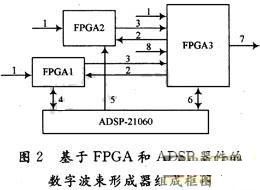

数字波束构成器由3片FPGA和1片ADSP-21060器材来完结,其间榜首片和第二片FPGA完结输入接纳通道的校对以及复数乘法累加运算并终究构成十个波束;第三片FPGA完结整个体系的的时序和形式操控并将前两片FPGA运算的成果组成后输出,需求时副瓣抵消的运算也在这一片完结。ADSP-21060器材首要完结接纳通道校对系数和波束构成系数的实时核算,需求时进行副瓣抵消系数的核算和发射通道校对运算。体系组成框图如图2所示。

其间总线上的标号解说如下:

1:输入的多通道A/D中频采样后的数字信号;

2:第三片FPGA传输操控信号给前两片FPGA;

3:前两片FPGA乘法累加运算成果输出到第三片FPGA;

4,5,6:ADSP-21060与FPGA的数据总线;

7:数字波束构成器的终究输出数据;

8:外部输入的形式操控信号。

为了让硬件渠道具有很强的通用性,关于FPGA器材,选用了Altera公司含有大容量片内RAM和硬件乘法器的Stratix系列的EPlS60芯片,该芯片有18个硬件乘法器模块,内部存储空间到达5 215 kb,逻辑单元数到达了57 120 les,彻底能满意此波束构成器的完结,并能运用冗余空间放置其他运算单元和操控模块,根本完结了体系的集成化模块化规划。且此器材的运算频率彻底满意需求,片内很多的剩下资源空间能够提供给后续部分的运用。

终究3片FPGA芯片的资源占用状况别离为:关于FPGAl芯片,编译后的资源为占用18个硬件乘法单元,占用1 680 kb/s片内存储空间,占用逻辑资源16 791 les;关于FPGA2芯片,编译后的资源为占用18个硬件乘法单元,占用1 680 kb片内存储空间,占用逻辑资源15 608 les;关于FPGA3芯片,编译后的资源占用为占用0个硬件乘法单元,占用103 kb片内存储空间,占用逻辑资源7 599 les。由以上详细数据可见,关于FPGA1和FPGA2芯片,由于需求做很多的乘法累加运算,芯片的硬件乘法单元已悉数占用,但片内存储空间只占用了32%,逻辑单元最多也只占用了不到30%。

2.2 作业进程

数字波束构成器由3片FPGA和1片ADSP-21060器材来完结功用,其间FPGA器材首要完结输入输出数据的缓存以及很多的乘法累加运算并发生或传输所需的各种时序和操控信号,ADSP-21060器材首要完结所需各种系数的实时核算。下面别离加以详细阐明。

2.2.1 FPGA的作业进程

这样能够运用波束构成系数的共扼联系,将本来占一半数据量的复数乘法运算变为加减运算,大大降低了乘法器的运用量。

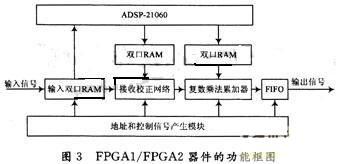

FPGA1和FPGA2器材根本功用相同,他由存储器模块、接纳校对网络、复数乘法累加器、地址和操控信号发生模块以及输出FIFO等几个模块完结。多路中频回波I,Q信号进入FPGA器材后首先进入双口RAM暂存,若当时作业在接纳校对形式,则ADSP-21060器材会从此双口RAM中读取数据以核算接纳校对系数,若作业在正常形式,则FPGA会自己发生地址和操控信号,将此双口RAM中的数据读出进入接纳校对网络,一起进入此网络的还有ADSP-21060器材核算出的接纳校对系数,在这个网络中完结接纳通道的校对后数据进入主乘法器,即复数乘法累加器,这一步运算需求用到波束构成系数,这个系数仍然是由ADSP-21060器材实时核算出并放在FPGA中相应的双口RAM里,经过地址和操控信号发生模块能够将从双口RAM中读出的数据和接纳校对网络输出的数据在乘法累加器前级进行路数和距离单元的对齐。复数乘法累加器的输出终究进入FIFO在时刻和距离上进行重排,终究输出到FPGA3。FPGA1/FPGA2器材的功用框图如图3所示。

关于FPGA3器材,首要完结操控、时序和数据信号的传输、波束乘累成果数据的组成、副瓣抵消的运算以及发射通道校对的进数和送数等功用。前两片FPGA乘累成果进入FPGA给3后依照距离单元进行组成,然后进入副瓣抵消模块。副瓣抵消时由21060实时核算出抵消系数送进FPGA3的副瓣抵消模块,一起抵消通道的数据也进入此模块与系数进行乘累操作,乘累成果再与组成后的波束构成成果进行副瓣抵消运算,成果直接输出下一级信号处理单元。发射通道校对时,发射通道的数据先进入FPGA3的RAM中暂存,由ADSP-21060器材取出进行相应处理,并将解算出的发射通道起伏和相位信息送回FPGA3对应的RAM中,再由FPGA3输出到相应体系进行后续操作。一起FPGA3还接纳输入的操控指令,并将一切操控指令分化后按不同需求别离送给FPGA1,FPGA2和ADSP-21060器材以操控一切器材的正常作业。

2.2.2 ADSP的作业进程

在这个数字波束构成器中,ADSP-21060器材首要完结以下功用:接纳通道校对时40路校对数据的进数以及对进数进行运算处理以得到接纳通道校对的系数并将此系数输出到FPGA1和FPGA2中;发射通道校对时1路校对数据的进数以及对进数进行运算处理以解算出每行发射机对应的起伏和相位数据并将此数据输出到FPGA3中;依据当时作业形式和作业频率实时核算出波束构成系数并输出到FPGA1和FPGA2以参加运算;副瓣抵消时完结抵消通道的进数并运用此数据和主通道数据实时核算出副瓣抵消系数,将此系数输出到FPGA3以进行副瓣抵消的运算。

DSP程序上电初始化今后就等候同步中止,进入同步中止服务子程序里取作业形式操控字并对各种寄存器和标志位进行相应赋值。在Tr中止到来后判别当时的作业形式,假如当时作业在接纳校对形式则开端从FPGA中的RAM取数,取数完结后进行接纳校对的相应运算,在运算完结后将接纳校对系数以DMA方法输出给FPGA;假如当时不是校对形式,则依据频率点和作业形式代码开端实时核算波束构成系数并将此系数经过DMA传输方法输出给FPGA参加乘法累加的运算。这些都完结后再判别当时是否需求做副瓣抵消,假如需求的话,再从第三片FPGA中取出抵消通道以及主通道的数据,运用这些数据实时核算副瓣抵消系数,并将此系数输出给FPGA3以进行副瓣抵消的运算。至此ADSP-21060器材的首要功用现已完结,程序重又回到等候同步中止状况。

2.3 测验成果

本文介绍的数字波束构成器已成功运用于多部雷达并获得很好的作用。下面给出几个前期测验的数据图表。图4,图5为在两个不同作业频率下,接纳通道校对后由天线接纳的扫角信号经过波束构成后按-39 dB加权在某一个波束输出的成果。图中横坐标为扫角信号视点距离,满刻度为0°~60°;纵坐标为分贝数。由图可见,最大副瓣低于-37.5 dB。

3 结 语

波束构成器是双(多)基地雷达、高频超视距雷达、三坐标雷达、相控阵雷达以及智能天线的中心部件之一,在确保运算速度和核算精度的前提下,本文提出的运用FPGA和ADSP器材完结的数字波束构成器较好地完结了预订的技能指标,逻辑规划选用VHDL言语结合原理图方法进行,有利于AS%&&&&&%规划;通用DSP器材21060的运用则能够满意实时核算波束构成系数和副瓣抵消系数的要求。本波束构成模块经实践电路测验标明彻底满意体系要求的20 M的波束构成速度要求,现已成功运用于多部现役雷达中,作用较好功用安稳,具有很高的实用价值。

发布者:小宇