导言

当今的嵌入式体系开发人员面临史无前例的应战,尽力向商场推出最具竞赛力的产品。

直到最近,完成的大部分体系还局限于需求许多软件并且功耗十分高的多芯片体系或许贵重的SoCASIC.可是,越来越多的规划团队感到受商场压力以及资源约束的影响,这些办法的吸引力越来越低。而关于根据ARM的嵌入式体系,FPGA技能、知识产权(IP)以及规划东西的开展促进了用户可定制SoC FPGA 的诞生。这些器材不光克服了传统办法的缺陷,并且在嵌入式体系完成上十分共同,具有显着的优势。

运用广泛的ARM处理器

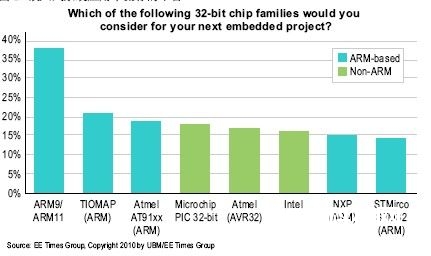

仅仅几年前,处理器商场仍是支离破碎。PowerPC、RISC、MIPS、SPARC 以及许多其他渠道都在竞赛商场主导地位。可是,跟着商场的老练,并且越来越专业化,某些渠道在一些运用范畴中锋芒毕露。特别是嵌入式体系运用范畴的ARM处理器(图1)特别如此。

图1. 嵌入式体系运用中盛行的渠道

在开展敏捷的嵌入式体系商场上运用十分广泛的ARM处理器十分合适规划人员运用。

首要,开展十分老练的软件、开发东西和ARM兼容器材辅佐体系完成了可以协同作业的处理计划东西箱。其次,受敏捷开展的ARM商场规划经济要素的影响,呈现了更好、更先进的体系完成挑选。

嵌入式体系规划应战

与以往比较,嵌入式体系开发人员有必要树立高性价比体系。敏捷扩张的全球商场对规划人员的要求越来越高。但我国、印度和拉丁美洲等新式商场范畴的机会也越来越多,这些商场越来越重要,不容忽视。为满意越来越高的用户根本需求,需求支撑各种规范和价格、功用以及特性的渠道。并且,竞赛在全球打开,这对规划团队的压力更大,要求在越来越小的商场窗口内推出特性丰厚的产品。

可是,对嵌入式产品的要求如此之高,规划团队却在不断削减。经济压力迫使许多公司减缩规划,规划资源也由此受到影响。成果,开发团队的规划在减缩,而作业强度却在增大。

对本钱十分重视的根据ARM的嵌入式体系规划人员越来越显着的感受到这一压力,清楚的认识到传统完成办法的缺陷。多芯片处理计划完成起来相对简单一些,可是本钱高,缺少灵敏性,功用/ 功耗方针达不到现在运用的需求。选用了软核处理器的单芯片处理计划完成起来也相对简单一些,可是难以抵达功耗和功用方针。ASIC SoC 具有板上硬核ARM内核,功耗和功用体现十分超卓,可是面市时刻长,不灵敏,关于大部分运用而言本钱过高。为前进竞赛力,嵌入式体系开发人员需求一种可以协助他们开发独具优势产品的处理计划,十分灵敏,功率也十分高。

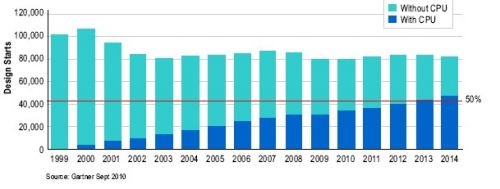

新一类SoC

在曩昔十年中,FPGA 内置嵌入式处理器的运用在稳步增长(图2)。因为Altera 在FPGA 技能上的前进,呈现了新一类SoC 器材,满意了现在嵌入式体系运用的多种功用需求。根据ARM的SOC FPGA 在一个SoC 中结合了硬核ARM处理器、存储器控制器以及外设和可定制FPGA 架构。这些SoC FPGA 处理了规划人员面临的许多难题,杰出了产品优势,价格和功用抵达最优,产品可以及时面市,延长了产品运用寿命。

图2.FPGA 中处理器的开展

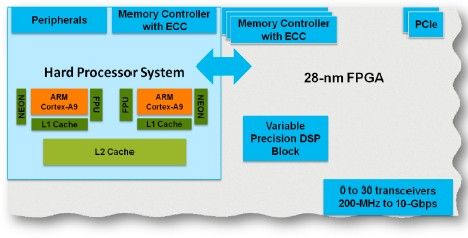

SoC FPGA

根据ARM的SoC FPGA(图3 所示)在单片FPGA 中严密结合了经过优化的“硬核”处理器体系(HPS)模块。HPS包括双核ARM处理器、多端口存储器控制器以及多个外设单元,处理器功用抵达4,000 DMIPS(DhrySTONes 2.1 基准测验),功耗不到1.8 W.这些硬核IP模块前进了功用一起降低了功耗和本钱,削减了对逻辑资源的占用,杰出了产品优势。用户可以定制片内FPGA 架构,开发专用逻辑。可编程功用支撑选用新的或许修正后的通讯规范和网络协议,进一步调整功用。

图3. 处理器与FPGA 架构严密集成

与传统的处理计划比较,SoC FPGA 在功用上有显着的优势。硬核单元相关于软核IP进行了很大的优化,在所选用的工艺节点上,完成了最好的功用、最低的功耗以及最高的密度。FPGA 通常是新工艺节点最早推出的器材,因而,规划人员运用SoC FPGA 可以运用最新最好的半导体技能。并且,与根据电路板的处理计划比较,片内总线严密衔接各个单元,进一步前进了功用和成效。从体系全体视点看,SoC FPGA 显着减小了体系体积,降低了功耗和本钱。

产品更敏捷面市

经过现场可编程渠道,运用现成的器材开发定制根据ARM的SoC FPGA,其开发时刻和本钱仅仅其他定制器材的一小部分。牢靠的FPGA 规划东西、直观的体系集成东西以及老练的ARM辅佐体系相结合,加快了开发进程,降低了危险。即便是第一次完成FPGA的规划人员,现在常用的东西支撑接口格局和规范,因而,他们可以比较轻松的从头运用已有软件、IP和其他规划内容。运用SoC FPGA 渠道,运用开发根底支撑条件,开发人员可以很快捉住嵌入式体系商场的机会。

灵敏性

在嵌入式体系商场上应对竞赛需求很高的灵敏性。网络和通讯运用有必要习惯新的或许改变的规范。工业和医疗供货商不一定需求大批量产品,可是对专业化产品有很大的需求。不考虑特别运用范畴,嵌入式体系开发人员有必要可以灵敏的应对剧烈的竞赛,运用最新的技能,很快捉住新的商场机会。

SoC FPGA 十分合适满意嵌入式商场需求。根据ARM的SoC FPGA 中的逻辑部分很简单应对各种变化,适用性较强。在SoC FPGA 中,逻辑是现场可编程的,意味着很简单敏捷修正,以杰出产品优势,进行更新或许重制某一产品型号。在有确保的情况下,即便设备在现场布置后,也可以进行从头装备。

可更新和规划重用

规划重用是办理本钱、缩短商场窗口、前进规划资源运用率的要害手法。可以在多个器材和系列中调整并从头运用规划内容,这种才能是无价的。当把现有规划或许IP模块运用到体积、功耗和功用需求都不同的器材上时,凭借这种办法,规划人员不需求从头开端从头进行规划。因为越来越多的规划团队涣散在世界各地,从头运用功用不光提高了效能,并且供给了同享和运用已有内容的好办法。

SoC FPGA 体系结构支撑多个IP内核,灵敏的习惯不同的器材系列。许多运用都有不同的价格、功用、功耗和其他约束,选用可重用和可更新内容很简单满意这些需求。跟着工艺技能的前进,选用这类FPGA 系列,经过鄙人一代产品中导入IP,可以便利的移植到下一工艺节点。

长寿命产品

关于许多运用而言,长寿命产品是要考虑的重要要素。产品生命周期,特别是医疗、工业和军用器材,长达10 到15 年,乃至更长。可是,IC 供货商的产品一般只供给较短的时刻。当这类产品的产品生命周期超越其%&&&&&% 组件时,规划人员会有很大的本钱价值,花费名贵的规划资源进行规划移植,或许重制。

为防止产品过期或许失效问题的晦气影响,主张需求较长产品生命周期的嵌入式体系开发人员挑选经过严厉牢靠性测验的实施计划,供货商在预期的产品生命周期内都可以供给支撑。因为其长寿命并且简单移植,工业、军事、航空航天、轿车以及医疗运用一直在选用FPGA.长寿命器材意味着很少在现场进行产品保护,然后降低了保护本钱,支撑将规划资源运用到新产品上。

Altera SoC FPGA

作为2011 年发动的“嵌入式计划”的一部分,ALTEra 为嵌入式体系商场供给28-nm根据ARM的SoC FPGA.这些Altera 产品具有:

■先进的硬核ARM处理器、外设和高速互联。

■片内Altera FPGA 架构、第二个存储器控制器以及PCI Express(PCIe)接口。

■支撑已有内容和IP集成的规划东西。

■选用或许不选用硅片,加快软件开发的仿真环境。

硅片

在28-nm 工艺节点,Altera 运用了定制办法,在Arria V 和Cyclone V FPGA 系列中供给ARM处理器,以满意多种嵌入式运用需求。在相同的TSMC 28-nm 低功耗(28LP)工艺上出产的两种系列产品都可以满意嵌入式体系的体系低功耗和低本钱需求。

Altera 的Cyclone V FPGA 系列十分合适对功耗和体积要求较高的运用,而Arria VFPGA 系列在体系结构上为满意高功用嵌入式运用而量身定制。

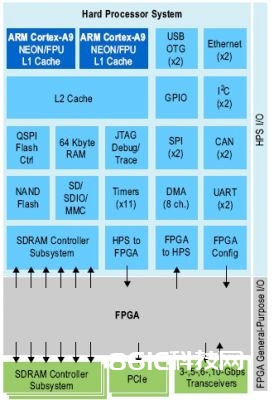

Altera ARMHPS(图4)在全功用HPS中结合了双核ARMCortex-A9 MPCore处理器、存储器控制器以及外设IP.28-nm 工艺节点的高功用双核ARMCortex-A9 MPCore 处理器作业速率高达800 MHz.双核装备完成了灵敏的SoC FPGA 产品,其功用可以进一步满意未来的需求。内置NEON媒体处理引擎和双精度浮点单元为多媒体和信号处理运用供给了规范化加快功用。每个内核32 个32-KB Level-1 高速缓存,在512-KB 同享Level-2 高速缓存的支撑下,经过减小延时和存储器拜访时刻,有助于提高功用。

图4. 根据ARM的硬核处理器体系简介

除了ARM内核自身,HPS还包括SDRAM控制器子体系、通用外设阵列,以及高速片内互联。外设组包括增强闪存控制器、MMC、DMA、USB 2.0、以太网、UART、SPI 和GPIO 接口。最终,Altera 共同的片内总线体系结构经过高速互联衔接了HPS和FPGA,总带宽大于125-Gbps.

在片内Altera FPGA 中完成了专用逻辑。因为可以长时刻安稳的为Cyclone V 和Arria VFPGA 系列供给支撑,Altera 产品在正常作业条件下,运用寿命一般可以抵达20 年以上。

快速体系规划东西

Altera 的Quartus II 开发软件供给了高效的规划环境,协助开发人员敏捷完成根据ARM的SoC.所包括的Qsys体系集成东西在IP功用和子体系之间主动生成互联逻辑,然后显着缩短了规划时刻,减轻了规划作业量。关于运用AMBA等通用接口规范和协议编写的IP,Qsys主动识别IP,将其与SoC 衔接。运用这一东西,很简单完成重用功用,在一片SoC FPGA 中一起运用已有或许第三方IP单元以及不同的规范接口。此外,开发人员很简单运用现有的内容,敏捷完成FPGA 开发。

软件开发

软件开发是开发嵌入式体系时十分重要的作业。出于这一原因,嵌入式软件开发人员一般运用名为“虚拟方针”的仿真环境,在可以运用硅片之前,编写、仿真并调试软件。运用Altera SoC FPGA 虚拟方针仿真环境,开发人员即便在拿到第一个硅片之前,也可以开端寄存器和二进制兼容软件开发。规划人员经过运用虚拟方针,提前完成大部分软件开发作业,降低了规划危险,更敏捷的将产品推向商场。

定论

与以往比较,现在的嵌入式体系开发人员有必要面临剧烈的竞赛,敏捷应对多变的规范、协议和需求,以更少的资源满意越来越高的各种商场需求。含有硬核处理器内核的SoC FPGA 不光支撑规划人员处理这些规划难题,并且还协助他们取得了显着的产品及时面市、价格/ 功用、杰出产品特色以及长寿命产品等优势。与传统计划比较,现在现已抵达了一个要害点,根据FPGA 的SoC 成为可行并且是首选的办法,必将在商场上取得广泛运用。