试验二:将MCLK和SMCLK装备为XT1(F5529的XT1为32.768KHZ)

/*1.装备IO口5.4和5.5为XT1功用。*/

/*2.装备XCAP为XCAP_3,即12PF的电容。*/

/*3.铲除XT1OFF标志位。*/

/*4.等候XT1起振。*/

#include <msp430.h>

void main(void){

P1SEL |= BIT0;P1DIR |= BIT0;//丈量ACLK用

P2SEL |= BIT2;P2DIR |= BIT2;//丈量SMCLK用

P7SEL |= BIT7;P7DIR |= BIT7;//丈量MCLK用

P5SEL |= BIT4|BIT5; //装备为XT1功用,电路板上晶振接于这两脚

UCSCTL6 |= XCAP_3; //装备电容为12pF

UCSCTL6 &= ~XT1OFF; //使能XT1

/*下面是很重要的一步:*/

/* XT1刚刚起振的时分或许有过错,导致时钟过错标志方位位,必须先清零*/

/*OFIFG即Osc Fault Flag,坐落SFRIFG1中*/

while(SFRIFG1 & OFIFG) //假如有时钟过错{

UCSCTL7 &=~(XT2OFFG+DCOFFG+XT1LFOFFG);//铲除3种时钟过错标志

SFRIFG1&=~(OFIFG);//铲除时钟过错标志位}

UCSCTL4&=(UCSCTL4&(~(SELS_7|SELM_7)))|SELS_0|SELM_0;

//将SMCLK和MCLK时钟源装备为XT1}

试验三:DCO-FLL数控振荡器结合锁相环

DCO模块在MSP430F5529系列芯片中非常重要,由于从MSP430F4XX开端,MSP430引用了FLL模块,FLL即锁相环,能够经过倍频的方法进步体系时钟频率,从而进步体系的运转速度。

DCO模块运转需求参阅时钟REFCLK,REFCLK能够来自REFOCLK、XT1CLK和XT2CLK,经过UCSCTL3的SELREF挑选,默许运用的XT1CLK,但假如XT1CLK不可用则运用REFOCLK。

DCO模块有两个输出时钟信号,即DCOCLK和DCOCLKDIV,其间,倍频计算公式如下:

DCOCLK = D*(N+1)*(REFCLK/n)

DCOCLKDIV = (N+1)*(REFCLK/n)

其间:n即REFCLK输入时钟分频,能够经过UCSCTL3中的FLLCLKDIV设定,默许为1,也便是不分频;

D能够经过UCSCTL2中的FLLD来设定,默许为1,也便是2分频;

N能够经过UCSCTL2中的FLLN来设定,默许值为32。

所以,体系上电后假如不做任何设置,DCOCLK的实践值为2097152,DCOCLKDIV的实践值为1048576。

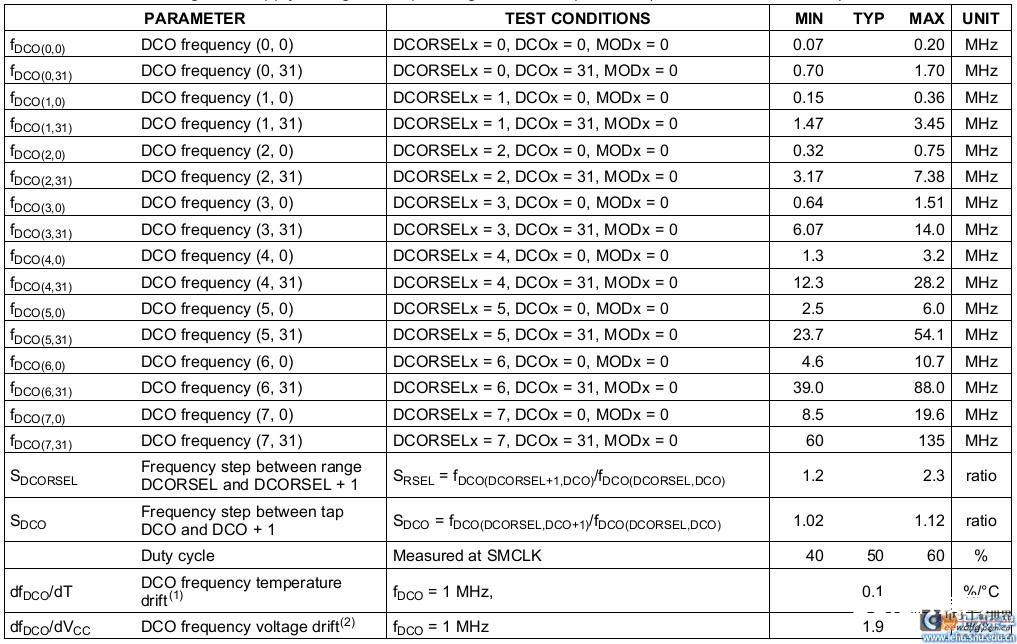

别的,装备芯片作业频率还需求装备DCORSEL和DCOx,DCORSEL和DCOx的详细效果如下:

DCORSEL坐落UCSCTL1,共3位,将DCO分为8个频率段。

DCOx坐落UCSCTL0共5位,将DCORSEL挑选的频率段分为32个频率阶,每阶比前一阶高出约8%,该寄存器体系能够主动调整,一般装备为0。

下表给出了相应设置情况下的频率调理规模:

/*经过DCO-FLL将32.768KHZ倍频到25MHZ*/

#include

#include “HAL_PMM.h”

void delay()

{

volatile unsigned int I;

for(I = 0; I != 5000; ++i){_NOP(); }}//延时函数

void main(void) {

WDTCTL = WDTPW+WDTHOLD;

P1SEL &= ~BIT1;

P1DIR |= BIT1;

P1SEL |= BIT0; //ACLK

P1DIR |= BIT0;

P2SEL |= BIT2; //SMCLK

P2DIR |= BIT2;

P7SEL |= BIT7; //MCLK

P7DIR |= BIT7;

P5SEL |= BIT4|BIT5;

UCSCTL6 |= XCAP_3;

UCSCTL6 &= ~XT1OFF;//翻开XT1,不然XT1LFOFFG或许报错

SetVCore(3); //进步Vcore电压到第一流,以满意倍频需求该函数坐落HAL_PMM.H中

__bis_SR_register(SCG0);//该语法为固定格局,意为将括号内的变量置位,SCG0与体系作业形式有关,此刻MCLK暂停作业

UCSCTL0 = 0; //先清零,FLL运转时,该寄存器体系会主动装备,不必管

UCSCTL1 = DCORSEL_6;

UCSCTL2 = FLLD_1 | 380;//FLLD=1,FLLN=380,则频率为

2*(380+1)*32.768=24.969MHZ

__bic_SR_register(SCG0);

__delay_cycles(782000);//体系自带的准确延时,单位us

while (SFRIFG1 & OFIFG) {

UCSCTL7 &= ~(XT2OFFG + XT1LFOFFG + DCOFFG);

SFRIFG1 &= ~OFIFG;

}

UCSCTL4 = UCSCTL4&(~(SELS_7|SELM_7))|SELS_3|SELM_3;

//挑选DCO作为时钟源

while(1){

P1OUT ^= BIT1;

delay();

}

}