TQ210的体系时钟装备和串口装备十分简略,本文从TQ210的体系时钟装备开端评论。

TQ210的时钟装备跟2440/6410的时钟装备差不多,仅仅锁相环的个数略有不同,装备进程是相同的。装备体系时钟,无非要经过以下几个进程:

(1)设置体系PLL确定时刻

(2)装备PLL

(3)装备各模块分频系数

(4)切换到PLL时钟

简略的看着四步好像没有条理,可是看到手册中的“S5PV210时钟生成线路图”就能够了解了,现在截图如下:

上图中无非就三种模块,PLL、MUX和DIV,MUX操控时钟源挑选,PLL担任生成PLL时钟,DIV担任分频。

为了体系安稳,在规划电路时咱们一般不会运用太高频率的晶振(防止高频线间/层间搅扰),可是,S5PV210的内核需求的作业频率很高(最高能够到达1G),这中情况下,咱们通常是经过锁相环(英文简称PLL)来对外部时钟源进行倍频,然后供内核运用(在TQ210开发板上选用的是12M晶振),因而,S5PV210供给了4个PLL(详细四个PLL的用处能够自己阅览手册),分别是APLL、MPLL、EPLL和VPLL,经过装备S5PV210供给的锁相环操控存放能够设置锁相环的倍频系数,使内核作业频率到达800M或许1G。需求留意的是PLL设置完结之后并不能马上安稳的作业,需求一个起振进程,在这段时刻内PLL的输出频率很不安稳,因而,内核的作业也是很不安稳的,为了处理这个问题,S5PV210供给LOCK_TIME(确定时刻)模块(经过设置相应的LOCK_TIME存放器能够设定确定的时刻长度),当锁相环操控存放器的值产生改动时,体系会确定内核,确定内核时CPU不作业,此刻确定模块会依据LOCK_TIME设定的值进行计时,计时完结后CPU才会运用PLL供给的时钟信号作业。

默许状况下内核运用外部时钟源供给的时钟,装备好PLL后需求设置相应的MUX,使内核在PLL供给的时钟信号下作业。从上面的时钟生成线路图中还能够看到许多MUX,咱们能够依据实践要求进行装备。留意,选通PLL的MUX应该在设置完分频之后装备。

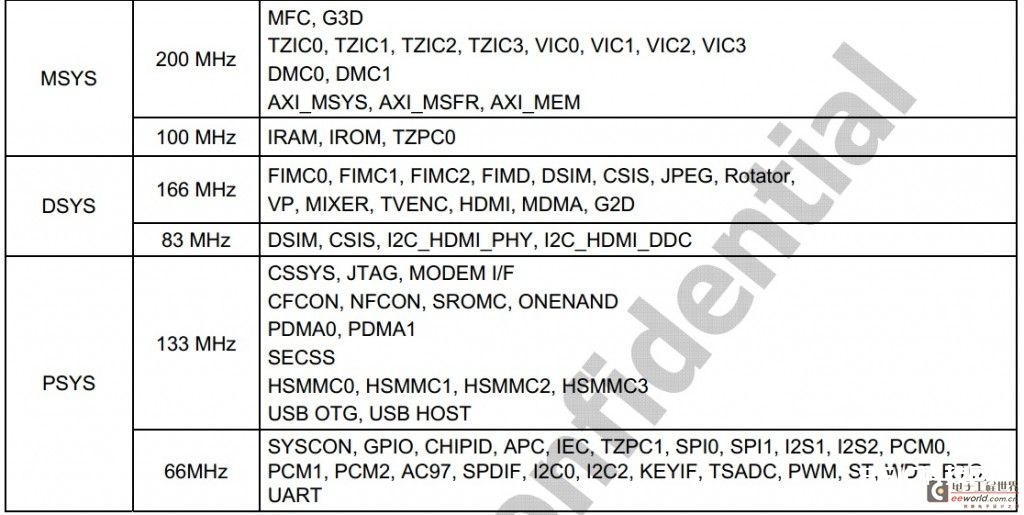

内核能够作业在1G的时钟信号下,而其他设备作业频率较低,因而,需求依据实践要求进行分频,分频的值并不是随意的,应该依据手册上供给的参阅值进行装备,以下是各模块的最高作业频率:

这样,装备完PLL和分频之后选通PLL,使CPU在高频形式下作业。

以上S5PV210的体系时钟装备逻辑,或许说了这么多您也很难了解,这时,您应该参阅代码、手册和本文进行了解。S5PV210体系时钟装备的代码许多,这儿我就不贴出来了,下面,咱们评论一下S5PV210的串口部分。

S5PV210的串口装备比起体系时钟来讲更为简略。学习串口应该先了解下串口的作业原理,认识一下串口,详细的作业原理能够阅览手册的串口部分,需求知道串口的相关装备参数,如波特率、数据位、中止位、校验位等,流操控相关的也能够看看,了解后自行装备一下,咱们这儿只评论下串口的装备,为了简略起见,咱们以非FIFO形式为例进行评论。

直接阅览手册的存放器操控部分,第一个存放器就是ULCON。ULCON能够装备数据位长度、中止位长度、教研形式和红外形式,假如需求设置为8N1,非红外形式则能够将ULCON装备为0x3。

第二个存放器是UCON,咱们只装备一下传输/接纳形式和时钟源即可,其他的选用默许方法,为了简略,咱们挑选“中止或查询形式”,以PCLK为时钟源,因而,能够装备UCON为0x5|(1<<10)。

咱们运用非FIFO形式,能够不设置UFCON存放器。

UMCON是流操控相关的,咱们也不作装备。

接下来的四个STAT存放器是表征串口作业状况的,无需装备。

接下来的UTXH是发送缓冲区存放器和URXH是接纳缓冲区存放器。

UBRDIV和UDIVSLOT是装备串口波特率的,算法也比较简略,手册上供给了三个束缚公式:

DIV_VAL = UBRDIVn + (num of 1s UDIVSLOTn)/16

DIV_VAL = (PCLK/(bps X 16))-1

或许

DIV_VAL = (SCLK_UART / (bps X 16)) – 1

咱们挑选PCLK作为串口作业时钟源,PCLK的频率为66.5M,假如咱们要设置串口波特率为115200则能够如下核算:

DIV_VAL = (66.5 X 10^6 / (115200 X 16)) – 1 = 35.07,故UBRDIV应该设置为35,

别的,0.07*16 + 1 = 2,所以UDIVSLOT中应该有两个1,故能够设置为0x3,当然也能够是0x88等,只需有两个1位就能够。

到这儿,串口就装备好了,仍是比较简略的,您装备完后还能够自己装备下FIFO和流操控,学完中止和DMA之后还能够装备为中止或许DMA形式,这儿就不多说了。代码比较简略,网上的比如也比较多,我就不上传了。