当时运用广泛的串行通讯接口标准首要有RS232,RS422和RS485,其间RS232串行通讯办法选用单端输入输出,传输间隔短、通讯速率低、抗干扰功用差;RS485与RS422均选用差分串行输入输出,但RS485只要一对双绞线,只能作业于半双工形式;RS422选用全双工通讯形式,经过两对双绞线可完结双向收发互不影响,且传输速率可达10 Mbit·s-1,传输间隔可达2 000 m。以RS422通讯协议为代表的串行通讯在数据通讯吞吐量较小的微处理电路中运用愈加简洁、灵敏,尤其在远间隔信息传输中更发挥着不行代替的效果。

1 硬件电路规划

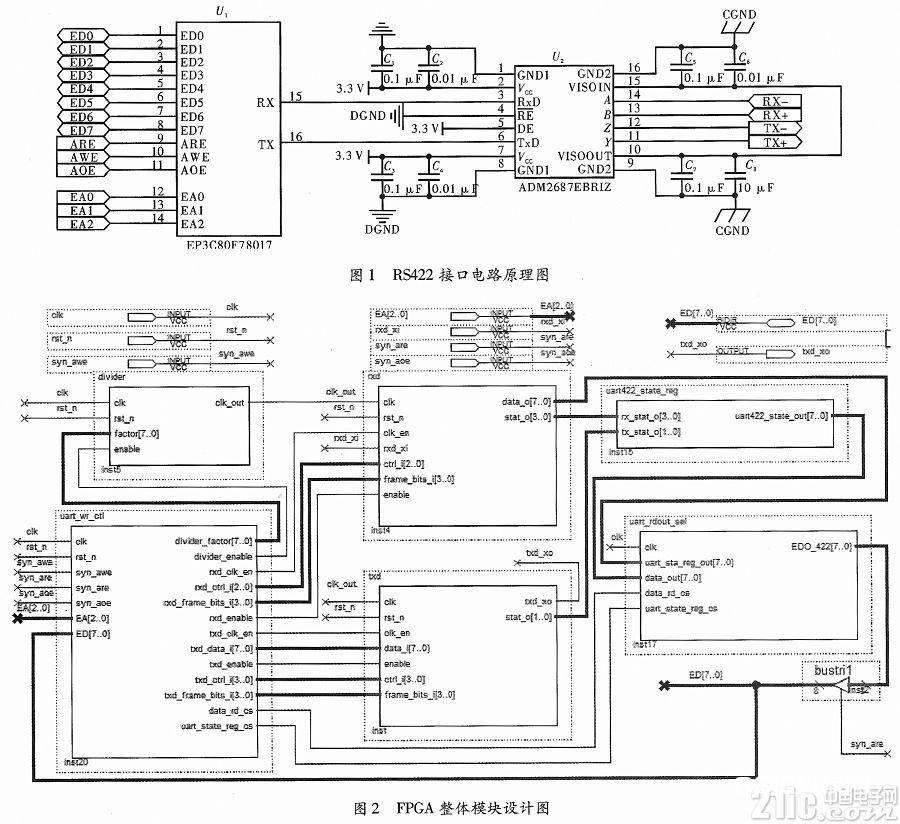

规划首要运用Altera公司的EP3C80F78017和ADI公司的ADM2687EBRIZ。RX+、RX-为差分信号输入端口,差分信号经U2解差分后传输到U1中,经过其间数据接纳模块的处理,传送并行数据给CPU。CPU发送的并行数据,经U1中的数据发送模块处理输出待处理的TTL信号,经过U2差分处理后输出差分信号到总线上,TX+、TX-为差分信号输出端口。U1一起接纳CPU输出的操控信号,以完结对通讯参数的调整。其规划原理如图1所示。

2 软件程序规划

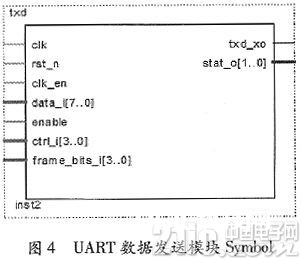

2.1 FPGA全体模块

clk为大局时钟输入端,rst_n为大局复位端,syn_awe为写使能指令端,syn_are为读使能指令端,syn_aoe为输出使能指令端,EA为地址总线数据端,ED为数据总线数据端,rxd_xi为串行数据输入端,txd_xo为串行数据输出端。

divider为时钟发生模块,首要发生通讯波特率采样时钟;txd为UART数据发送模块,进行数据并串转化;rxd为UART数据接纳模块,进行数据串并转化;uart_wr_ctl为总线解析模块,首要担任解析CPU总线指令,操控其他模块的作业状况;uart422_state_reg为UART作业状况模块,归纳rxd和txd的作业状况并输出;uart_rdout_sel为数据输出挑选模块,其首要操控总作业状况数据与UART接纳数据的挑选输出。

2.2 时钟发生模块

模块首要为UART数据收发模块供给了作业时钟,依据时钟分频系数对输入的大局时钟进行计数处理,输出UART通讯波特率16倍的分频时钟频率。将时钟分频系数加1,除掉大局时钟频率,则等于分频时钟频率。

clk为大局时钟输入端,rst_n为模块复位端,enable为模块使能端,factor为时钟分频系数输入端,clk_out为分频时钟输出端。本模块选用计数分频的规划思维,当计数值大于factor值1/2时,clk_out输出为高电平,反之则输出低电平。

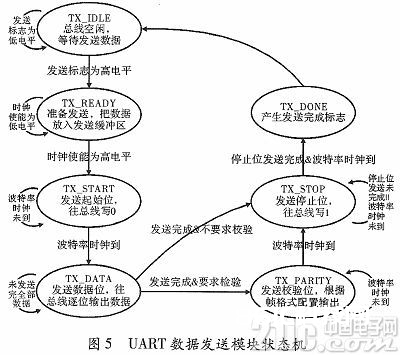

2.3 UART数据发送模块

UART数据发送模块规划简略,首要依据输入的操控信号,对输入的并行数据进行并串转化,并以操控信号要求的数据帧格局和波特率选用LSB形式发送出去。模块在接纳到有用的8位并行数据后,依据操控信号指令,按串行数据帧格局,开始添加1位开始位0,然后依据操控信号指令决议是否添加奇偶校验位,再在尾部添加1位或2位中止位1,最终组成通讯两边约好的数据帧格局发送出去。

clk为模块作业时钟输入端,rst_n为模块复位端,clk_en为时钟使能端,enable为模块使能端;ctrl_i为操控信号输入端。其间,ctrl_i[3]操控使能发送奇偶校验,ctrl_i[2]操控奇偶校验挑选,ctrl_i[1]操控中止位的个数,ctrl_i[0]操控数据发动发送;data_i为待发送数据输入端,frame_bits_i为帧数据位数输入端,txd_xo为数据发送端,st at_o为发送状况输出端。其间,stat_o[1]为发送器完结发送符号位,star_o[0]为发送缓冲器数据载入完结符号位。UART数据发送模块状况机,如图5所示。

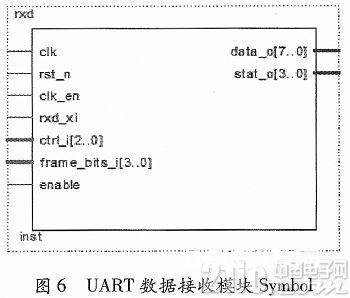

2.4 UART数据接纳模块

因为外部运用环境的影响,RX输入线上或许发生毛刺。为减小这一影响,该模块规划时选用“大都表决法”,详细处理办法是在一个数据位中心取3个点的采样电平值,若少于2个点为电平“1”,则将该数据位判为电平“0”,不然判为电平“1”。

clk为模块作业时钟输入端,rst_n为模块复位端,clk_en为时钟使能端,enable为模块使能端,rxd_xi为UART数据接纳端,ctrl_i为操控信号输入端。其间,ctrl_i[2]操控使能接纳奇偶校验,ctrl_i[1]操控奇偶校验挑选,ctrl_i[0]操控读UART数据缓冲器使能,frame_bits_i为帧数据位数输入端,data_o为已接纳数据输出端,stat_o为接纳状况输出端。其间,stat_o[3]为帧过错符号位,stat_o[2]为接纳缓冲器数据溢出符号位,stat_o[1]为校验过错符号位,stat_o[0]为数据完结接纳符号位。UART数据接纳模块状况机,如图7所示。

2.5 总线解析模块

本模块首要依据地址总线数据和数据总线数据,以及输出使能和读写使能指令信号,发生对其他模块的操控信号和片选信号,即解析了总线指令。

clk为大局时钟输入端,rst_n为模块复位端,syn_awe为写使能指令端,syn_are为读使能指令端,syn_aoe为输出使能指令端,EA为地址总线数据端,ED为数据总线数据端,divider_factor为输出时钟发生模块时钟分频系数,divider_enable为输出时钟发生模块使能指令信号,rxd_clk_en为输出UART数据接纳模块时钟使能指令信号,rxd_ctrl_i为输出UART数据接纳模块操控指令信号,rxd_frame_bits_i为输出UART数据接纳模块帧数据位数,rxd_enable为输出UART数据接纳模块使能指令信号;txd_clk_en为输出UART数据发送模块时钟使能指令信号,txd_data_i为输出UART数据发送模块待发送数据,txd_enable为输出UART数据发送模块使能指令信号,txd_ctrl_i为输出UART数据发送模块操控指令信号,txd_frame_bits_i为输出UART数据发送模块帧数据位数;data_rd_cs为读UART接纳数据指令挑选端,uart_state_reg_cs为读总作业状况数据指令挑选端。

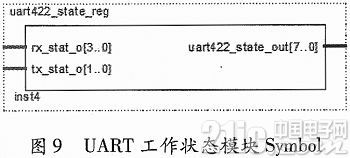

2.6 UART作业状况模块

模块首要是将输入的UART数据接纳模块状况数据与UART数据发送模块状况数据合并为总作业状况数据,并进行输出。

rx_stat_o为UART数据接纳模块状况数据的输入端,tx_stat_o为UART数据发送模块状况数据的输入端,uart422_state_out为总作业状况数据输出端。

2.7 数据输出挑选模块

模块首要依据输入的读数据指令挑选信号,对输入的总作业状况数据和UART接纳数据,进行挑选输出。

clk为大局时钟输入端,uart_sta_reg_out为总作业状况数据输入端,data_out为UART接纳数据输入端,data_rd_cs为读UART接纳数据指令挑选端,uarrt_state_reg_cs为读总作业状况数据指令挑选端,EDO_422为所选数据输出端。

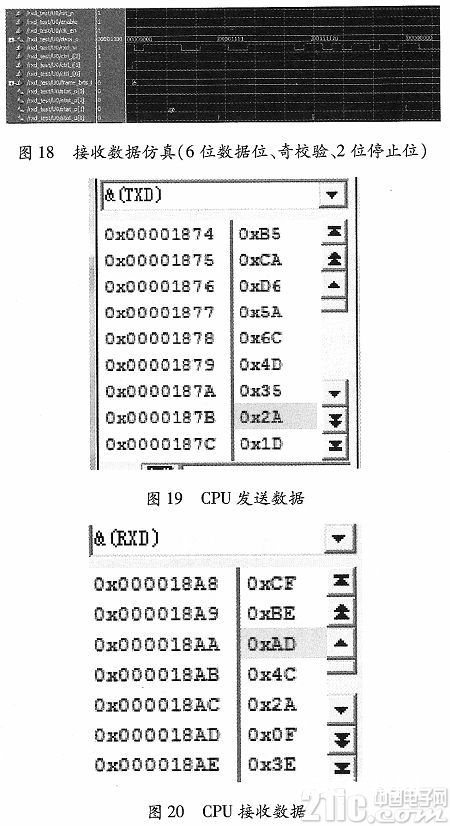

3 仿真成果

在Modelsim_SE10.1b的开发环境下,对FPGA源代码进行逻辑归纳仿真,其仿真成果如图11~图18所示。仿真成果表明,规划完结了预期的各种逻辑功用,收发数据准确无误。图19和图20分别为CPU发送和接纳的数据,图中所示数据与FPGA仿真成果共同。

4 结束语

规划灵敏简略,并可动态调整通讯波特率和数据位及中止位长度,还可挑选是否使能数据奇偶校验功用,较好地完结了RS422串行总线之间的数据传输,然后大幅增强了规划的可靠性和通用性。后期测验运用证明了,该接口电路规划具有较高的稳定性和实用性,并可用于RS422通讯的许多场合。