跟着人们订货无线服务数量的激增、各种服务类型的多样化,以及更低的便携式设备接入因特网的费用,使得关于添加根底设施容量的需求日益显着。3G智能手机、3G上网本和3G平板电脑是引发关于无线数据服务和基站容量的爆破性需求的首要推动力。将功用叠加到现有的无线宽带设备,例如:HSPA+和EV-DO(即3G+),现已处理了一部分数据吞吐量的需求,但因为服务速度慢,无线服务供货商仍饱尝用户责备,尤其是在大城市中,用户不满的状况愈加严峻。

无线运营商有向更高带宽服务开展的方案,如:LTE和LTE-Advanced,以应对这一应战;可是,布置这些4G技能还需求几年时刻,可是与此一起数据吞吐量的要求却还在不断上升。当全球的“桌上型”无线宽带服务需求无所不在时(据业界分析师猜测这一现象将在往后6年内呈现),无线服务供货商仍将面对进步基站密度的压力。很多添加根底设施的需求以及本地商场的剧烈竞赛将使得基站OEM厂商面对涨价压力。

以更低功耗和价格来添加容量——是神话仍是实践?

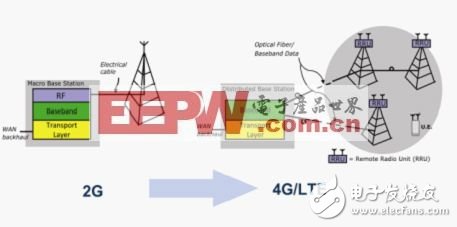

曩昔,在长途通讯职业更高功用的基站收发台(BTS)一般需求耗费更多电能和更高的总具有本钱。可是,未来这一状况将有望改动。在亚洲和非洲,Green field 3G和增强型3G的布置将引发严酷的降价及能耗压力,这很或许会涉及整个无线根底设施商场。关于无线根底设施OEM厂商来说,要害的是要经过下降基站元器材资料本钱,保持和增强盈余才能。如图1所示,下降元器材资料本钱的一种办法是从传统的、单一基站布置转变为分布式布置模型。

图1——基站网络的演化

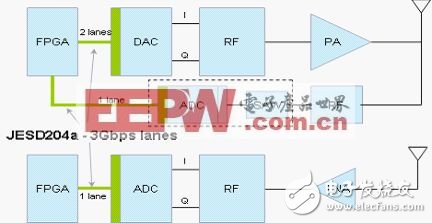

这种拓扑结构处理了上文中说到的一些应战,而且也促进了根据SERDES的逻辑器材的运用和这类器材运用的成熟化,用以支撑从RRU(射频拉远单元)到BTS的光纤数据传输。可是,因为射频拉远单元所包含的射频和数据转化设备,其本钱仍占了BTS的元器材资料总本钱中的很大部分。一类更低本钱、低功耗的新式FPGA,如LatTIceECP3器材,可经过与集成了支撑CPRI和OBSAI基带接口的SERDES相结合,供给灵敏的数据处理才能,而且下降射频拉远单元的总本钱。可是,添加数据吞吐量的需求现已使得关于传统并行数据转化器接口的各方面要求都迫临其极限,比如:功用、印刷电路板布局的杂乱性和制作本钱以及保护数据完整性所需的尽力。这些应战导致了在实践RRU数据转化器和数据处理FPGA之间的SERDES功用需求从BTS接口迁移到数字数据/操控接口,如图2所示。JEDEC JC-16协会于2008年发布了这种新式接口的敞开的职业规范,称之为JESD204A,并为进一步下降射频拉远单元的元器材资料本钱带来了很大的期望。

Figure 2 – JESD204A Interface

图2——JESD204A接口

现在,NXP半导体供给的CGVTM数据转化器上的JESD204A接口是一种高速串行接口,运用兼容CML的差分信号和8B/10B编码。现在的最高数据速率为3.125 Gbps,经过数据转化器和FPGA之间的多路通道完成恣意巨细的体系带宽,完成每个通道带宽超越312.5兆字节/秒的数据速率。因为JESD204A支撑准确的跨线同步,它自身还支撑正交采样,这关于以OFDM调制机制为根底的3G和4G空中接口来说是十分必要的。根据SERDES的数据转化器和FPGA的优势

可编程逻辑和高速数据转化技能在基站规划的整个演化进程中发挥了十分重要的效果。数据转化器供给了射频功率放大器与无线通讯单元中射频小信号部分的桥接,而FPGA为规划师们供给了满足的灵敏性,使得在空中接口规范彻底确认之前就可以开端规划。

日益添加的基站数据吞吐量的需求导致了无线通讯单元的元件本钱和功耗的添加,并使得相关印刷电路板和接口愈加杂乱,一起愈加着重对信号完整性的要求。兼容了JESD204A的数据转化器,具有下降元器材资料本钱及其他商业和技能方面的长处,使得BTS的OEM厂商无法疏忽这个新式、具有突破性含义的接口挑选。不断节约的元器材资料本钱很快超越了选用该接口技能的花费,而且还进步了体系的可靠性,然后进一步节约了本钱。

JEDEC JESD204A经过简化印刷电路板布局大大地下降了射频拉远单元的元器材资料本钱,印刷电路板布局的简化在削减了电路板层数的一起缩小了电路板尺度,这两者都是添加电路板本钱的重要因素。此外,因为JESD204A大大下降了数据转化器和FPGA之间的接口信号数量,然后使得整个体系的可靠性得到增强。因为低电压摆幅的CML下降了功耗,电源的元器材资料本钱也或许相应地削减。JESD204A除了有助于下降元器材资料本钱,还对规划的体系架构级有很大的好处。强壮的嵌入式协议(没有软件开支),包含数据加扰、单比特过错检测和数据线路同步丢掉检测,以及加强了射频印刷电路板上模仿和数字部分的阻隔,进步了抗噪声才能。许多业界观察员以为数据转化接口向JESD204A的转化是不可避免的,就像在PC和DSP硬件领域中向USB、PCI Express和串行RapidIO高速串行的转化相同。

正如数据转化器那样,关于本钱、功耗和功用的更高要求也迫使FPGA架构产生严重改动,然后显著地进步了其功用、特性和逻辑密度。与ASIC比较,FPGA因其自身的灵敏性和更快的产品上市时刻,长期以来一向广受赞誉,可是曩昔FPGA仅限用于“接口逻辑”和“批改过错”的运用。现在因为FPGA的价值已大大扩展,这一状况现已产生改观。例如,莱迪思低本钱、低功耗的新式FPGA系列,具有增强型功用,如集成的SERDES、DSP的数据通路和嵌入式存储器,现已成为了很多射频拉远单元规划的重要组成部分。体系规划工程师们现在仅需花费一半的功耗和本钱,运用这款极具竞赛力的带有SERDES功用的FPGA,在杂乱的信号途径运用中运用这个可编程渠道,完成比如数字下变频(Digital Down Conversion,DDC)、数字上变频(Digital Up Conversion,DUC)、波峰因数缩小(Crest Factor ReducTIon,CFR)和数字预失真(Digital Pre-DistorTIon,DPD)功用。

小结

BTS的OEM厂商需求仔细考虑,运用新的JESD204A高速串行接口为射频拉远单元节约元器材资料本钱和其他费用,以作为应对未来不断添加的无线根底设施ASP的降价压力的一种重要手法。

曩昔,FPGA和数据转化器在射频拉远单元规划中发挥了要害效果;现在,它们在下降体系构建本钱上发挥着更大的效果。根据SERDES的、可扩展的JESD204A接口在多个ADC / DAC和多个FGPA之间供给了一个无缝、简化的、低功耗和低本钱的数据高速公路。功用丰厚、更低本钱的FPGA完成了更快的产品上市时刻和更短的本钱回收周期,并供给可以更有效地应对不断改变的规范的灵敏性。体系规划工程师现在还具有一个令人兴奋的、改善的东西集来应对不断开展的无线宽带商场的应战。