ccd(charge couple device)是一种电荷藕合式光电转化器材。在物体位移丈量体系中,常常以ccd作为位移传感器。当一束曝光器宣布的激光照射到被测物体上并发生漫反射时,反射光将经透镜聚集后成像在ccd上,以使ccd光敏单元感光,然后发生搬运电荷。这样ccd驱动电路就会发生必定频率的驱动脉冲以反映物体位移信息,输出的信号为模仿信号。经a/d转化后,便可由后续处理电路收集和运算。

实践丈量作业中,因为作业环境、光照强度或被测物体的不同,会使得照射到被测物体外表的激光束的反射率改动比较大,因而,ccd上成像点的光强就会时强时弱。ccd光敏单元在过强或过弱光线照射下,会发生过饱和或不饱和的电荷,然后使输出的模仿信号不能满意数据收集要求,因而不能实在反映被测物体的位移信息,影响终究计算成果的精确性,而发生了较大的差错。鉴于以上原因,为了能够得到精确的被测物体的位移成果,应使ccd丈量体系输出的模仿信号峰值尽量稳定在某一规模内。

cpld杂乱可编程逻辑器材具有集成度高,体积小,速度快等特色。经过cpld能够以厂家供给的cad东西为开发渠道,结合原理图修改与vhdl言语软件编程,以在cpld中完结数字硬件中的大多数逻辑电路。因而,本文所规划的ccd主动增益体系的中心部分选用cpld来完结。

ccd信号的主动增益调整

ccd传感器输出的模仿信号与入射光光强、帧搬运频率有关。其巨细随入射光光强的增大而增大,随帧搬运频率的增大而减小,因而,经过改动入射光的光强或帧搬运频率就能够调整输出的模仿信号峰值。本体系便是选用调理帧搬运频率来到达主动增益调整的目的。

一般情况下,帧搬运脉冲由ccd驱动电路输出,其频率巨细直接影响ccd传感器的积分时刻。帧搬运频率越小,传感器积分时刻越长,相应地,ccd传感器曝光时刻也越长,光敏单元捕捉到的光量也越多。当帧搬运频率过小时,光敏单元所发生的光电电荷就会到达过饱和状况,输出的模仿电压峰值将会超越所要求的规模。反之,输出的模仿电压峰值将会低于所要求的规模。因而,可规划一个ccd输出电压峰值的采样、坚持电路,再对此峰值进行a/d转化,一起与所要求的规模进行比较。当其超出规模值时,可增大帧搬运频率;而当其值低于规模时,则可减小帧搬运频率。

体系全体结构

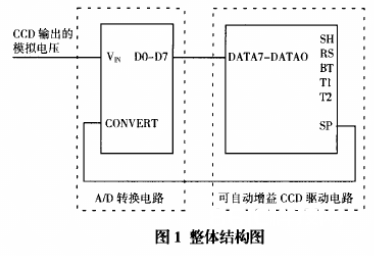

这种根据cpld的ccd主动增益调整驱动电路的全体结构如图1所示,该体系共分为两部分。第一部分为模仿/数字转化电路,该部分选用一个转化精度为8位的a/d转化器来将ccd输出的模仿电压值转化为数字量。第二部分为可主动调整增益的ccd驱动电路,此部分选用cpld进行装备,可主动完结增益调整及ccd驱动信号的输出,并可为a/d转化器供给转化操控脉冲。

a/d转化部分

ccd的输出信号为模仿量,故须经a/d将其转化成数字量,以便cpld进行处理。在本规划中,a/d转化器选用的ad9048可作业在35msps的高速上,由cpld发生的单位搬运脉冲sp可为其供给转化操控脉冲convert。在convert的上升沿到来后,a/d9048对ccd相应象素点上输出的模仿电压值进行采样,并在convert下降沿到来之前输出转化成果,该成果由cpld存放并终究得到一帧中ccd输出的模仿电压峰值的巨细。

可主动增益的ccd驱动电路规划

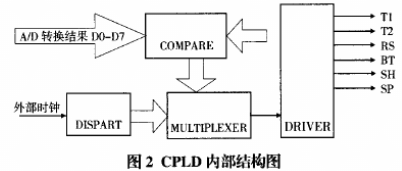

此电路使用cpld规划,其内部可划分为四个模块(如图2所示),整个芯片所需的时钟由外部晶振或振荡电路供给。

第一个分频模块dispart用于对外部时钟进行一到八倍的分频。第二个模块mul tiplexer是一个多选一模块,由compare操控。第三个模块compare用于对a/d转化的成果进行存放,并将一帧完毕后得到的ccd输出电压峰值与所设定的阈值进行比较,若超出阈值上限则输出成果减一,mulTIplexer选出频率较高的一路时钟作为driver的输入时钟脉冲;反之,则对compare的输出成果加一,mulTIplexer选出频率较低的一路时钟作为driver的输入时钟脉冲。第四个模块driver用来发生驱动ccd的信号及一位单位搬运信号。

当mulTIplexer选出频率较高的一路脉冲作为driver的输入时钟,再由driver发生ccd驱动信号时,驱动信号中的帧搬运脉冲sh频率就会添加,然后使ccd传感器的曝光时刻变短,ccd输出的模仿电压峰值下降;反之,sh频率减小,曝光时刻变长,ccd输出的模仿电压峰值升高。这样,经过以上进程,便可调理ccd模仿电压峰值的规模。

本规划使用的ccd器材为tcd1201d,选用二相驱动脉冲作业,驱动电路要发生六路作业脉冲,其间五路用作ccd供给作业脉冲,别离为帧搬运脉冲sh、电荷搬运脉冲t1、t2、复位脉冲rs、补偿脉冲bt;另一路为单元搬运脉冲sp。此六路脉冲由cpld中的driver部分发生,此部分可用硬件描绘言语vhdl进行规划。

发生补偿脉冲bt和单元搬运脉冲sp时,因为bt占空比为2:1,因而应对输入的时钟脉冲三分频,低电平占时钟脉冲一个周期,高电平占时钟脉冲两个周期,其详细的程序部分如下:

process(clk)

begin

if(clk’event and clk=‘1’)then

counter1<=counter1+1;

if counter1=2 then

mbt<=‘0’;

counter1<=0;

else mbt<=‘1’;

end if;

end if;

bt<=mbt;

sp<=mbt and(not msh2);

end process;

该器材有2048位有用像元,作业时还要有46位哑像元输出,一个扫描周期至少应有2094个像元时钟周期,因为该器材两并行输出,因而,一个帧搬运周期内的t1、t2至少别离有1047个脉冲。因为t1、t2的周期持平,方向相反且周期为bt周期的二倍,因而,发生sh、t1、t2的程序进程如下:

process(mbt,clk)

begin

if (mbtevent and mbt=‘1’)then

mt<=not mt;

end if;

if(clk’event and clk=‘1’)then

t1<=mt and (not msh2);

t2<=(not mt)or msh2;

end if;

end process;

process(mt)

begin

if(mt’event and mt=‘1’)

then

counter2<=counter2+1;

if counter2=1100 then

counter2<=0;

msh1<=‘1’;

msh2<=‘1’;

elsif(counter2<=3)then

msh1<=‘1’;

msh2<=‘1’;

elsif(counter2>3 and counter2<=5)then

msh1<=‘0’;

msh2<=‘1’;

else

msh1<=‘0’;

msh2<=‘0’;

end if;

end if;

sh<=msh1;

end process;

发生rs的程序进程如下:

process(mbt,clk)

begin

if(clk’event and clk=‘0’)then

rs<=not mbt;

ned if;

end process;

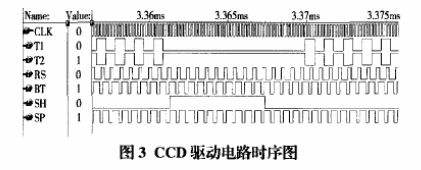

至此,这样ccd驱动电路的六路信号均发生完毕,能够进行仿真,其成果如图3所示。

由图3可看出,所发生的驱动信号满意tcd1201d所需驱动时序联系。

dispart模块是用来对外部时钟进行分频的,可使用vhdl言语描绘。其间二、三分频的程序如下:

process(clk)

begin

if(clk’event and clk=‘1’)then

mf1<=not mf1;

end if;

f1<=mf1;

end process;

process(clk)

begin

if(clk’event and clk=‘1’)

then

counter2<=counter2+1;

if counter2=2 then

mf2<=‘1’;

counter2<=0;

else

mf2<=‘0’;

end if;

end if;

f2<=mf2;

end process;

其他分频数与之相似,这儿不再赘述。

compare模块是用来对a/d的转化成果进行存放,并在一帧完毕后,对得到的电压峰值进行判别以确认其是否在所规则的阈值规模内,然后操控多选一模块mulTIplexer。使用vhdl言语描绘时,其程序的首要部分如下:

process(clk)

begin

if(clk’event and clk=‘0’)then

if data>reg_data then

reg_data<=data;

end if;

end if;

end process

process(sh)

begin

if(sh’event and sh=‘1’)

then

if(reg_data>200)then

if(reg_q(2)or reg_q(1)or reg_q(0)=‘1’ then

reg_q<=reg_q-1;

end if;

elsif(reg_data<150)then

if(reg_q(2)and reg_q(1)

and reg_q(0)=‘0’ then

reg_q<=reg_q+1;

end if;

else reg_q<=reg_q;

end if;

end if;

q<=reg_q;

end process;

这儿,第一个进程的作用是得到ccd输出电压的峰值,data为a/d转化的成果。第二个进程的作用是判别峰值是否在阈值规模内,以调整输出q,去操控多选一模块挑选相应的时钟脉冲来作为driver的输入。

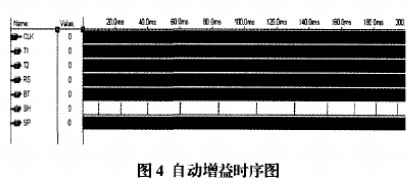

将规划好的各个模块使用原理图进行衔接,然后进行器材挑选,本规划选cpld芯片为epm7128slc84-15,然后编译,再进行仿真,即可所得,如图4所示的时序图。

调查该时序图中能够看到,如cpld的作业与开始的规划目的相符,即可将程序下载到epm7128slc-15芯片中。

试验成果

进行电路的原理图规划,制成电路板,与ccd传感器衔接。将光束打在一反射物体上,反射光为ccd传感器所承受,然后调理光照强度,使用示波器调查sh,能够看到sh的频率随光强的增大而增大。

完毕语

本文所规划的带的ccd驱动电路,可集成于一片cpld芯片中,较曩昔的由几十片芯片组成的驱动电路,其面积大大减小了,并且带有主动增益调整功用,对频率的选出选用逐次迫临的方法。因而,选用恰当的步长,就能够将sh的改动操控在比较适宜的规模内,然后使峰值的收敛到达较好的作用。此外,主动增益调整也避免了人工调整的费事和差错,提高了精度,下降了劳动强度。

责任修改:gt