2.5.1 实例的内容及方针

1.实例的首要内容

本节旨在经过给定的工程实例——“蜂鸣器播映梁祝音乐”来了解Altera Quartus II软件的根本操作、规划、编译及仿真流程。一起运用依据Altera FPGA的开发板将该实例进行下载验证,完结工程规划的硬件完结,了解Altera FPGA开发板的运用及装备办法。

在本节中,将首要解说下面一些知识点。

- Quartus II工程创立及特点设置。

- Quartus II源文件规划输入办法。

- Quartus II束缚规划。

- Quartus II工程编译。

- Quartus II功用仿真。

- Quartus II时序仿真。

- Quartus II硬件下载。

经过这些知识点,依照下面供给的练习流程,读者能够迅速地把握运用Quartus II软件进行FPGA开发的办法。

2.实例方针

经过详细的流程解说,读者应到达下面的方针。

- 了解Quartus II软件的操作环境。

- 了解Quartus II软件开发FPGA的根本流程。

- 可独立运用Quartus II软件开发新工程。

2.5.2 渠道简介

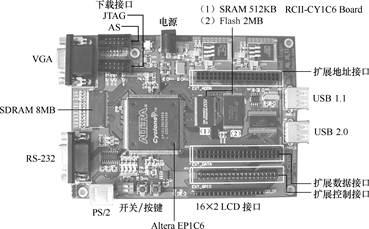

本实例依据赤色飓风II代Altera板,在此开发板上集成了Altera的Cyclone一代FPGA及相关的丰厚外设资源。

此开发板愈加详细的信息、扩展附件及运用办法,能够到赤色飓风的官方网站:http://www.fpgadev.com获取更多的信息。

本实例将在这个开发板上对Altera的FPGA规划流程做一个全面的介绍,依照此例程的流程便可在该开发板上运转一个FPGA程序。如图2.29所示为此开发板的外观图。

图2.29 赤色飓风II代Altera板外观图

2.5.3 实例详解

本节将运用图解的办法将整个流程一步一步展示给读者,使读者能够轻松把握Quartus II的开发流程。

1.工程创立及特点设置

(1)发动Quartus II软件。

装置Quartus II软件后,在桌面或许程序组中发动Quartus II软件。

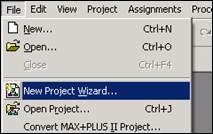

(2)翻开新工程导游。

发动软件后,挑选“File”菜单的“New Project Wizard”选项,翻开新建工程导游,如图2.30所示。在新建工程导游的 “介绍”页面中,单击“Next”按钮进入下一页。

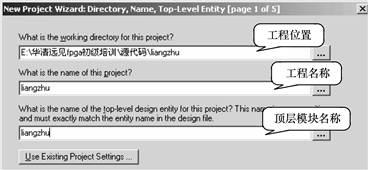

(3)设置工程特点。

如图2.31所示,在新建工程导游的第一页对工程作业目录、工程称号以及顶层模块称号进行设置。

图2.30 新建工程

图2.31 设置工程特点

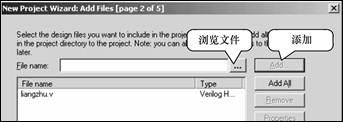

(4)增加规划文件。

在新建工程导游的第二页挑选为工程增加规划文件,如图2.32所示。

图2.32 增加规划文件

(5)挑选FPGA器材。

在新建工程导游的第三页,为工程装备相应的器材类型和参数,如图2.33所示。选取的器材类型将在彻底编译时将工程规划映射到对应的器材逻辑资源上。

图2.33 挑选器材类型

(6)完结工程创立。

装备完器材特点后,挑选Quartus II默许的归纳东西、仿真东西及时序剖析东西,完结工程的创立。

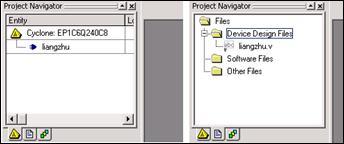

挑选软件左面的工程浏览器的 按钮来办理已增加的文件。如图2.34所示,左面为工程层次窗口,右边为规划文件窗口。

按钮来办理已增加的文件。如图2.34所示,左面为工程层次窗口,右边为规划文件窗口。

图2.34 工程结构窗口

2.规划输入

(1)增加规划文件。

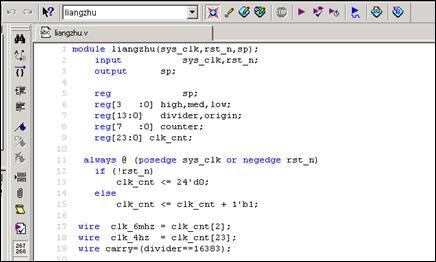

假如在创立工程时没有为工程增加规划文件,能够挑选“Project”菜单的“Add/Remove Files in Project”选项,为工程增加规划文件。在本实例中,读者可向工程增加实例代码中的liangzhu.v文件。

增加后,在工程浏览器中双击liangzhu.v图标,即可查看该Verilog规划文件,如图2.35所示。

图2.35 Verilog规划文件

(2)装备器材特点。

相同的,假如在创立工程时没有为工程装备器材类型及特点,能够在工程浏览器的工程实体图标上单击右键,挑选“Device”选项,为工程装备器材特点,如图2.36所示。

若在树立工程时现已装备好,则可单击“Device Pin Options…”按钮,进一步设置器材的相关特点,如图2.37所示。

图2.36 器材挑选 图2.37 器材特点装备

在如图2.38所示的对话框中,可对FPGA所运用的装备芯片及未用管脚等进行装备。

图2.38 指定装备形式

挑选“Unused Pins”选项卡,将不运用的管脚装备为三态,如图2.39所示。

图2.39 未用管脚置三态

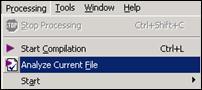

(3)剖析工程。

编写规划输入文件后,首要要进行工程剖析,意图是为了查看规划输入的语法。单击 “Start Analysis Synthesis”按钮剖析工程,如图2.40所示。

“Start Analysis Synthesis”按钮剖析工程,如图2.40所示。

图2.40 剖析工程选项

查看信息栏,修正一切呈现的过错,直到剖析经过,如图2.41所示。

图2.41 剖析工程成果,没有报错

3.束缚规划

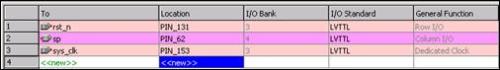

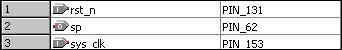

(1)管脚分配。

管脚分配的效果在于将规划输入文件的端口与实践的器材进行映射,完结规划输入模块端口在实践器材管脚上的实例化。在Quartus II软件中能够在管脚分配主窗口中对管脚的分配进行设置,如图2.42所示。

图2.42 管脚分配

经过东西栏中的方便按钮能够协助用户快速的进行管脚分配,如图2.43所示。

经过管脚分配主窗口中的管脚信息能够看到管脚的I/O品种、管脚的序号、Bank地点的方位、I/O运用的电压规范等,如图2.44所示。

图2.43 指定管脚方便按钮 图2.44 管脚信息

(2)其他束缚。

除了对工程的管脚进行束缚外,Quartus II软件还答应用户对其他的一些束缚进行设置,例如面积束缚、速度束缚、时钟束缚、资源束缚等。这些束缚都归于较为严厉的工程设置,在本实战练习中无需考虑。

4.编译工程

(1)彻底编译。

有了完好的规划输入、完好的束缚条件后,就能够对工程进行彻底编译了,如图2.45所示是彻底编译的选项。

依据工程复杂度的不同,Quartus II在进行彻底编译时所耗费的时刻差异也很大。在工程浏览器中显现了编译的类别及进展,协助用户了解编译的进程。

图2.45 彻底编译选项 图2.46 编译状况

若在编译进程中呈现过错提示,用户可在信息栏中查看过错的信息,修正一切存在的过错后从头进行编译,直到能够无过错地完结编译,如图2.47所示。

图2.47 编译成果信息栏

(2)编译陈述。

Quartus II编译完毕后,为用户供给了一个完好而详细的编译陈述。经过该陈述,用户能够查看工程运用资源的状况及体系能够到达的功用,如图2.48所示。

5.功用仿真

(1)树立仿真文件。

挑选Quartus II软件“File”菜单的“New”选项,翻开新建其他文件对话框,挑选新建波形图文件,如图2.49所示。

图2.48 编译成果陈述 图2.49 新建波形图

(2)增加调查信号。

用户能够经过双击波形窗口中的空白区域为工程增加需求调查的信号,如图2.50所示。

图2.50 仿真波形窗口

在翻开的刺进节点或总线对话框中,翻开“Node Finder…”(节点查找器),如图2.51所示。经过节点查找器,用户能够方便地挑选需求调查的信号。

图2.51 刺进节点或总线对话框

挑选Filter:“Pins:all”,然后点击list列出所用输入/输出端口,如图2.52所示。

图2.52 节点查找器

选中一切信号,单击 按钮,即可将选中信号参加调查方针窗口中,如图2.53所示。

按钮,即可将选中信号参加调查方针窗口中,如图2.53所示。

图2.53 已增加好的信号

(3)设置仿真时刻最小距离。

考虑到硬件环境供给的是50MHz的时钟,即时钟周期为20ns,设置“Grid Size”为20ns。挑选“Edit”菜单的“Grid Size”选项进行设置,如图2.54所示。

(4)设置仿真时刻长度。

挑选“Edit”菜单的“End Time”选项,设置仿真时刻长度为10ms,如图2.55所示。

(5)增加鼓励信号。

选中sys_clk信号,单击 时钟按钮,将该信号设置为时钟波形,周期为20ns,如图2.56所示。此信号代表了体系时钟。

时钟按钮,将该信号设置为时钟波形,周期为20ns,如图2.56所示。此信号代表了体系时钟。

图2.55 设置仿真完毕时刻 图2.56 设置时钟

选中rst_n信号,单击 高电平按钮,将该信号设置为1。此信号代表了复位信号。

高电平按钮,将该信号设置为1。此信号代表了复位信号。

增加鼓励信号后,挑选保存文件,此刻的波形如图2.57所示。

图2.57 以设置好的输入波形

(6)生成功用仿真网表。

挑选“Tools”菜单的“Simulator Tool”选项,翻开仿真器,如图2.58所示。

将仿真器的仿真形式设置为“Functional”(功用仿真),如图2.59所示。

图2.58 仿真器选项 图2.59 仿真对话框

单击“Generate Functional Simulation Netlist”按钮发生仿真网表。仿真网表是将工程规划文件进行编译及映射后生成的用于进行仿真的文件,仿真器依据仿真网表进行仿真,直接反响了工程规划文件的实在状况。

(7)开端功用仿真。

单击“Start”按钮开端进行功用仿真,如图2.60所示,能够看到仿真的进展,依据工程的复杂度,仿真进程所耗费的时刻也有所不同。

图2.60 仿真进展

仿真完结后单击“open”按钮翻开仿真成果,如图2.61所示。

图2.61 仿真波形成果

6.时序仿真

功用仿真后,假如波形没有问题,开端做时序仿真,查看波形延时对规划是否有影响。

挑选“Tools”菜单的“Simulator Tool”选项,翻开仿真器,挑选仿真形式为“Timing”,即时序仿真形式,如图2.62所示。

图2.62 挑选时序仿真

单击“Start”按钮,开端时序仿真。时序仿真比功用仿真要慢一些。

仿真完结后,查看仿真成果。经过波形能够看到发生了7.06ns的延时,如图2.63所示。

图2.63 查看仿真成果

能够看到,功用仿真并不包括推迟,而时序仿真则会依据详细的器材参数装备及资源运用状况将推迟仿真出来。功用仿真首要用于验证工程规划文件逻辑的正确性,而时序仿真更能表现实在的硬件运转进程中规划文件的履行进程。

7.下载程序

仿真验证完毕后,用户就能够将工程下载到实践的开发板上进行验证了。

挑选“Tools”菜单的“Programmer”选项,翻开下载器界面,如图2.64所示。

图2.64 下载界面

首要单击“Hardware Setup”按钮,挑选下载电缆,如ByteBlasterII(LPT1),即打印机接口下载线,然后挑选下载形式为JTAG(在线调试)形式或许AS(固化至EPCS装备芯片)形式,并挑选对应的下载文件。

衔接好下载电缆后,选中“Program/Configure”即可下载。

8.成果查验

下载完毕后,用户应该能够在开发板的蜂鸣器上听到演奏的梁祝乐曲。假如选用的是JTAG下载形式,那么将开发板断电后,从头上电,则乐曲不会再持续演奏;若运用的是AS下载形式,则乐曲还会再持续演奏。

若下载后没有听到乐曲,用户应查看几个首要简单出问题的过程。例如,规划输入是否完好,管脚是否分配,下载电缆是否正确衔接等。

2.5.4 小结

上述流程便是一个完好的FPGA规划流程。尽管此实例完结的功用比较简单,但关于初学者来说,是一个不错的入门实例。其首要意图是让初学者对FPGA的规划有一个开始的了解。经过该实例来了解Quartus II软件的运用,为往后的学习打下根底。

在实践的FPGA规划中,在每个阶段都会遇到许多问题。为了完结终究的方针,需求充分地使用Quartus II规划软件。这需求一个比较长时刻的学习和堆集,期望经过这个实例能让初学者更快地入门。