数字信号处理器(DSP)是选用数字计算办法对信号进行处理的专用芯片。因为其功能安稳,可大规划集成,编程性高和易完结等长处,被广泛应用。其间,以图画处理与DSP技能结合较为遍及,因为图画所包含的信息数据量大,而DSP的处理速度快,易于完结很多数据高速传输的特色能够满意这一要求。

现在,图画处理技能已在通讯、信息、电子、航天及军事等范畴得到广泛应用。与图画处理有关的体系规划中,FPGA加DSP构架是遍及的运用办法。为充分利用DSP的功能,需求在FPGA中对图画进行相应的预处理,再把图画数据传输给DSP进行处理。所以FPGA与DSP之间的数据传输技能变得不可或缺。

图画数据传输的速度与安稳性对整个体系的功能具有很大的影响。本文介绍了一种根据EDMA的高速安稳的数据传输办法,并在TI的DSP开发渠道CCS下,对该办法的功能进行了测验。

1 方案规划

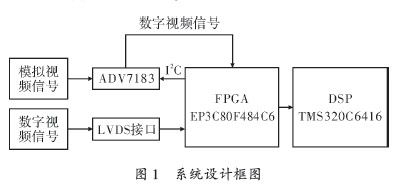

文中图画传输硬件体系结构如图1所示。该体系中选用Ahera公司的Cyclone3系列FPGA:EP3C80F484C6,Analog Device公司的视频解码芯片ADV7183,差分输入14位数据的LVDS接口和TI公司的TMS320C6416。该体系既可收集模仿视频信号,又可收集数字视频信号。模仿信号通过模数转化芯片ADV7183后变成数字信号,数字信号经由LVDS差分接口进入FPGA。为调试便利,模仿图画与数字图画一致运用320×256标准。DSP以EDMA办法接纳,通过FPGA预处理后的图画数据,在CCS渠道下进行显现以验证传输的正确性。

2 接口电路规划

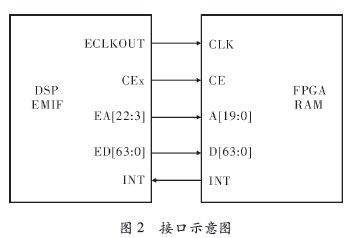

DSP以EDMA办法从FPGA中读取数据,需求FPGA在内部装备一块巨细恰当的存储空间。FPGA作为一个存储器,通过DSP的外部存储器接口(EMIF)与DSP相连。硬件衔接如图2所示。

图2所示为FPGA与DSP的硬件上衔接示意图。实践运用时,并没有运用上述一切信号线。FPGA运用到的管脚如下:CLK,CE,A[19:0],D[63:0]和INT。CLK是DSP供给的同步读写时钟,CE是DSP的片选信号,A[19:0]为地址线,D[63:0]地址线。INT为中止信号。

FPGA与DSP的传输机制:FPGA运用QuartusII开发渠道往双口RAM中写数,写满后用中止管脚INT来告诉DSP读数。DSP收到FPGA的中止信号后,开端读数。读数期间片选信号CE有用,FPGA把DSP片选信号CE作为双口RAM的读使能,在使能期间用DSP供给的时钟CLK读取数据。

体系中DSP供给给FPGA的时钟CLK为100MHz。接纳模仿图画时,图画数据为8位,只运用D[7:0]8根数据线;接纳数字图画时,图画数据为14位,运用D[15:0]16根数据线,高两方位0。数字图画与模仿图画均为320×256。

3 EDMA传输

TMS320C6000系列DSP中的,增强型直接存储器拜访(EDMA)操控器履行一切二级高速缓存/内存操控器与外设之间的数据传输。

EDMA操控器包含事情和中止处理寄存器、事情编码器、参数RAM和地址发生硬件电路。事情是触发EDMA发动的同步信号,事情寄存器用于捕获EDMA事情。事情编码器处理多个事情发生时事情的优先级问题。对应事情的传输参数存储在EDMA参数RAM中,而且传递给地址发生硬件单元,进行寻址EMIF或外设履行相应的读写操作。

3.1 传输流程

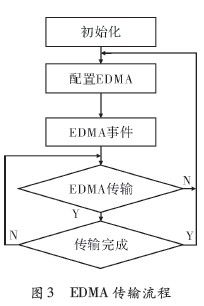

运用EDMA数据传输的办法有两种,一种是CPU初始化的EDMA;第二种是事情触发的EDMA。一切的EDMA通道都有一个特定的同步事情与之对应,如外围设备事情、外部硬件中止或EDMA传输完结事情都能够同步触发EDMA的传输。当通道对应的同步事情发生或由CPU同步该通道时,通道就完结一次数据传输恳求。由事情触发的EDMA传输实时性好,是一种常见的传输办法。体系选用的便是事情触发形式,触发信号便是FP GA给DSP的中止信号。图3为EDMA的传输流程。

3.2 EDMA装备

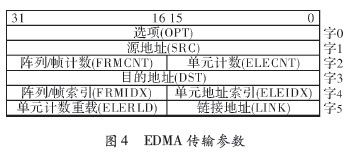

同步事情发生时,EDMA传输的数据巨细和源意图地址由参数RAM中的参数决议。拜访EDMA的参数RAM时需求通过外围总线。EDMA传输参数,如图4所示。

选项(OPT)部分首要用于传输数据的最小单元、数据传输的源地址和意图地址的寻址形式。体系中的最小传输单元为1 Byte,源地址设置为一维源,意图地址设置为二维源。数据传输形式为帧同步。传输数据块的行数设置255(实践传输行数为256),列数设置为320。

源地址(SRC)设置了源数据地点的地址,体系该参数装备为0xA0000000,指向FPGA意图地址(DST)设置了数据要被传输到的存储空间的地址。

完结传输进程为把一幅320×256 Byte的图画从FPGA缓存到了SDRAM中。传输14位的数字图画时,一个像素的图画数据占用2 Byte,所以要把选项(OPT)中的最小传输单元改为2 Byte。

3.3 程序完结

相应的EDMA通道初始化完结后,使能并翻开相应的中止。FPGA每发生一次EDMA同步事情,即往INT管脚发一次中止信号,EDMA就能完结一次指定要求的传输,然后等候下一次同步事情。

4 试验成果

DSP供给给FPGA的时钟为100 MHz,传输一幅320×256的图画需求约为0.8 ms。传输速度较快,能够满意图画快速传输以及实时处理的要求。TI的开发渠道CCS能够调查存储器中的数据,并把收到的存在存储器中的数据显现成图画,然后能够验证传输的正确性以及安稳性。数据源为模仿图画时,相机拍照的原始图画和DSP收到的图画如图5和图6所示。

数据源为数字信号时,原始图画为14位数据,TI的仿真渠道只能显现8位图画,所以DSP中收到的图画数据只能以高8位进行显现,但会丢掉图画的一些细节,图画全体偏暗。因为体系选用的数字图画由中波红外热像仪收集,因为视场不同,原始图画无法收集。图7为提取高8位图画数据显现的图画。

图5~图7中的图画通过屡次传输验证,没有呈现过错的图画。阐明该体系完结的图画数据传输满意图画实时处理的速度要求以及牢靠性要求。

5 结束语

介绍了一种FPGA向DSP的数据传输办法,描绘了EDMA的特色以及由其操控的数据传输的完结进程。所介绍的办法在开发的试验渠道上,进行了验证。文中介绍了FPGA向DSP的传输,更改EDMA的源地址与意图地址及相关参数能够完结DSP向FPGA的数据传输。