软过错是指高能粒子与硅元素之间的相互作用而在半导体中构成的随机、暂时的状况改动或瞬变。跟着SRAM工艺的功用日益前进,越来越低的电压和节点电容使得SRAM器材更易呈现软过错。软过错不只会损坏数据,并且还有或许导致功用丧失和严峻的体系毛病。各种工业操控器、军事装备、网络体系、医疗设备、轿车电子设备、服务器、手持设备和消费类运用都易遭到软过错的损伤。一个未经纠正的软过错有或许导致各类使命要害型运用D如植入式医疗设备、军用和轿车电子设备中运用的高端安全体系等D呈现体系毛病。

本文旨在解说软过错是怎么产生,以及怎么损坏半导体存储器中存储的重要数据的。为此,本文将论述软过错的来历以及它们的产生概率。此外,本文还将解说软过错是怎么影响存储单元(每个单元存储一个位)并导致它们改动状况的。本文还将探求软过错的不同来历,以及用于消减其影响的技能-包含工艺和体系层面上的技能。终究,本文将扼要描绘存储器中的片上纠错码(ECC)是怎么消减软过错影响的。

近年来,半导体技能取得了巨大前进,但这种前进也带来了新的问题。当今的CMOS工艺已缩至很小的尺度,以至于地外辐射和芯片封装正导致越来越多的毛病。因为这些毛病是可逆的,它们被称为软过错。软过错初次呈现于1978年,因为受铀污染的封装模块,英特尔公司无法向ATT交给其出产的芯片。20世纪70年代,软过错首要与动态RAM(DRAM)有关,这是因为它们的芯片封装资料含有微量的放射性污染物。

软过错是指高能粒子与硅元素之间的相互作用而在半导体中构成的随机、暂时的状况改动或瞬变。但与硬过错不同的是,一个简略的复位/重写操作可以康复受影响器材的正常运转。数字和模仿电路、传输线路和磁存储器中都或许产生软过错,但半导体存储器最易呈现软过错,其原因是它们的单元尺度较大,并且每个位坚持某种状况的时刻较长(因而添加了危险)。 软过错有或许翻转一个或多个位,这取决于诱发粒子抵达器材时的能量。一个高能粒子与半导体衬底之间的相互作用将产生多个电子空穴对。它们在耗尽区中产生的电场将导致一次电荷漂移,然后导致电流扰动。假如这个电流移动的电荷跨过了存储单元(每个单元存储一个位)的临界电荷,所存储的数据就有或许翻转,然后导致下一次被读取时呈现过错。

软过错分为两级-芯片级和体系级。当芯片中的放射性原子衰变并开释出阿尔法粒子时,芯片级软过错将产生。它们一般是由高能粒子的辐射导致的(鄙人文中解说)。这些阿尔法粒子与某个存储单元磕碰,然后导致其改动状况。当所传输的数据遇到噪声时,体系级软性过错将产生。这种过错一般在数据坐落总线而非存储器中时产生。操控器将噪声解读为数据。这个过错数据终究被视为正确数据,然后导致寻址或处理过错。

用于衡量软过错产生率的软过错率(SER)决议了器材因高能粒子产生毛病的概率。因为软过错是随机的,软过错的产生并不决议存储器的牢靠性,而是决议其毛病率。在那些选用了软过错应对机制的体系中(首要是高安全性和高牢靠性体系),假如一个软过错(被称为“所检测到的不行康复的过错”-DUE)被检测到,体系将重启,以防止损坏重要数据。假如未重启,它终究将成为一次无记载数据损坏(SDC)。SDC要比DUE危险得多,因为SDC会导致数据丢掉,而DUE只会导致体系在短时刻内不行用。在许多的消费电子设备中,软过错的危险并不很大,它们更或许因软件过错或部件损耗产生毛病。

软过错的产生概率取决于许多要素,如入射粒子、碰击区域和电路规划等。电容和电压更高的电路更不简单呈现软过错, 但这会引起更慢的逻辑门和更高的功耗。因而,跟着芯片工艺的不断前进,软过错的产生概率也越来越大。电容和电压的组合被称为临界电荷(Qcrit)。它被界说为一次粒子碰击导致电路产生毛病所必需具有的电荷。因为逻辑电路中的每个节点都有其共同的电容和输出间隔,因而,Qcrit一般以节点为单位丈量。此外还有必要留意,Qcrit 会随温度缓慢改动。

电路软过错 = k X 通量 X 面积 X e-Qcrit/Qcoil

其间,k = 取决于详细工艺的常数

通量 =中子通量

面积 = 对软过错灵敏的电路面积

Qcoll = 所收集电荷与所生成电荷的比率

该模型被称为中子诱发型电路软过错的Hazucha Svensson模型。

导致软过错的原因

阿尔法粒子

阿尔法粒子由两个质子和两个中子组成,类似于一个氦核。它们由放射性原子核在阿尔法衰变过程中开释。 阿尔法粒子具有数个MeV的动能,低于中子。阿尔法粒子具有一个细密的电荷层,在穿过半导体衬底时将产生多个电子空穴对。假如这种扰动满意强,它就有或许翻转某个位。因为这种状况一般只会继续几分之一纳秒,因而很难被检测出。

芯片被封装在含有微量放射性污染物的资料,如锡球或加工资猜中。塑封资料、封装和其它安装资猜中的微量铀- 238、铀- 232的放射性衰变会产生低能阿尔法粒子。但是,咱们简直不或许保持完成大多数电路的牢靠功用所需的抱负资料纯度(小于0.001次/小时/平方厘米)。微量的环氧树脂可为芯片屏蔽阿尔法辐射,然后下降软过错的产生概率。

世界射线

制造商已设法操控了开释阿尔法粒子的污染物,但他们却无法抗击世界辐射。事实上,在现代半导体器材中,世界射线是最或许导致软过错的原因。世界射线中的首要粒子一般不能抵达地球表面,但它们会产生一串高能次级粒子,其间大多数是高能中子。中子不带电荷,因而不会导致软过错,但却能被芯片中的原子核抓获,然后生成阿尔法粒子,继而导致软过错。中子所阅历的衰减很小,可穿透厚达5英寸的混凝土。

因为大气屏蔽效应跟着海拔的升高而削弱,世界辐射将随之添加。因而,飞机和卫星中的存储器模块极易呈现软过错,软过错率是地上模块的数百倍乃至数千倍。此外,因为上述大气屏蔽效应的削弱,坐落极地的存储模块也极易呈现软过错。为削减软过错,高危险运用中所运用的模块需求经过一个名为辐射硬化的工艺。尽管如此,因为出产辐射硬化芯片需求许多测验(和时刻),它们一般都归于旧的工艺节点。

热中子

因为存在中子抓获反响,短缺动能的中子是软过错的一个重要来历。(硼磷硅玻璃介电层中许多存在的)硼同位素(10B)原子核抓获一个热中子后将开释一个阿尔法粒子、锂原子核和伽马射线。阿尔法粒子和锂原子核都能导致软过错。硼在出产中被用于下降玻璃的消融温度,因而具有更好的回流和整平特性。

在重要规划中,贫硼(只含11B)可用于下降软过错率,经过运用磷硅玻璃(PSG)氧化层代替硼磷硅玻璃(BPSG)来完成。贫硼关于肿瘤放射医治中运用的医疗电子设备特别重要。中子和医治中运用的光子束相结合将构成一个热中子通量,然后导致极高的软过错率。尽管如此,热中子并非现在导致软过错的首要原因,制造商现已过150nm工艺节点消除了含硼酸介电层。

消减软过错的影响

改善工艺和存储单元布局

咱们可以经过添加存储单元中所存储的临界电荷进步存储器的牢靠性。此外,咱们还可以运用一种可消减分散层厚度的工艺前进存储器抵挡软过错的才能。该工艺可缩短带电粒子在存储单元中存在的时刻。三阱架构也可用于将电荷驱离有源区。该工艺构成一个与 NMOS耗尽区相反的电场,迫使电荷进入衬底。它仅适用于NMOS区产生软过错的状况。

体系层面的消减技能

在体系层面上,规划人员可以运用外部纠错码(ECC)逻辑消减软过错的影响。在该技能中,用户运用额定的带奇偶校验位的存储芯片检测和纠正过错。正如人们所料,体系层面的消减技能较为贵重,并且添加了FPGA软件的复杂性。

改动芯片规划和架构

这是抗击软过错的最佳办法。芯片规划人员可以经过将ECC算法植入到芯片中消减软过错的影响。在写操作时,ECC编码器算法为存储器中存储的每一个可寻址的数据字写入奇偶校验位。在读操作时,ECC检测算法运用奇偶校验位确认数据位是否现已改动。假如呈现单位过错,ECC纠错算法将确认相关位的方位,然后经过将该数据位翻转至其互补值帮忙纠错。

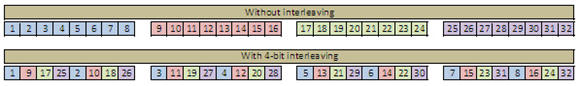

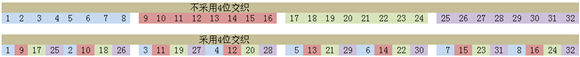

尽管如此,ECC不能独立应对多位翻转过错。因而,规划人员有必要选用位交错技能。该技能安排位线的办法是将物理上相邻的位映射到不同的字寄存器上。位交错间隔将映射到同一个字寄存器上的两个接连位分隔。假如位交错间隔大于一次多单元碰击的分散规模,它将在多个字中导致单位翻转,而不是在一个字中导致一次多位翻转。

典型的位交错间隔取决于详细工艺。中子测验和随后的物理MPU剖析用于确认每种工艺节点的安全交错间隔。在一个位交错存储器中,单位过错纠正算法可用于检测和纠正一切过错。ECC算法仅适用于受影响数据字的副本。存储器中的数据依然含有已翻转的位。假如存储器中的这个已翻转的位没有被纠正,同一个数据字中的另一次位翻转就或许导致一次多位翻转。因而,ECC逻辑有必要指示出单位翻转的产生和纠错。然后,体系可以运用该信息辨认该事情,并回写纠正后的数据。这种技能被称为存储器冲洗技能。

跟着半导体芯片变得越来越小,产生软过错的危险也在不断升高。存储单元的Qcrit会跟着其尺度的缩小而削减,这使得其更易翻转。因而,许多专家猜测,软过错将成为这种趋势的限制要素,并且终究将到达饱和点,除非咱们开宣布可以克服软过错的新技能。此外,跟着技能进入人类日子的更多范畴,人们关于牢靠性的要求只会越来越高。这种趋势催生了对存储器模块的片上ECC的需求。一切存储器厂商都已开端推出具有片上ECC功用的芯片,以满意商场对高牢靠性存储器的需求。SRAM范畴的全球领导者赛普拉斯公司具有一个根据ECC的异步SRAM系列,该系列是当今商场上牢靠性最高的异步SRAM。具有ECC功用的16Mbit异步SRAM已开端投产,4Mbi版别也已开端供给样品。