导言

在数字体系规划中,依据不同的规划需求,经常会遇到偶数分频、奇数分频、半整数分频等,有的还要求等占空比。在依据cpld(杂乱可编程逻辑器材)的数字体系规划中,很简略完成由计数器或其级联构成各种形式的偶数分频及非等占空比的奇数分频,但对等占空比的奇数分频及半整数分频的完成较为困难。

本文运用vhdl(甚高速集成电路硬件描绘言语),经过quartus ⅱ 4.2开发渠道,规划了一种可以完成等占空比的整数和近似等占空比的半整数分频器,这种规划办法原理简略,并且只需很少的cpld逻辑宏单元。

1、规划原理

体系规划框图如图1所示。

依据不同分频系数设置恰当的计数器周期,每个计数值对应输入时钟信号fi的一个周期,让q0只在fi的上升沿及恰当的计数规模内发生高电平,最终将q0和q1进行逻辑或操作,从而得到所需的分频信号fo。q1的作用是在奇数分频中补足下降沿处半个时钟周期,使其等占空比,以及在半整数分频中,在时钟下降沿处发生分频信号的上升沿,以完成半整数分频。

下面介绍怎么确认计数器周期以及q0、q1发生高电平输出时各自的计数规模。为叙说便利,现规则如下符号:分频系数为divide(max downto 0),其间max是分频数对应二进制数的最高位,关于半整数分频,最低位即第0位为小数位;q 0_count和q1_count分别为q0和q1发生高电平的计数规模,并记divide(max downto 1)为a,divide(max downto 2)为b,divide(max downto 0)-1为c。

1.1 偶数及奇数分频

计数器周期都为0到c。等占空比的偶数分频很简略完成,在此不加叙说。对奇数分频,只需当q0_count<a时q0输出高电平,当q1_count=a-1时q1输出一个周期的高电平,其他情况下q0和q1都为低电平,然后把q0和q1逻辑或,所得的输出fo便是所需的基数分频时钟信号。

1.2 半整数分频

计数器周期为0到c。假如整数部分是偶数,只需当q0_count<b时q0输出高电平,当b≤q1_count<a+b时q1输出高电平,其他情况下,q0和q1都为低电平;假如整数部分是奇数,只需当q0_coun≤b时q0输出高电平,当b≤q1_count≤a+b输出高电平,其他情况下q0和q1都为低电平,然后把q0和q1逻辑或所得输出f0即所需的半整数分频时钟信号。

2、仿真成果及硬件电路测验

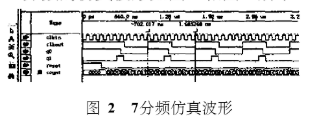

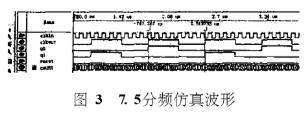

依据上面的原理,运用quartus ⅱ 4.2开发的7分频和7.5分频的仿真波形如图2和图3所示。

只需略微修正程序,即可完成恣意整数和半整数分频。

本规划在altera公司的epm7064slc84-10构成的一个数据收集体系测验经过,功能杰出。

3、结束语

本分频办法原理简略,具有必定的通用性,并且运用的cpld逻辑宏单元数较少,如在epm7064中,上面仿真的两个分频器均只用7个逻辑宏单元。

责任编辑:gt