1. 导言

在GPS接纳机的规划中,为了查验和完善信号处理算法,需求在本地取得GPS数字中频信号数据。选用实在的数据并不是最佳挑选,首要是由于其间的许多信号特色无法操控,也无法模仿不同的接纳环境和搅扰状况,这给算法的验证测验带来费事;并且存储GPS实在数据需求耗费很多的硬件资源。处理这一问题的有用办法是规划一个可以发生GPS数字中频信号并且参数可控的仿真信号源。

一般的仿真信号源规划方法被分裂为两种——纯硬件方法和纯软件方法。纯硬件方法是运用硬件器材和硬件表述直接进行规划,其规划难度大、周期长,并且体系结构规划的改动会带来巨大的硬件规划作业量。纯软件规划的仿真信号源,是运用软件言语在PC机上建立整个体系,其发生的数据需求被缓存起来以供硬件测验。这样做不只糟蹋存储资源,并且难以满意实时性要求。本文介绍了一种新的GPS中频信号源的FPGA规划计划,它是运用Xilinx System Generator for DSP东西可以主动由体系级表述转化成FPGA硬件表述的特色,完结从软件图形化规划到FPGA硬件完结的一体化流程。其长处在于,功能规划部分在MATLAB/SIMULINK下完结,信号源发生结构明晰,进行信号验证检测和参数更改;硬件完结时,经过Xilinx System Generator 东西,主动生成优化的硬件描绘言语文件和硬件测验文件,辅以Xilinx 硬件开发渠道,大大减少了直接的硬件规划作业量,缩短了从规划到完结的进程,也方便了对体系规划的批改和晋级。

2. Xilinx System Generator for DSP

Xilinx System Generator是Xilinx公司开发的FPGA辅助规划东西,包含嵌入Simulink的Xilinx 模块调集(BlockSet)和模型到硬件的转化软件。它可主动生成FPGA归纳、仿真和完结东西所需的指令文件。用户可以在图形化环境中完结体系模型的硬件开发。在规划中,System Generator将Xilinx 模块调集里的模块映射为IP(Intellectual Property)库中的模块,接着从体系参数推断出操控信号和电路,再将Simulink的分层规划转化为VHDL的分层网表,之后调用Xilinx Core Generator 和VHDL模仿、归纳完结东西来完结硬件规划,最终经过FPGA渠道完结硬件体系。这样,规划者就可以垂手可得地从一个笼统的体系级表述转化到单一来历的门级的FPGA硬件表述。这也处理了不熟悉硬件言语描绘的规划者进行硬件规划完结的问题。

3. GPS 数字中频信号源的FPGA规划

3.1 GPS数字中频信号

3.2 规划计划

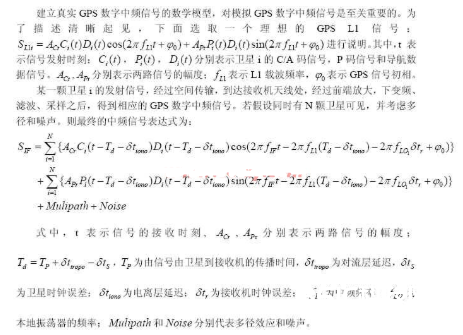

图1 GPS数字中频信号源规划计划

依据GPS数字中频信号的发生公式,咱们可以得到如图1所示的规划计划。其间每一个通道担任发生一颗特定卫星(对应一个特定的卫星PRN号)的扩频码、导航数据等信号。参数设定模块担任核算和设定各个模块的要害参数(如卫星PRN号,载波频率,码发生器的寄存器状况等),其间包含一个对应GPS时刻的Z计数器和X1计数器[3]。载波发生器是以Xilinx 模块调会集的NCO(Numerically Controlled Oscillator)模块[4]为中心建立的,其频率和相位可由参数设定模块调控。多径模块可以模仿传达进程中多径效应,计划中是经过将前端一颗或多颗卫星发生的信号经过不同的推迟加入到原信号中完结的。滤波/采样部分可以依据后续模块的不同(C/A码捕获或P码捕获),在软件规划中选用不同的参数(滤波器带宽、采样率),或在硬件完结时选用不同的硬件滤波器和采样器。下面介绍C/A码、P码发生器、设定器以及其他几个要害模块的规划计划。

3.2.1 C/A码发生器及设定器规划

GPS 的C/A码是序列长度为1023的GOLD码,码速率为1.023MHz,周期为1ms。由两个10位移位寄存器G1和G2经过异或兼并得到的,其移位多项式分别为![]() 和

和![]() 。

。

本计划中C/A码设定器可以作业于两种形式:

1)在码循环周期的初始点或半中点设定。依据待设定的方针GPS时刻对应的计数器值,换算出间隔未来最近的C/A码循环周期初始点或半中点的码片数,并用此数值设置倒计数器初值,待其计数为零时C/A码设定器将G1和G2寄存器复位到它们的初始状况或半中点状况。自此以后C/A码发生器与方针GPS时刻完结同步。该设定进程的最大推迟为511ms.

2)即时设定。本计划中对每一个寄存器位独自规划了设定单元,可以鄙人一个时钟周期到来时,将该位设定成0或1。在本作业形式中,模块需求首要换算出方针GPS时刻对应的C/A码状况索引,之后结合预存的寄存器状况表查找到G1和G2的寄存器状况,经过设定单元鄙人一个时钟周期将状况进行批改。这种形式可以完结即时同步。

3.2.2 P码发生器及设定器规划

GPS的P码是由4个具有不同特征多项式的12位移位寄存器X1A,X1B,X2A,X2B的成果兼并得到。经过译码切断、推迟、时钟操控等模块完结X1B相关于X1A,X2B相关于X2A,以及X2A/X2B相关于X1A/X1B的相位进动,然后发生周期为1.5秒的X1历元以及周期为38个星期的P码序列。经过操控 相关于 成果的推迟,到达发生不同卫星对应P码的意图。

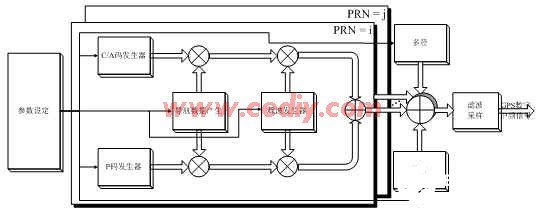

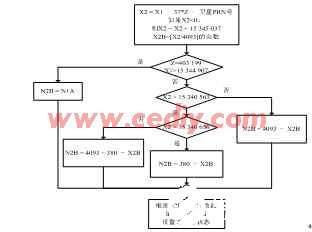

图2 X2B状况设定器作业流程图

P码设定器相关于C/A码设定器要杂乱的多,需求依据4个移位寄存器的不同状况进行不同的规划,且需求在不同的时刻复位。图2给出了咱们提出的X2B寄存器设定器的规划算法,X1A,X1B和X2A的设定器的规划思路与之相似。X1计数值,Z计数值和卫星PRN号作为输入。首要依据X1,Z计数值,核算出X2历元内的计数值X2和在一个X2B循环内的计数值X2B。假如此时刻处于一星期的X1A的最终一个循环,需求在此循环结束时对X2B进行切断。不然,依据设定时刻对应X2B寄存器的不同状况,推算出间隔下一个寄存器初始状况所需等候的P码码片数(N2B)。将此值作为计数器初值并开端倒计数,当计数为零时将X2B寄存器设置为初始状况,从此时刻开端,该寄存器的状况与方针GPS时刻到达同步。在完结该算法时,运用Xilinx 模块调会集的Mcode模块编写算法程序。此种算法完结对一切4个寄存器的同步最大推迟小于500 。相同,P 码设定器也可作业在即时设定形式下。

3.2.3导航数据模块

导航数据为50Hz的二进制码,由12.5分钟长的超帧组成,每个超帧分为25帧,每帧5个子帧,每个子帧10个字长,每个字长30bit。每帧第1,2,3播映卫星的星钟批改参数和播送星历,第4,5个子帧为历书数据、电离层批改参数及其它体系信息。计划中咱们只规划第1,2个子帧,关于其它3个子帧,咱们将NASA网站下载的24小时GPS历书数据转化为二进制比特文件,导入导航数据模块发生。第1个子帧为遥测字(TLW),其前8个比特为同步头(10001011),第9~24比特为卫星测控信息和保存位(这儿咱们都置为0),最终6比特为校验位。第二个子帧为握手字(HOW),由Z计数(对P码发生器中的X1历元个数的计数),告警标志,反诈骗标志,子帧ID,保存位和校验位组成。

在完结时,可以运用Xilinx Mcode模块,结合星历数据文件,发生仿真导航数据,也可规划成对外的输入接口,接实在导航数据或其它导航数据仿真器的输出。

3.2.4 高斯白噪声发生模块

这儿咱们需求发生限带的高斯白噪声,由于伪随机噪声具有相似于随机噪声的一些核算特性,具有随机噪声的特色,咱们选用与码发生器中相似的寄存器序列来发生伪随机m序列。又由于m序列的噪声特性与其周期长度有关,周期越长,越挨近白噪声谱,咱们这儿选用特征多项式为 的m序列发生器。若m序列的码元周期为 ,则在0~0.45/ (Hz)的范围内可以为具有均匀的功率谱。因而经过操控 可以得到所需频率范围内的模仿高斯白噪声。

4.硬件完结及运转成果

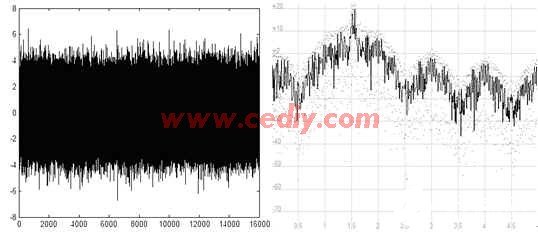

此GPS数字中频信号源的规划计划在Simulink环境中完结了图形化规划和仿真验证,并运用System Generator东西生成FPGA硬件表述文件和硬件测验文件,在Xilinx ISE环境下进行了编译和归纳,一起运用ModelSim进行了硬件仿真验证。最终将Xilinx ISE生成的位流文件下载到选用Xilinx XC2S200 芯片的FPGA硬件渠道进行了硬件体系完结和信号验证。图3给出了依据本计划规划的仿真信号源所发生的GPS数字中频信号的时域波形和功率谱(卫星PRN号为1,中频频率为15.42MHz,信噪比10dB)。经过与实践GPS中频信号及其功率谱的比照发现,二者特性是相一致的。

图3 仿真信号源发生的 GPS数字中频信号及功率谱

5.定论

文章从GPS数字中频信号源的数学模型动身,依据纯硬件和纯软件信号源规划方法的缺陷,提出了兼具软件规划灵活性和硬件规划实时高效性的GPS数字中频信号源的规划计划。计划经过多通道并行结构完结了对多颗可见卫星信号的模仿,经过码发生器和设定器完结了对恣意GPS时刻对应C/A码、P码的发生和同步,并经过多径、高斯白噪声模块模仿了信号传达进程中的多径效应和噪声环境。对卫星PRN的挑选及各个模块的要害参数进行会集核算、设定和办理,方便了参数调理、对各种效应影响的研讨以及和其他信号处理模块的协作[7]。本规划选用的依据System Generator的一体化流程,既降低了因体系批改和晋级带来的硬件规划作业量,又弥补了软件计划实时性缺乏的缺陷,这也为GPS接纳机其他模块及其他信号处理体系的规划供给了新思路。本信号源的规划和完结是GPS及其他卫星导航体系接纳机自主研发的重要组成部分,在卫星导航体系的民用产业化进程中,可以发生可观的社会效益和经济效益。

本文作者的立异点:提出了兼具软件规划灵活性和硬件规划实时高效性的GPS数字中频信号源的高效一体化FPGA规划计划。

责任编辑:gt