时序束缚和你的工程

履行东西不会企图寻觅到达最快速的布局&布线途径。——取而代之的是,履行东西会尽力到达你所希望的功能要求。

功能要求和时序束缚相关——时许束缚经过将逻辑元件放置的更近一些以缩短布线资源然后改进规划功能。

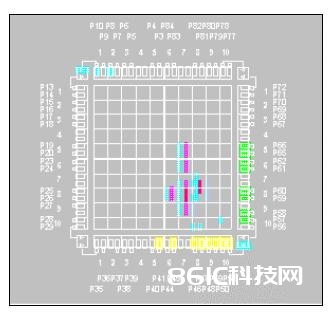

没有时序束缚的比如

该工程没有时序束缚和管脚分配

——留意它的管脚和放置

——该规划的体系时钟频率可以跑到50M

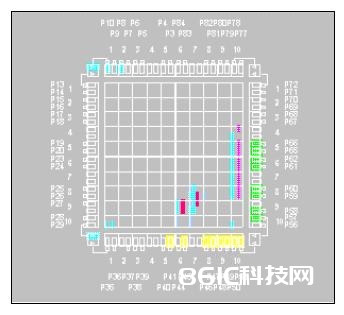

时序束缚的比如

和上面是相同的一个规划,可是加入了3个大局时序束缚。

——它最高能跑到60M的体系时钟频率

——留意它大部分的逻辑的布局更接近器材边缘其相应管脚的方位

更多关于时序束缚

时序束缚应该用于界定规划的功能方针

1. 太紧的束缚将会延伸编译时刻

2. 不实际的束缚或许导致履行东西停工

3. 检查归纳陈述或许映射后静态时序陈述以决议你的束缚是否实际

履行后,检查布局布线后静态时序陈述以决议是否你的功能要求到达了——假如束缚要求没有到达,检查时序陈述寻觅原因。

途径结尾

有两种类型的途径结尾:

1. I/O pads

2. 同步单元(触发器,锁存器,RAMs)

时序束缚的两个过程:

1. 途径结尾出产groups(望文生义便是进行分组)

2. 点拨不同groups之间的时序要求

大局束缚运用默许的途径结尾groups——即一切的触发器、I/O pads等