数字ASIC|0″>ASIC–上个世纪的黏合逻辑

上个世纪,在数字化思想主导规划范畴时,体系是规范处理器,ASSP,模仿电路和黏合逻辑的混合物。“黏合逻辑”是经过小型和中型集成电路|0″>集成电路把不同数字芯片的协议和总线连在一起。为了下降本钱完成一体化,“黏合逻辑”从前风行整个ASIC业。

现在,整个数字体系开展到深亚微米(DSM)半导体阶段,“黏合逻辑”也渐渐退出了体系规划运用。可是“黏合逻辑”真的过期了吗?答案因人而异。现在,关于数字“黏合逻辑”的需求不如曾经那么激烈,可是模仿“黏合功用”却在添加。

复合信号ASIC—今日的“体系胶连”

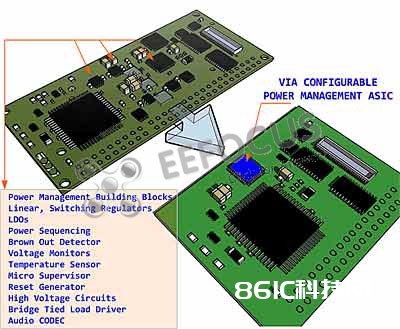

现在的体系有许多模仿功用,可是却并不合适90和65纳米硅芯片运用。这些体系需求多个电源层,若干电压等级,电源的排序,睡觉形式功耗,高电压LED驱动器,高质量音频处理器以及这些功用的智能操控。体系级芯片数字化处理计划的添加导致咱们需求复合信号集成电路,包含了许多为了节省本钱,进步功用和集成的模仿功用。如图1所示:

|

|

|

图1 : 别离的电源办理功用组合在一个可装备的集成电路上 |

便携式电子设备或许包含广泛的电源电压:用于数字集成电路的1.8V和3.3V电压,用于锂离子电池的4.2V电压,用于传统接口的5V电压,用于LED背光的36V电压,独自的用于灵敏模仿电路的电压以及用于电机操控的高电压。依据每个功率源的要求,规划师们挑选不同的电源转化拓扑结构,其间包含线性,开关以及低压降稳压器。

不仅是调节器的朴实数量在添加,这些体系往往有杂乱的电源排序要求,每个供给源彼此之间在电源开关,睡觉和下降的操作形式时的敞开和封闭需求准确的操控。一般这些供给源不只是是简略的翻开,而需求电源电压的斜升或斜降行为,然后添加了电源办理体系的额定的杂乱性。在设备的电源办理规划中,跟着调压器彼此之间的正确排序,体系复位信号,振荡器敞开和PLL安稳时刻有必要考虑进去。

一个电源办理体系集成了多种电源转化拓扑结构,数字排序逻辑,操控电源办理功用的数字通讯,模仿电压以及电流丈量;不变性回忆器用来存储电压设置点,摆放次第,序列周期和工厂校准数据。这些电源办理资源耗费了了许多电路板空间,需求多位包装,并参加到拼装本钱中,使其成为电源办理集成电路的抱负候选。这些专用集成电路建立在混合信号处理的基础上,因而相关功用不能与电源办理正常联络,比方音频处理,蜂鸣器驱动器和马达操控,在设备中成为内含物的挑选器材。关于PMIC ASIC来说,担任集成和操控许多IP模块很往常。功用如表1:

表1 PMIC 电源办理集成电路功用

线性调节器 电机操控

转化器 音频扬声器驱动

低压降稳压器 自定义数字逻辑

发光二极管升压稳压器 电源排序

电池办理-充电,监督 复位发生器

LED驱动 电压监督器

LCD电压发生器 电流监督器

电压转化器 电扇操控

音频处理 温度传感器

非易失性存储器 欠压检测器

可装备电源办理集成电路

一切的模仿和电源办理“胶连”的进入让一个单一设备完成了整合,进步了侧寻功用,下降了整个体系的本钱。但是,全定制的电源办理IC开发一贯贵重,进入市场缓慢,并且有很大的危险。

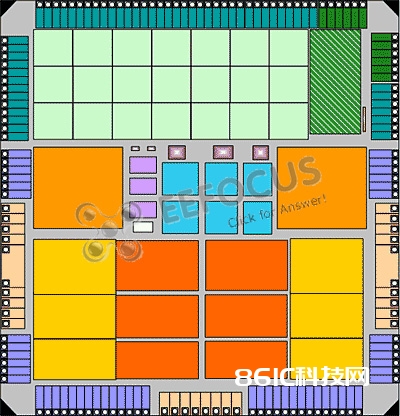

可装备阵列技能(VCA)的开展产生了硅验证的电源办理ASIC的处理计划,经过一个单一的遮罩层的改变来装备和定制特定的运用。一个VCA在ASIC模块上集成了硅验证模仿化,数字化和内存资源。然后这些资源由全体的路由结构所掩盖。包含这些VCA的晶片经过特别处理和铸造,一切的模仿和数字资源可彼此联络并由一个遮罩层来装备。因为只要一个遮罩层铸造加工,制作本钱大大下降,制作时刻从几个月到几周,硅验证的IP和互联路的运用大大下降了危险。

|

|

|

图2显现了一个可装备的PMIC和其组成部分 |

表 2 合适电源办理运用的可装备ASIC的功用

3V至50V操作

15750 个ASIC门

21,500位的RAM

1000 × 8电可擦除只读存储器,20年的数据保存才能,100K的写入周期

44个可装备数字I / O

12个20V的运算放大器与资源

12个3.3V的运算放大器与资源

6个电源办理单元

2个调节器

2个10位,1MSPS的DAC

42个可装备的模仿I / O

3.3V的独立模仿电源

20V的独立模仿电源

规划一个可装备电源办理集成电路(PMIC)

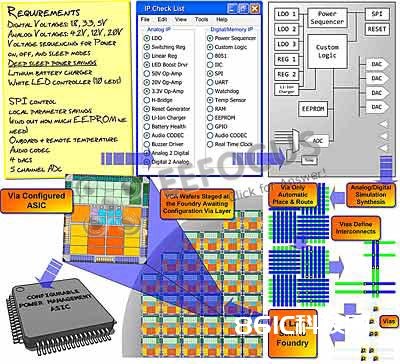

在可装备ASIC中拟定一个归纳的电源办理计划遵从图3的流程,从承认体系所需电压规模开端,每个区域所需的工作和睡觉形式的电流以及电源电压的次第。PMIC的规划意图是获取模仿图表和数字硬件描绘言语。高档其他规划用来

模仿承认设备操作。在传统的全定制ASIC规划流程中,下一步将是艰苦的,贵重的,简单犯错的晶体管布局,布局需求把规划转化到详细的硅片上。在可装备流程中,HDL格局的数字规划归纳成Verilog(现在运用最为广泛的硬件描绘言语),在门级Verliog中,软件一般把来自模仿图表的SPICE表进行转化。然后把模仿和数字Verliog网结合起来并提交给主动布局布线东西,经过大局路由结构来主动装备设备。

和全定制电源办理IC规划的数月比较,混合信号主动布局布线进程彻底装备设备只是数天。在大局路由金属层中,主动布局布线东西的输出是掩模层的一个GDSII代表。和一个全定制规划来说需求20多个层比较,这个路由层发送到铸造只需结构一个掩模层,然后大大减少了结构费用,使得原型从数月到数周成为或许。

|

|

|

图3 可装备电源办理ASIC规划流程 |

可装备ASIC供给商给规划者们供给了集成于可装备ASIC的硅验证的电源办理和混合信号IP模块。关于%&&&&&%规划来讲,“无全定制布局需求”的办法导致了低本钱,快速开展和更安全的规划流程。因而,规划团队能够处理现在产品所需的充溢挑战性的和不断改变的电源办理处理计划。

作者简介:

Reid Wender,运用工程师主管,2005年参加Triad半导体。之前,他是工程方面的副总裁,任职于QuVIs的半导体部分。他有20年的ASIC规划和项目办理经验,包含Nextwave Silicon, AS%&&&&&% International, Philips, 和IBM这些公司,并具有田纳西大学的电子工程学士学位。