一.准备常识

运用51单片机操控IO口相对来说要简略得多,最小体系建立结束后直接通过软件往各IO口写“1”或许写“0”即可。但运用STM32操控IO口输入输出却远没有这么简单,通过一个下午的查阅文献及探究后,稍微有了条理。

个人所运用的STM32F103VBT6有100个引脚,其间有五组GPIO(GPIOA…GPIOE),每组有16个GPIO端口(GPIOx_Pin0…GPIOx_Pin15)共80个,每个GPIO端口都有:

两个32位装备寄存器(GPIOx_CRL,GPIOx_CRH);

两个32位数据寄存器(GPIOx_IDR,GPIOx_ODR);

一个32方位位/复位寄存器(GPIOx_BSRR);

一个16位复位寄存器(GPIOx_BRR);

和一个32位确定寄存器(GPIOx_LCKR)。

其间各个寄存器的效果:

|

称号 |

寄存器 |

含义 |

|

端口装备寄存器 |

GPIOx_CRL GPIOx_CRH |

装备GPIO作业形式 |

|

端口输入数据寄存器 |

GPIOx_IDR |

读取GPIO输入状况 |

|

端口输出数据寄存器 |

GPIOx_ODR |

操控GPIO输出状况 |

|

端口位设置/复位寄存器 |

GPIOx_BSRR |

用于位操作GPIO的输出状况的:设置端口为0或1 |

|

端口位复位寄存器 |

GPIOx_BRR |

用于位操作GPIO的输出状况的:设置端口为0 |

|

端口装备确定寄存器 |

GPIOx_LCKR |

端口确定后下次体系复位之前将不能再更改端口位的装备 |

每个I/O端口位能够自在编程,但是I/0端口寄存器必须按32位字被拜访(不答应半字或字节拜访)。GPIOx_BSRR和GPIOx_BRR寄存器答应对任何GPIO寄存器的读/更改的独立拜访;这样,在读和更改拜访之间产生IRQ时不会产生风险。

输入数据寄存器(GPIOx_IDR)在每个APB2时钟周期捕捉I/O引脚上的数据。因而,要操控GPIOC端口,必须先使能APB2时钟。此外,STM32初始化外设第一步便是敞开APB时钟。(时钟部分常识暂时知道该如此,往后再学习。)

关于GPIO各寄存器的描绘:

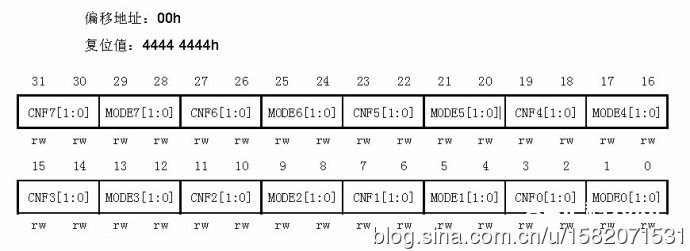

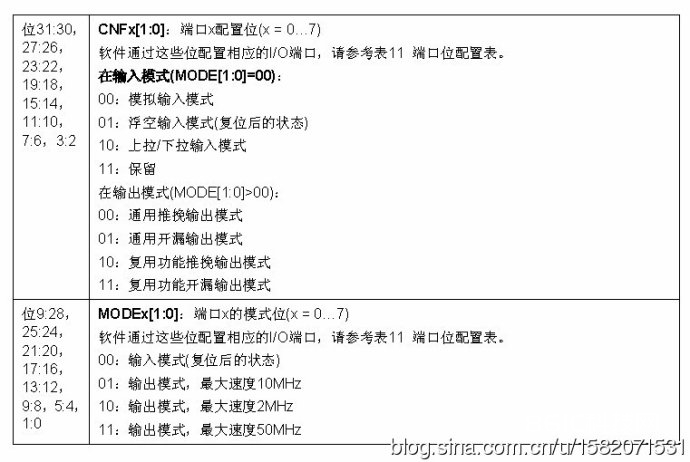

端口装备低寄存器(GPIOx_CRL) (x=A..E):

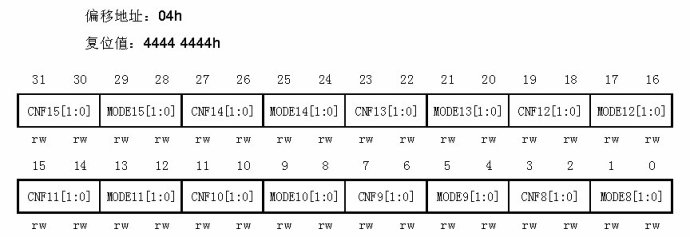

端口装备高寄存器(GPIOx_CRH) (x=A..E):