公司的产品是根据MSP430F5418开发的,在程序的调试进程中遇到过一些问题,现总结如下。

1)UCS

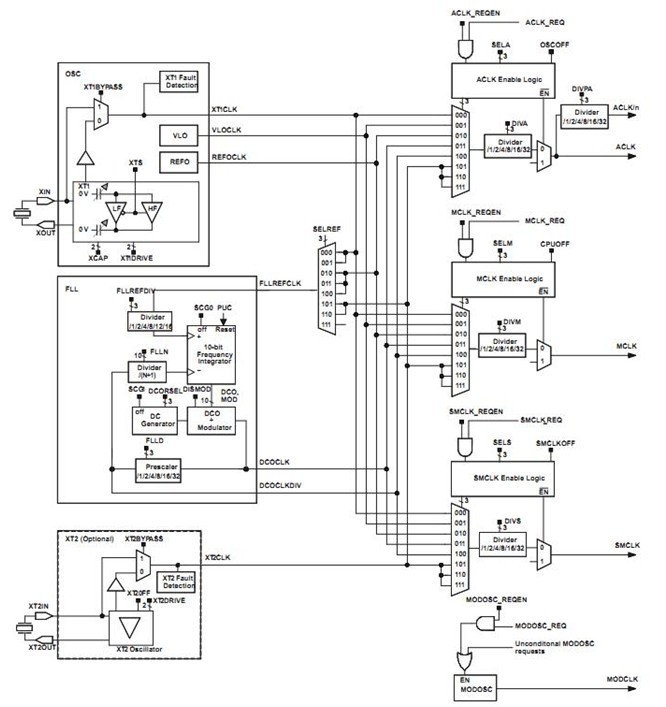

时钟好像处理器的心脏,每一个周期便是心脏的一次脉动。曾经运用其他处理器时,只需求挑选适宜频率的晶体,接在XT1和XT2两头,再加两个电容就能够了。而MSP430F5418的时钟体系略显杂乱,简单让刚开始触摸它的人一头雾水。5418的时钟设置由UCS(Unified Clock System)来办理,运用起来比较灵敏,其结构如图

所示。

UCS模块有XT1CLK和XT2CLK两个外部时钟源,以及VLOCLK、REFOCLK和DCOCLK(DCOCLKDIV是DCOCLK的分频输出)三个内部时钟源。其间XT1CLK、REFOCLK和XT2CLK能够作为FLLREFCLK输入到FLL单元来改动DCO的输出。所有这些时钟源经分频后都能够作为MCLK、SMCLK和ACLK输出。

下面是一个UCS设置的比如,运用32768Hz的内部时钟源REFOCLK,并经过FLL倍频使MCLK为16.384MHz。

void UCS_Init(void)

{

UCSCTL3 |= SELREF__REFOCLK; //选取REFOCLK作为FLLREFCLK

__bis_SR_register(SCG0); //制止FLL

UCSCTL0 = 0x0000;

UCSCTL1 = DCORSEL_6;

UCSCTL2 = FLLD_1 + 499;//将REFOCLK 500倍频到16.384MHz

__bic_SR_register(SCG0); //使能FLL

UCSCTL5 |= DIVS__32; // SMCLK 32分频后输出

UCSCTL4 |= SELA__REFOCLK; //选取REFOCLK为ACLK

do

{//铲除时钟过错标志位

UCSCTL7 &= ~(XT2OFFG + XT1LFOFFG + XT1HFOFFG + DCOFFG);

SFRIFG1 &= ~OFIFG; //铲除时钟过错中止标志

} while (SFRIFG1 & OFIFG); //等候时钟安稳

}

2)SPI

在进行SPI接口的设置时,假如处理器作为主器材,那么必定要根据从器材的时序确认正确的时钟相位和时钟极性。假如使能了SPI的发送中止,需求留意的一点是,在发送第一个字节来发动整个发送进程时,该字节的发送不是瞬间的,需求等候必定的时刻,以UCB1为例即:

UCB1TXBUF = data;

while (UCB1STAT & UCBUSY); //等候data发送完毕

3)UART

经过串口调试帮手向UART发送数据时,假如使能了接纳中止,那么每接纳一个字符都会触发一次中止,两次中止之间程序是会回到主程序持续履行的。怎么判别接纳数据的完毕?一种办法是固定指令的长度,以长度来界定;另一种更常用的办法是规划必定的通信协议来针对不定长的指令,如把每个指令都封装成帧,给其加上特定的帧头、帧尾。

4)RTC

MSP430F5418的RTC在日历形式下存在BUG,直接对日期及时刻寄存器赋值经常会不成功。处理的办法是读写日期和时刻寄存器时运用TI公司在RTC_Workaround中给出的例程。

5)其他

规划中应尽量防止中止嵌套,中止服务程序中的代码量尽量少。