摘要:近年来,自习惯均衡技能在通讯体系中的运用日益广泛,运用自习惯均衡技能在多径环境中可以有效地进步数字接收机的功用。为了习惯宽带数字接收机的高速率特色,本文论述了自习惯均衡器的原理并对其进行改善。最终运用FPGA芯片和Verilog HDL规划完结了自习惯均衡器并仿真验证了新办法的有效性。

信道均衡技能(Channel equalization)是指为了进步式微信道中的通讯体系的传输功用而采纳的一种抗式微办法。它首要是减小信道的多径时延带来的码间串扰(ISI)问题。其原理是对信道或整个传输体系特性进行补偿,然后到达体系传输的要求。在实践的通讯体系中,信道的特性是不知道的并且是不抱负的,传统的均衡器无法满意体系的要求,自习惯均衡器直接从传输的信号中,依据某种算法不断调整体系中滤波器的增益,来习惯信道的随机改动,然后有更好的失真补偿功用,使均衡器总是坚持最佳的作业状况。FPGA以其处理速度快、开发周期短、可重复修正、开发东西智能、支撑并行处理等长处成为现代通讯范畴硬件规划的首选办法之一。依据FPGA完结的自习惯均衡器可以更好地习惯当时通讯的开展要求,具有更宽广的运用远景。

最小均方差错算法(LMS)是较常用的一种完结自习惯均衡器的算法,也是FPGA完结自习惯均衡器的最抱负的算法,所以本文挑选运用LMS算法规划均衡器。本文所规划的自习惯均衡器是宽带数字接收机的一部分,为了满意宽带体系的高速率,实时性的特色,在算法规划,对LMS算法进行必定的改善。

1 LMS算法根本原理

LMS算法是依据最小均方差原则的维纳滤波器和最速下降法(method of steepest descent)提出的,其公式如下:

y(n)=uT(n)w(n) (1)

e(n)=d(n)-y(n) (2)

w(n+1)=w(n)+2μe(n)u(n) (3)

d(n)为希望输入信号,e(n)为差错,其间μ为步长因子,用以操控收敛速度与稳定性,LMS算法收敛的条件为:0

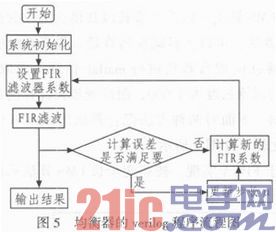

LMS算法的根本过程如下:

过程1,初始化w(0)=0,n=0;挑选μ;

过程2,依据式(2)(3)核算差错e(n)和w(n+1);

过程3,若差错不满意要求,更新n=n+1,重复过程2,若满意要求则中止迭代。

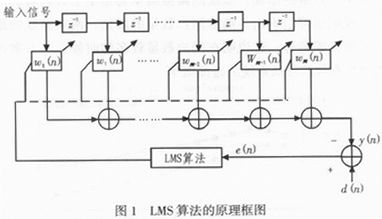

下图为最小均方差错算法的原理框图。

2 LMS算法改善

在宽带体系中,数据量大,速率快,因此对均衡器的处理速度要求高,签于此本文把变步长LMS算法和符号LMS算法结合在一起,以满意上述要求。

步长因子μ操控着算法的收敛速度和稳定性,当μ较大时收敛速度快,稳定性较差,μ较小,稳定性好,收敛速度慢。变步长LMS算法可以统筹收敛速度和稳定性两个方面。一种变步长算法的公式为:

μ(n)=β[1-exp(-α|e(n)|2)] (4)

α、β为参数。由上式看到跟着差错的减小,步长因子也在减小,稳定性添加。

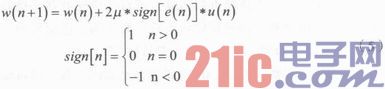

公式(3)中,咱们看到,每次迭代都会运用乘法器,运算量较大。符号LMS算法对公式(3)中的差错e(n)进行缩放,每次迭代可削减运用一次乘法器,公式如下:

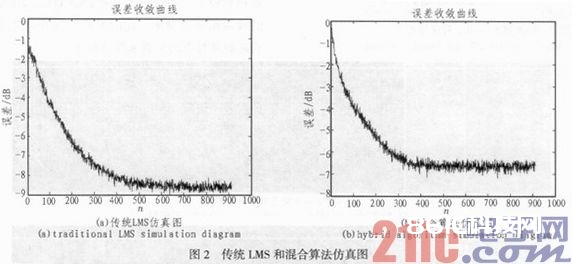

由公式(5)可以看出,符号LMS算法会丢失必定的精度。变步长LMS算法可以改动步长以取得快的收敛速度,结合符号LMS算法,可以很多削减运算量,进步体系的功率。本文对两种算法的混合算法进行matlab仿真,选取64阶均衡器,数据的练习长度为1 000,盯梢变步长核算的参数挑选α=4,β=1/128。下面临两种办法混合算法用matlab仿真,并和传统算法比较,如图2所示。

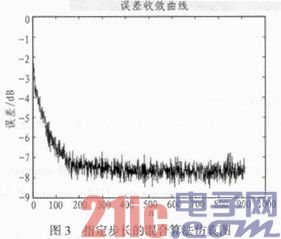

为了便于FPGA完结,依照变步长LMS算法思维,本文不在对变步长LMS算法中步长μ进行盯梢核算,而是指定步长收敛之前为0.02,收敛之后步长0.15,其他参数不变,运用Matlab仿真,如图3所示。

从图中咱们看到混合算法的差错比传统算法有所增大,但是在迭代300次后趋于稳定,比传统算法削减200次,因此混合算法更能满意实时性的要求。

图3中,因为收敛之前步长且不随差错的减小而减小(迭代次数为200),所以收敛速度更快;收敛之后步长较小,均匀的稳态差错比混合算法有所减小。

3 依据FPGA自习惯均衡器的完结

由仿真可知,咱们提出的混合算法可以满意规划自习惯均衡器的要求。本章将依据此算法的用FPGA完结自习惯均衡器。

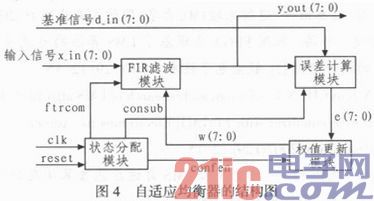

选用FPGA规划LMS自习惯均衡器的结构图如图4所示。它首要分为FIR滤波器模块、差错核算模块、权值更新模块和状况分配模块4个单元。

文中为了便利完结,FIR滤波器模块完结18阶的FIR滤波。差错核算模块中的基准信号d(k)事前可存在ROM里。权值更新部分完结FIR滤波器系数的核算与调整,设定收敛之前μ=2-4,收敛之后μ=2-6。

状况分配模块功用包含初始化各模块,它产生操控信号、操控完结各个模块完结特定功用;和谐各个模块间的操作。

因为FPGA不支撑浮点数运算,而自习惯滤波器必定要涉及到小数的核算,因此咱们将一切小数化为二进制处理。本文规划选用4..4格局,第一位为符号位。

依据以上参数,依照LMS原理以及结构图,咱们即可编写程序,主程序流程图如图5所示。

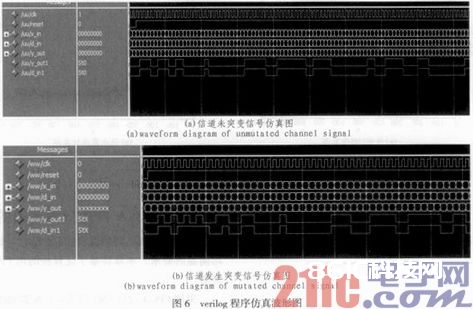

文中选用xilinx公司的ISE12.4为开发东西,Modelsim为仿真东西。为了便于比较,咱们将输出信号和希望信号进行判定。仿真成果如下。

图6(a)中信道无搅扰,可以看出输出信号和希望信号共同;若信道产生骤变,如图6(b)所示,在阅历一段时刻后均很器可以消除码间搅扰。经过仿真,可以得到:依据混合算法的自习惯均衡器可以消除码间串扰,可以快速地从多径信号中康复动身送信号,削减误码。

4 定论

文中改善了LMS算法原理,运用FPGA完结了自习惯均衡器,从仿真成果来看,选用FPGA完结自习惯均衡器彻底可满意规划要求,依据改善型算法可取得较高的数据处理速度。鉴于时刻和本文篇幅较小,规划中FIR滤波器的阶数选取相对较小,并且引进符号LMS算法,因此对白习惯均衡器的收敛精度会带来必定的影响,但可以经过添加FIR滤波器的阶数和数据的位数来进步精度。