意法半导体(纽约证券交易所代码:STM)推出全新微处理器架构SPEAr1300,新架构将被用于意法半导体针对高功用网络和嵌入式使用研制并深受商场欢迎的全新SPEAr®(结构化处理器增强型架构)嵌入式微处理器产品系列。

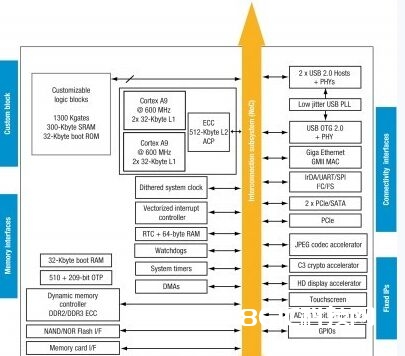

凭仗在制作SPEAr300和SPEAr600产品线上堆集的经历,全新SPEAr1300整合功用强壮的双核ARM Cortex-A9处理器和 DDR3内存接口,采意图法半导体的低功耗55nm HCMOS(高速CMOS)制程。双核ARM Cortex-A9处理器支撑全对称运转,处理速度高达600MHz/核,相当于3000 DMIPS。 SPEAr1300利意图法半导体的创新片上网络技术完成内部外设的互连功用,可支撑多个不同的流量协议,以最具本钱效益和能效的方法,最大极限地进步数据吞吐量。第一批样片已供给应相关客户并开端进行使用规划。

SPEAr1300除了具本钱效益和用户订制的优势外,更具有业界抢先的DMIPS/MHz和功耗/DMIPS比率。新架构集成DDR3 内存控制器和全套的外设接口,如PCIe、SATA、USB以及以太网等功用,使SPEAr1300成为高功用使用的抱负挑选,包含网络、瘦客户机、视频会议终端设备、网络存储器(NAS)、计算机外设和工厂自动化。 意法半导体计算机体系SoC产品部总经理Loris Valenti表明:“这款全新SPEAr产品架构根据具有无与伦比的低功耗和多处理器功用的ARM Cortex-A9处理器内核。行将上市的SPEAr嵌入式微处理器针对下一代网络家电的要求,完成史无前例的处理功用、存储吞吐量、使用灵活性以及低功耗。”全新SPEAr1300架构的首要特性:• 双ARM Cortex-A9内核,运转频率 600MHz,相当于3000 DMIPS

• 64位AXI(AMBA3)总线片上网络技术

• 具有过错校验码(ECC)的DRAM 和 L2高速缓存

• 具有ECC功用的533MHz 32位DDR3存储器控制器;一起支撑16位DDR2

• 加速器一致性端口(ACP)

• 千兆以太网接口

• PCIe 2.0接口,支撑 5 GT/s (每秒传输千兆次)

• SATA II 3 Gbit/s

• USB 2.0

• 256位密钥硬件加密/解密

• 130万门可装备逻辑阵列 全新SPEAr1300产品线将于几个月后将推出嵌入式微处理器,进一步扩粗心法半导体的SPEAr产品系列,为客户供给更多的产品挑选。