能够仿制上一个实例cy4ex7的整个工程文件夹,更名为cy4ex8。然后在Quartus II中翻开这个新的工程。

Cyclone IV的PLL输入一个时钟信号,最多能够发生5个输出时钟,输出的频率和相位都是能够在必定范围内调整的。

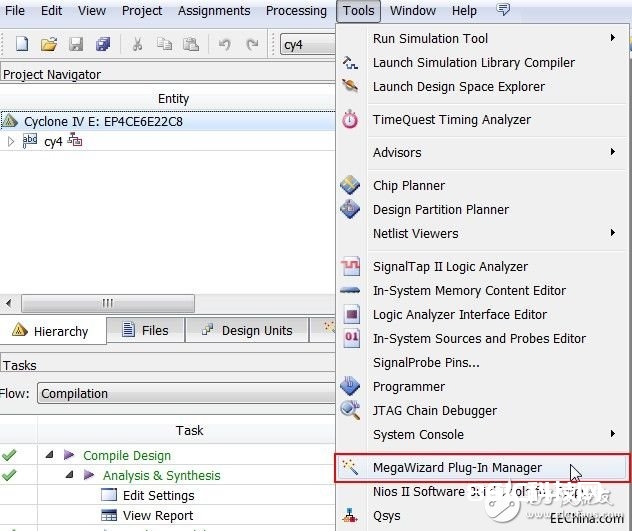

下面咱们来看本实例怎么装备一个PLL硬核IP,并将其集成到工程中。如图8.18所示,在新建的工程中,点击菜单“ToolsàMegaWizard Plug-In Manager”。

图8.18MegaWizard菜单

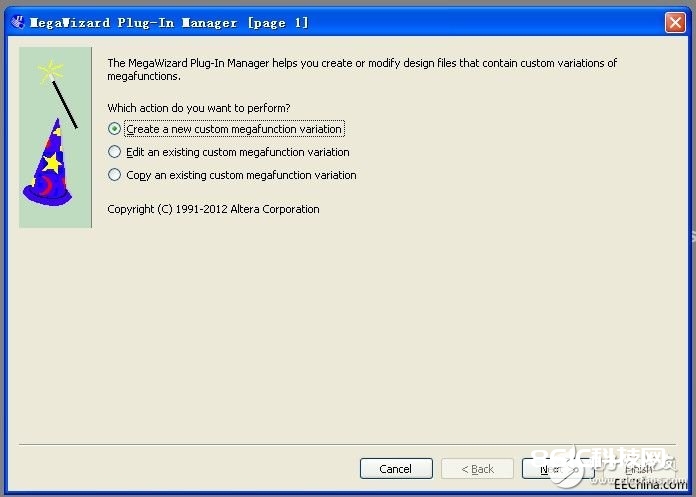

如图8.19所示,挑选“Creat a new custommegafuncTIon variaTIon”,然后点击Next。

图8.19 新建IP核导游

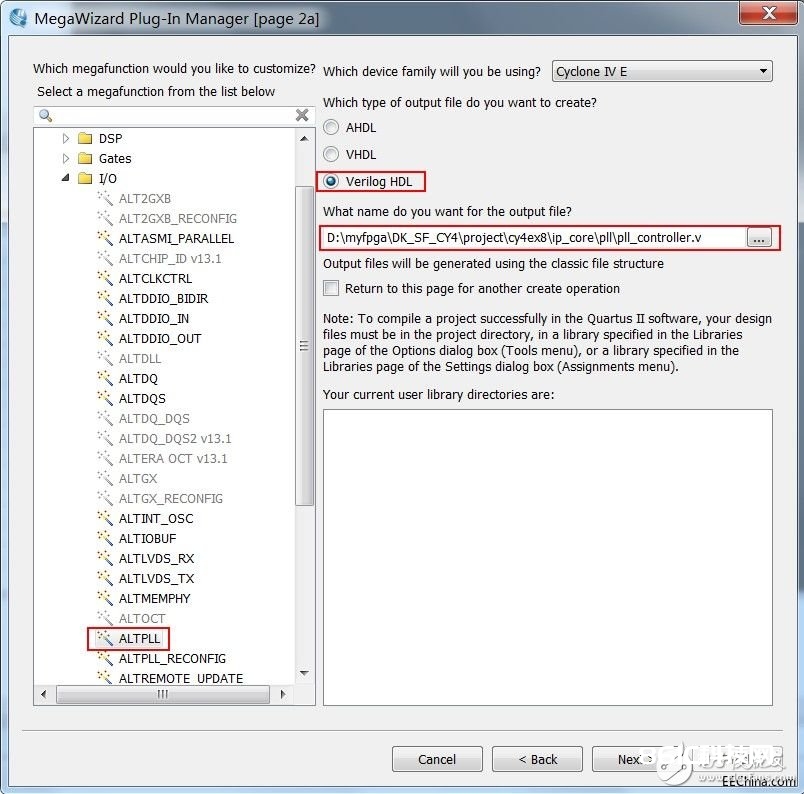

接着挑选咱们所需求的IP核,如图8.20所示进行设置。

● 在“Select a megafuncTIon from the list below”下面挑选IP核为“I/O à ALTPLL”。

● 在“What device family will you be using”后边的下拉栏中挑选咱们所运用的器材系列为“Cyclone IV E”。

● 在“What type of output file do you want to create?”下面挑选言语为“Verilog”。

● 在“What name do you want for the output file?”下面输入工程地点的途径,而且在最终边加上一个称号,这个称号是咱们现在正在例化的PLL模块的称号,咱们能够给他起名叫pll_controller,然后点击Next进入下一个页面。这儿它地点的途径,实际上是咱们在工程文件夹cy4ex8下面创立的ip_core文件夹和其下的pll文件夹。

图8.20 挑选ALTPLL为IP核

接着来到了PLL的参数装备页面,如图8.21所示进行设置。然后点击Next进入下一个页面。

● 在“What device speed grade will you be using?”后边挑选“8”,即咱们运用的器材的速度等级。

● 在“What is the frequency of the inclk0 input?”后边挑选“25MHz”,即咱们输入到该PLL的基准时钟频率。

图8.21 PLL的General装备页面

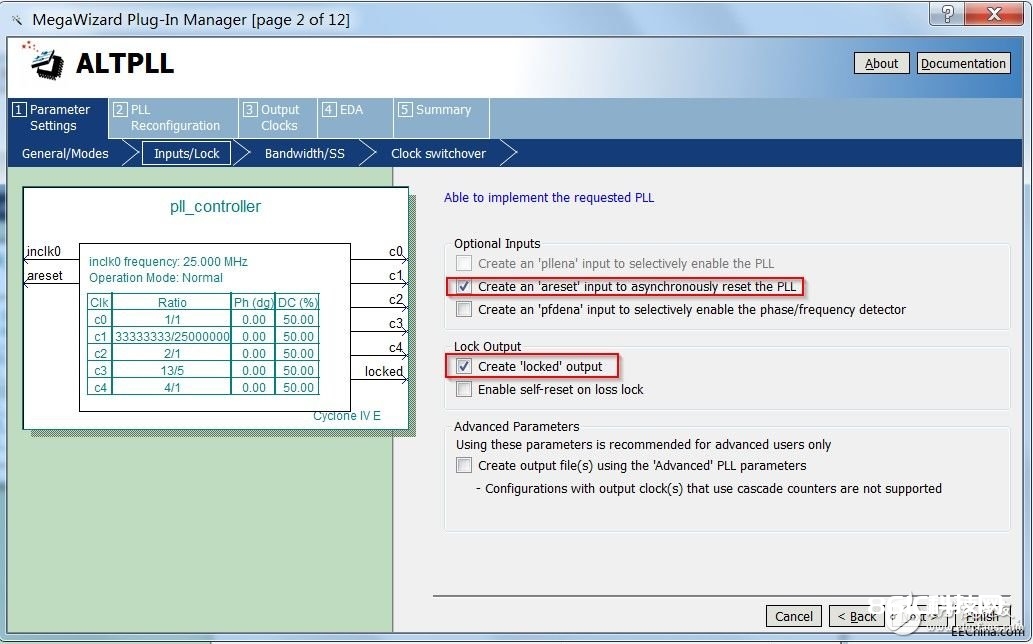

Input/lock页面中,如图8.22所示进行设置,接着点击Next进入下一个页面。

● 勾选“Create an ‘areset’ input to asynchronously reset the PLL”,即引出该PLL硬核的’areset’信号,这是该PLL硬核的异步复位信号,高电平有用。

● 勾选“Create ‘locked’ output”,即引出该PLL硬核的’locked’信号,该信号用于指示PLL是否完结内部初始化,现已能够正常输出了高电平有用。

图8.22 PLL的input/lock装备页面

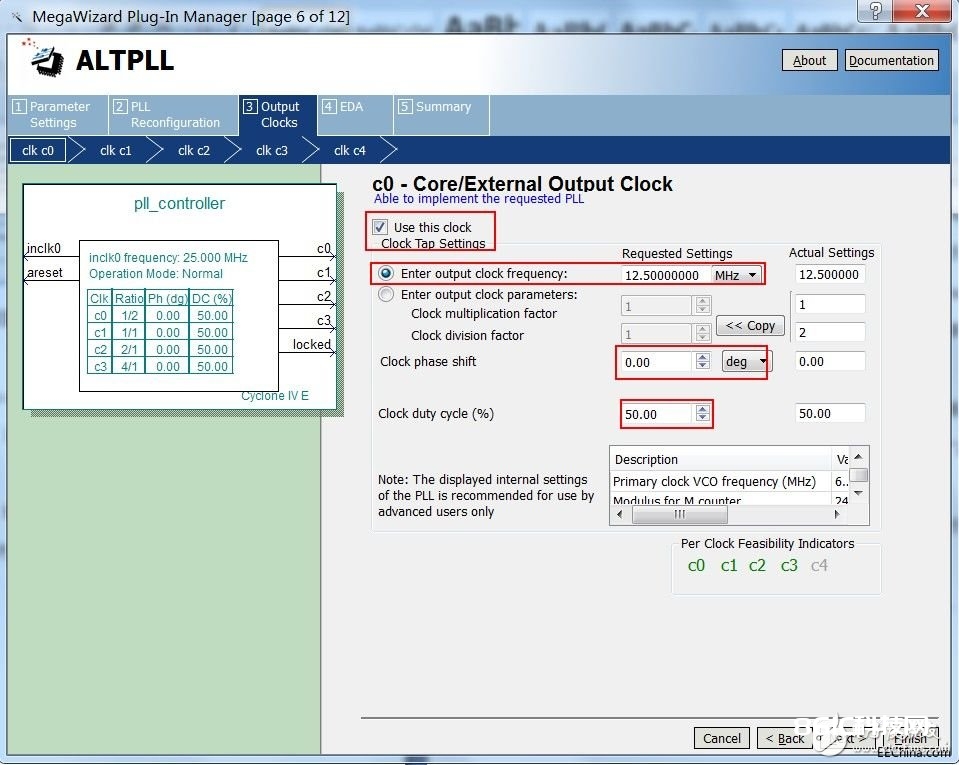

Bandwidth/SS、Clock Switchover和PLLReconfiguraTIon页面不必设置,默许即可。直接进入OuputClocks页面,如图8.23所示,这儿有5个可选的时钟输出通道,经过勾选对应通道下方的Usethis clock选项敞开对应的时钟输出通道。能够在装备页面中设置输出时钟的频率、相位和占空比。这儿是 C0通道的设置。

● 勾选“Use this clock”,表明运用该时钟输出信号。

● 输入“Enter output clock frequency”为“12.5MHz”,表明该通道输出的时钟频率为12.5MHz。

● 输入“Clock phase shift”为“0 deg”,表明该通道输出的时钟相位为0 deg。

● 输入“Clock duty cycle(%)”为“50.00%”,表明该通道输出的时钟占空比为50%。

图8.23 PLL的clk c0装备页面

和C0的装备相同,咱们能够别离敞开而且装备C1、C2、C3,这些时钟尽管这个例程暂时用不上,可是后续的例程将会运用到。

● C1的时钟频率为25MHz,相位为0deg,占空比为50%。

● C2的时钟频率为50MHz,相位为0deg,占空比为50%。

● C3的时钟频率为100MHz,相位为0deg,占空比为50%。

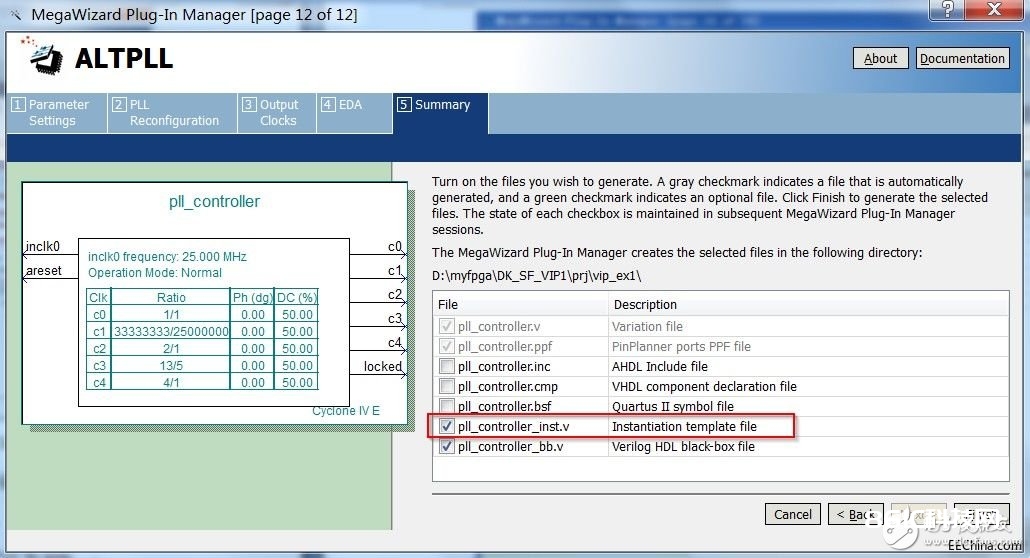

装备完结后,最终在Summary页面,如图8.24所示,勾选上*_inst.v文件,这是一个PLL例化的模板文件,一会咱们能够在工程目录下找到这个文件,然后翻开它,将它的代码仿制到工程中,修正对应接口即可完结这个IP核的集成。

图8.24 PLL的Summary装备页面

点击Finish完结PLL的装备。工程中若弹出如图8.25所示的对话框,勾选“Automaticallyadd Quartus II IP Files to all projects”选项后,点击Yes。

图8.25 增加IP核文件到工程

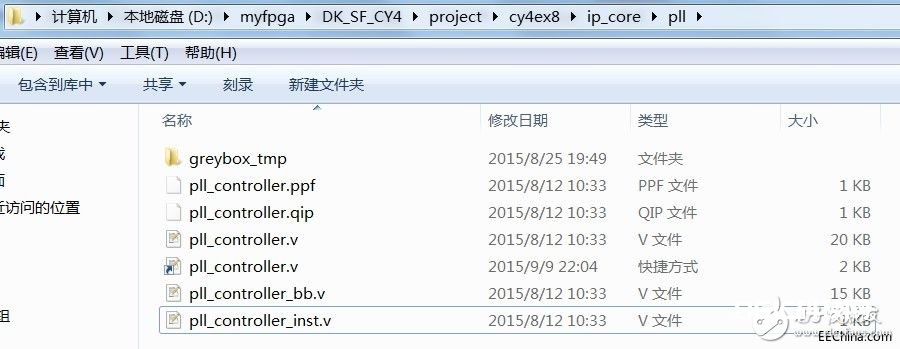

此刻,咱们能够来到pll文件夹下,如图8.26所示,翻开pll_controller_inst.v文件,它是这个PLL IP核的例化模板。

图8.26 PLL IP核生成文件

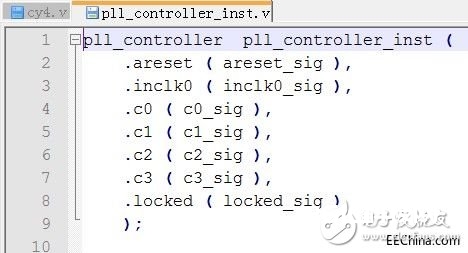

pll_controller_inst.v如图8.27所示。仿制文件中的内容,将()内的信号名改为咱们连接到这个模块的接口信号名就能够了。

图8.27 PLL IP核例化模板