1 布景常识

跟着网络技能的开展,网络带宽不断增大,体系处理网络协议开支越来越大。以太网具有易于集成、低本钱以及传输间隔远等特色,越来越多的通讯设备需求接入到以太网扩展网络功用以完结长途操控和愈加高效的数据传输,根据TCP/IP协议的运用越来越多。FPGA等可编程逻辑器件的快速开展使得以太网协议传输越来越快,跟着新技能的不断开展,完结TCP/IP协议栈技能水平越来越高,根据FPGA操控嵌入式以太网协议处理运用越来越遍及。

W5500是一款多功用的全硬件以太网接口芯片,内部集成有10/100M以太网操控器,嵌入了TCP卸载引擎(TCP Offload Engine:TOE),且集成有32K发送缓存区和接纳缓存区存储用于数据传输。无需考虑协议内部各层联系,不触及操作体系,只需求正确装备就能够完结网络衔接,接口电路简略、编程灵敏便利。

本规划从本钱操控和完结周期来考虑,选用了以W5500芯片作为TCP/IP协议栈进行传输体系的规划和完结。

2 体系规划

2.1 TOE技能

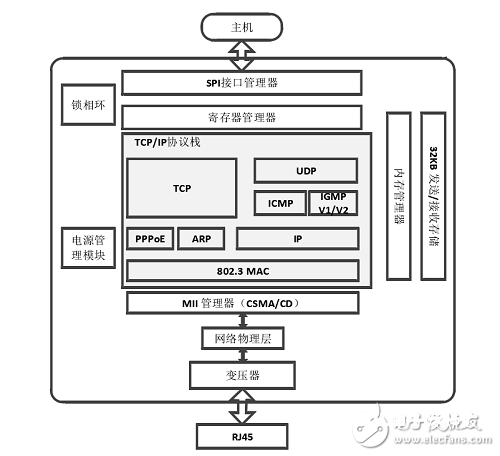

选用TOE技能,即以太网卸载引擎技能,其完结方法是将TCP协议数据包从主机CPU转移到包括TOE功用的网卡,让TOE网卡处理TCP协议数据量,然后进步服务器功用。TOE方法不需进行软件协议栈移植,开发周期缩短,CPU担负下降,安稳功用进步。其处理方法框图如下图1所示。

图 1 TOE方法进行TCP/IP协议栈处理

2.2 W5500以太网操控器

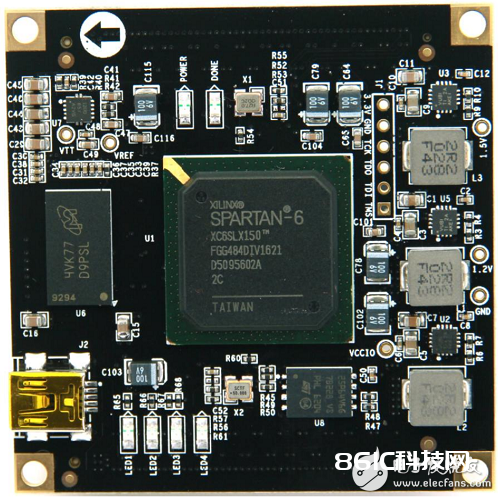

W5500芯片首要经过Socket编程进行协议通讯,共有8个可供运用,选用SPI传输协议进行各个寄存器的参数装备,最高数据传输速率可达80MHz。W5500的内部功用框图,如下图2所示。

图 2 W5500的内部功用方框图

2.3 体系程序规划

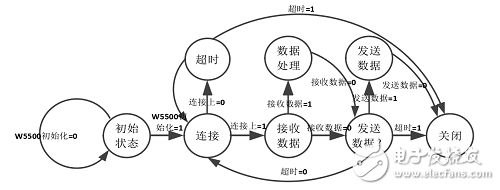

本规划中FPGA选用Xilinx公司的Spartan6系列的XC6SLX150-2FG484C芯片。这款高功用中心板,具有高速,高带宽,高容量等特色。该中心板硬件实物图如下图3所示。

图 3 中心板硬件实物图

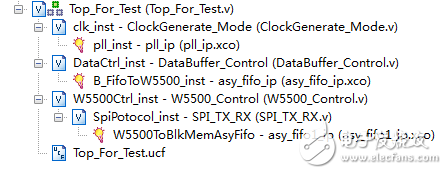

经过规划FPGA程序操控W5500作为服务器方法,等候上位机衔接,经三次衔接握手成功后,便可进行TCP/IP协议的数据传输。TCP协议通讯状态机如图4所示。

图 4 TCP状态机的FPGA完结

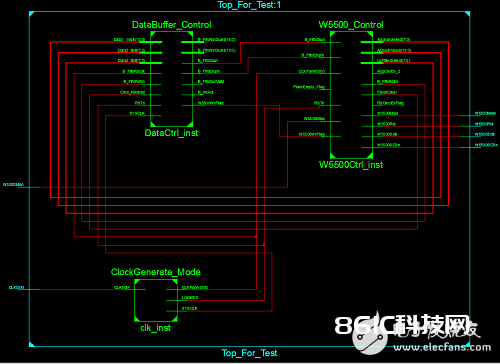

选用模块化、自顶向下的方法进行FPGA程序规划,即顶层Top模块作为总控部分,下一层分为时钟生成、数据操控和W5500操控三大模块,即如下图5所示的Verilog程序工程结构图。其间,数据操控模块首要处理、缓存与W5500模块的接纳和发送的数据;W5500操控模块选用SPI方法完结FPGA对W5500芯片寄存器的操控。

图 5 W5500的程序规划结构图

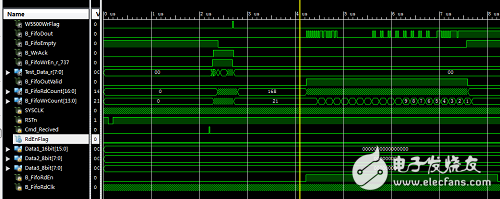

对规划的Verilog程序进行仿真测验,得到如下图6所示的成果。可见,经过W5500模块的数据接纳和发送功用均完结。

图 6 W5500模块功用仿真验证图

得到的顶层综RTL原理图如下图7所示。

图 7 W5500模块顶层归纳RTL图

2.4 体系测验

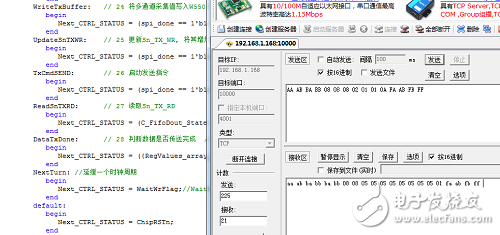

本体系的规划,将下位机(FPGA和W5500)作为服务器,上位机选用测验软件“TCP&UDP测验东西”作为客户端。

将程序装备到FPGA中,首要敞开下位机的服务器方法,等候客户端的衔接。然后打来测验软件,设置好要衔接的IP地址(即服务器IP)和端口号,树立客户端并衔接。衔接成功后,便开端TCP/IP协议传输测验,经过发送对应的指令数据,服务器接纳到指令后,进行数据解析处理和操控,并将成果数据发送回客服端(PC端)。

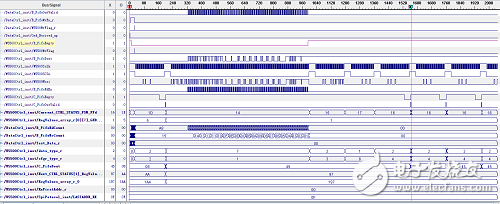

在程序规划过程中,运用开发软件ISE中的ChipScope功用,能够明晰地观测各个信号的改变状况,以测验程序规划的正确性,及便于找出问题。规划完结的ChipScope在线抓数据成果如下图8所示,可实时观测数据与指令的联系和改变状况。

图 8 W5500数据抓取归纳测验成果

得到对应的实测成果如下图9所示,验证了以TCP/IP协议方法的数据发送和接纳功用的完结。

图 9 W5500功用实测成果图

3 结语

本体系完结了根据FPGA的,选用嵌入式以太网W5500芯片以硬件方法完结的TCP/IP协议栈,进步了CPU的处理功率,而且使得通讯速率在很大程度上得到了进步,为以太网数据传输体系的规划供给了一种有用的方法。