引 言

跟着规划杂乱度的添加,运用IP核已经成为一种常用的规划办法。QuartusⅡ软件供给的Megafunt-tions是依据Altera底层硬件结构最合理的老练运用模块,在代码中运用MegafuncTIons这类IP资源,不光能将规划者从繁琐的代码编写中摆脱出来,更重要的是,在大多数情况下MegafuncTIons的归纳和完结成果比用户编写的代码更优。并且只需要简略地设置选取宏功用模块的相关参数就能够在程序中调用它们,因而宏功用模块的运用也非常便利。QuartusⅡ的Mega-funcTIns中包括有算术运算(ArithmeTIc)、逻辑门(Gates)、I/O、存贮器(Storage)等四个系列,能够依据体系规划需求灵敏选用。

在实时图画处理中,用Sobel算子进行物体的边际检测是常常用到的算法,因为对处理速度要求较高,因而用纯软件的办法很难到达要求。而FPGA对一起可完结的处理使命简直没有约束,合适高速、并行信号处理,并且FPGA密度高、容量大,有内置存储器、简单完结,所以FPGA广泛用于实时图画处理体系中。

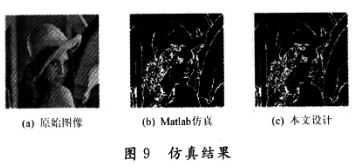

在此经过调用依据RAM的移位寄存器altshifttaps、可编程乘加器altmult add、可编程多路并行加法器parallel_add和参数化绝对值运算模块lpm_abs,完结了依据FPGA的Sobel边际检测。终究给出规划体系的仿真成果,经过与Matlab仿真成果相比较,能够看出该规划取得了很好的边际检测作用。

1 Sobel边际检测算法

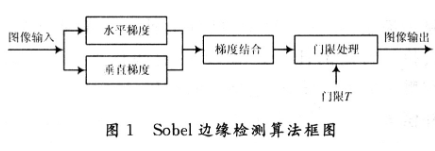

图1给出了Sobel边际检测算法框图。从图中能够看出对一副图画进行Sobel边际检测时首先要运用Sobel算子核算出水平梯度和笔直梯度,然后再把两个方向的梯度结合起来,终究运用门限处理模块判别图画边际并输出边际检测成果。

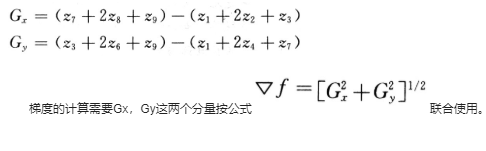

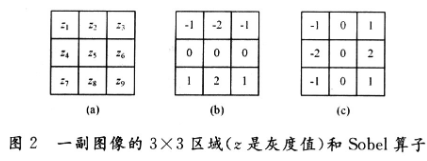

图2(a)为一副图画的3×3区域,图2(b)和图2(c)别离为Sobel算子的x方向(笔直方向)梯度算子和y方向(水平方向)梯度算子。当选用Sobel算子对图2(a)所示的3×3区域做梯度核算时,可得符号为z5的像素点x方向梯度和y方向的梯度重量别离为:但是实践执行时,为了运算便利能够选用公式

f△|Gx|+|Gy|对梯度进行近似。

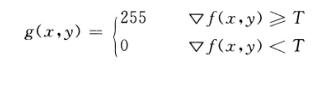

该规划在门限处理时,选用根本大局门限:当某像素点(x,y)的梯度值XXXXf(x,y)大于或等于设定的门限T时,规则该点的灰度值为255,反之则为0。即:

2 Sobel边际检测的硬件完结

依据图1所示的Sobel边际检测算法框图,可得FPGA硬件完结Sobel边际检测时应该包括梯度核算模块和门限处理模块。此外在硬件完结时还要选用图画数据缓冲模块对图画做缓冲处理,以便进一步对图画数据做模板处理。门限处理模块能够经过编写VerilogHDL代码完结。以下首要介绍图画数据缓冲模块和梯度核算模块。

2.1 图画数据缓冲模块器

在图画的空域滤波中,为了得到3×3的方形模板窗,常运用FIFO(First In First Out)模块作为图画数据的缓冲器。这儿经过运用依据RAM的移位寄存器宏模块altshift taps完结了相同的功用,并且还省去了一些操控信号,运用非常便利。

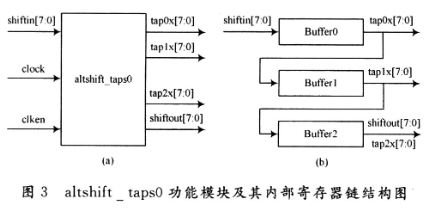

altshift_taps宏功用模块是一个可装备的、具有抽头(Taps)输出的移位寄存器,每个抽头在移位寄存器链的指定方位输出数据。图3(a)和图3(b)别离为定制的8位输入/8位输出、3抽头,且相邻两个抽头相距256个寄存器的altshift_taps0功用模块及其内部寄存器链结构图,图3(b)中的Buffer0,Buffer1,Buffer2别离为由256个8位移位寄存器构成的寄存器链。当图画的第N行数据在像素时钟同步下从shiftin[7:0]端输入到altshift_taps0的Buffer0后,跟着第N+1行图画数据输入到Buffer0中,第N行的图画数据顺次存入Buffer1中,而当第N十2行图画数据存入Buffer0后,Buffer1和Buffer2中别离寄存的是第N+1行和第N行的图画数据,然后完结缓冲图画数据的功用。这样在像素时钟的同步下,第N+2,N+1,N行的同一列数据别离从tap0x[7:0],taplx[7:0],tap2x[7:0]端输出给梯度核算模块,进行梯度核算。

2.2 梯度核算模块

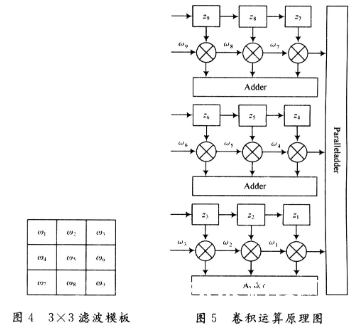

Sobel边际检测中,图画像素点梯度的核算可由So-bel算子与图画像素卷积运算的输出经梯度核算公式核算取得。图5是图4所示的3×3空间滤波模板与图2(a)所示的3×3图画区域卷积运算的原理图。从中能够看出,为了完结卷积运算需要做乘法和加法运算,之前的文献中大都选用分立的D触发器和加法器以及乘法器来完结卷积运算,它的结构杂乱。在此选用可编程乘加器altmult_add模块和可编程多路并行加法器par-allel_add模块完结卷积运算,大大简化了规划。

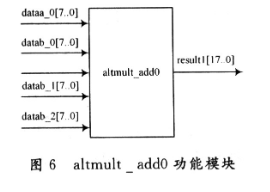

可编程乘加器altmult_and能够接纳多组数据输入,各组数据相乘后相加或相减作为成果输出。并且altmult_add在运用时能够依据需要设置乘法器个数、输入/输出数据格式、流水线操控时钟等参数,一起它还支撑输入数据内部移位功用。

运用可编程多路并行加法器parallel_add模块时,用户能够自在规划输入数据位宽,累加数据个数,界说累加输入数据类型,模块终究主动生成恰当位宽的数据输出。并且运用parallel_add模块做加法运算时,能够经过指定时钟延时以完结流水线规划,然后改进电路的功用,进步整个体系的作业频率。

图6为完结梯度核算而定制的altmult_add0模块,该乘加器包括3个乘法器,1个加法器并且为了改进电路的功用和进步体系的作业频率,在该模块中运用了寄存器。一起因为该模块运用了数据的内部移位功用,当某行的图画数据从dataa_0[7:0]顺次输入时,经过3个时钟周期后,相邻的3个数据别离与固定的模板系数datab_0,datab_1,datab_2相乘,并将成果送给加法器完结加法运算。当选用三个这样相似的altmult_add模块并联时,便可完结卷积运算,而当卷积模板选用Sobel算子时,就能够取得像素点的水平梯度和笔直梯度。

在取得Gx和Gy后,还要经过公式 才能够核算出对应像素点的梯度值。规划中能够运用QuartusⅡ供给的lpm_abs宏功用模块完结绝对值的核算。

才能够核算出对应像素点的梯度值。规划中能够运用QuartusⅡ供给的lpm_abs宏功用模块完结绝对值的核算。

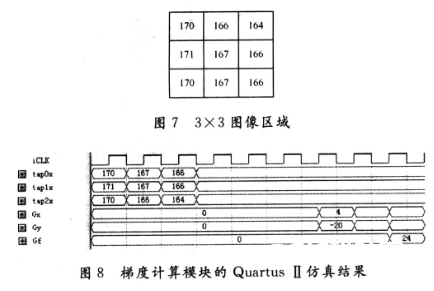

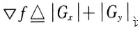

图7为3×3图画区域,图8是依据altmult_add模块、parallel_add模块和lpm_abs模块构建的梯度核算模块对进行Sobel算子处理的QuartusⅡ仿真成果。因为选用了流水线规划,在第7个时钟的上升沿从Gx端,Gy端别离输出有用的x方向和y方向梯度值,并在第9个时钟的上升沿从Gf端输出图7的中心像素点的梯度,这个仿真成果与运用公式 核算出的梯度值彻底相同。

核算出的梯度值彻底相同。

3 仿真成果

为了愈加直观地验证该体系的边际检测作用,在体系功用验证时选用Matlab和Modelsim进行混合仿真,仿真成果如图9所示。图9(a)为一幅256×256的原始图画,图9(b)为设定门限T为125的Matlab程序对原始图画的Sobel边际检测成果。图9(c)为该规划的Sobel边际检测成果。比较图9(b)和图9(c),能够看出该规划得到的成果简直与Matlab的仿真成果彻底相同,即该规划取得了很好的边际检测作用。

4 结 语

该规划运用QuartusⅡ软件供给的可编程乘加器altmult_add模块、可编程多路并行加法器parallel_add模块和绝对值核算模块lpm_abs,及运用VerilogHDL规划的门限处理模块和其他相应的操控模块,完结依据FPGA的Sobel边际检测的硬件规划。该办法既避免了自己编写很多程序代码的繁琐,又取得很好的归纳和完结成果。终究经过与Matlab的仿真成果相比较证明了本规划能够有用地完结Sobel边际检测。

责任编辑:gt