1. verilog完成根本门电路

verilog完成反相器,2输入与门、2输入或门、2输入与非门、2输入或非门、2输入异或门、2输入同或门;

编撰仿真程序,对完成进行仿真测验;

将仿真后的verilog代码进行归纳与完成,并下载到basys3上验证;

2. verilog完成2选1MUX

编撰仿真程序,对其进行测验;

将仿真后的verilog代码进行归纳与完成,并下载到basys3上验证;

2.

led[0] sw[0] sw[1]完成2输入与门

led[2] sw[2] sw[3]完成2输入或门

led[4] sw[4] sw[5]完成2输入与非门

led[6] sw[6] sw[7]完成2输入或非门

led[8] sw[8] sw[9]完成2输入异或门

led[10] sw[10] sw[11]完成2输入同或门

led[12] sw[12]完成反相器

led[13] sw[13] sw[14] sw[15]完成2选1MUX

3.完成模块

module fpga001(

input [15:0] sw,

output [13:0] led

);

assign led[0] = sw[0] & sw[1];

assign led[2] = sw[2] | sw[3];

assign led[4] = ~(sw[4] & sw[5]);

assign led[6] = ~(sw[6] | sw[7]);

assign led[8] = (sw[8] & (~sw[9])) | (~sw[8] & sw[9]);

assign led[10] = ~((sw[10] & (~sw[11])) | (~sw[10] & sw[11]));

assign led[12] = ~sw[12];

assign led[13] = ~sw[13] & sw[14] | sw[13] & sw[15];

endmodule

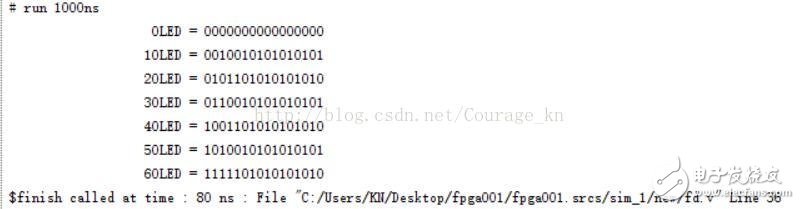

4.测验模块

module fd;

reg[15:0] w;

wire[13:0] l;

fpga001 f(w, l);

iniTIal

begin

w = 16‘b0;

#10 w = 16’b0010010101010101;

#10 w = 16‘b0101101010101010;

#10 w = 16’b0110010101010101;

#10 w = 16‘b1001101010101010;

#10 w = 16’b1010010101010101;

#10 w = 16‘b1111101010101010;

#20 $finish;

end

iniTIal

begin

$monitor($TIme, “LED = %b”, w);

end

endmodule

5.引脚分布图

## This file is a general .xdc for the Basys3 rev B board

## To use it in a project:

## – uncomment the lines corresponding to used pins

## – rename the used ports (in each line, after get_ports) according to the top level signal names in the project

## Clock signal

#set_property PACKAGE_PIN W5 [get_ports clk]

#set_property IOSTANDARD LVCMOS33 [get_ports clk]

#create_clock -add -name sys_clk_pin -period 10.00 -waveform {0 5} [get_ports clk]

## Switches

set_property PACKAGE_PIN V17 [get_ports {sw[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sw[0]}]

set_property PACKAGE_PIN V16 [get_ports {sw[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sw[1]}]

set_property PACKAGE_PIN W16 [get_ports {sw[2]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sw[2]}]

set_property PACKAGE_PIN W17 [get_ports {sw[3]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sw[3]}]

set_property PACKAGE_PIN W15 [get_ports {sw[4]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sw[4]}]

set_property PACKAGE_PIN V15 [get_ports {sw[5]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sw[5]}]

set_property PACKAGE_PIN W14 [get_ports {sw[6]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sw[6]}]

set_property PACKAGE_PIN W13 [get_ports {sw[7]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sw[7]}]

set_property PACKAGE_PIN V2 [get_ports {sw[8]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sw[8]}]

set_property PACKAGE_PIN T3 [get_ports {sw[9]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sw[9]}]

set_property PACKAGE_PIN T2 [get_ports {sw[10]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sw[10]}]

set_property PACKAGE_PIN R3 [get_ports {sw[11]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sw[11]}]

set_property PACKAGE_PIN W2 [get_ports {sw[12]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sw[12]}]

set_property PACKAGE_PIN U1 [get_ports {sw[13]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sw[13]}]

set_property PACKAGE_PIN T1 [get_ports {sw[14]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sw[14]}]

set_property PACKAGE_PIN R2 [get_ports {sw[15]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sw[15]}]

## LEDs

set_property PACKAGE_PIN U16 [get_ports {led[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[0]}]

set_property PACKAGE_PIN E19 [get_ports {led[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[1]}]

set_property PACKAGE_PIN U19 [get_ports {led[2]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[2]}]

set_property PACKAGE_PIN V19 [get_ports {led[3]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[3]}]

set_property PACKAGE_PIN W18 [get_ports {led[4]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[4]}]

set_property PACKAGE_PIN U15 [get_ports {led[5]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[5]}]

set_property PACKAGE_PIN U14 [get_ports {led[6]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[6]}]

set_property PACKAGE_PIN V14 [get_ports {led[7]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[7]}]

set_property PACKAGE_PIN V13 [get_ports {led[8]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[8]}]

set_property PACKAGE_PIN V3 [get_ports {led[9]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[9]}]

set_property PACKAGE_PIN W3 [get_ports {led[10]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[10]}]

set_property PACKAGE_PIN U3 [get_ports {led[11]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[11]}]

set_property PACKAGE_PIN P3 [get_ports {led[12]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[12]}]

set_property PACKAGE_PIN N3 [get_ports {led[13]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[13]}]

set_property PACKAGE_PIN P1 [get_ports {led[14]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[14]}]

set_property PACKAGE_PIN L1 [get_ports {led[15]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[15]}]

##7 segment display

#set_property PACKAGE_PIN W7 [get_ports {seg[0]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {seg[0]}]

#set_property PACKAGE_PIN W6 [get_ports {seg[1]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {seg[1]}]

#set_property PACKAGE_PIN U8 [get_ports {seg[2]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {seg[2]}]

#set_property PACKAGE_PIN V8 [get_ports {seg[3]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {seg[3]}]

#set_property PACKAGE_PIN U5 [get_ports {seg[4]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {seg[4]}]

#set_property PACKAGE_PIN V5 [get_ports {seg[5]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {seg[5]}]

#set_property PACKAGE_PIN U7 [get_ports {seg[6]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {seg[6]}]

#set_property PACKAGE_PIN V7 [get_ports dp]

#set_property IOSTANDARD LVCMOS33 [get_ports dp]

#set_property PACKAGE_PIN U2 [get_ports {an[0]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {an[0]}]

#set_property PACKAGE_PIN U4 [get_ports {an[1]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {an[1]}]

#set_property PACKAGE_PIN V4 [get_ports {an[2]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {an[2]}]

#set_property PACKAGE_PIN W4 [get_ports {an[3]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {an[3]}]

##Buttons

#set_property PACKAGE_PIN U18 [get_ports btnC]

#set_property IOSTANDARD LVCMOS33 [get_ports btnC]

#set_property PACKAGE_PIN T18 [get_ports btnU]

#set_property IOSTANDARD LVCMOS33 [get_ports btnU]

#set_property PACKAGE_PIN W19 [get_ports btnL]

#set_property IOSTANDARD LVCMOS33 [get_ports btnL]

#set_property PACKAGE_PIN T17 [get_ports btnR]

#set_property IOSTANDARD LVCMOS33 [get_ports btnR]

#set_property PACKAGE_PIN U17 [get_ports btnD]

#set_property IOSTANDARD LVCMOS33 [get_ports btnD]

##Pmod Header JA

##Sch name = JA1

#set_property PACKAGE_PIN J1 [get_ports {JA[0]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {JA[0]}]

##Sch name = JA2

#set_property PACKAGE_PIN L2 [get_ports {JA[1]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {JA[1]}]

##Sch name = JA3

#set_property PACKAGE_PIN J2 [get_ports {JA[2]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {JA[2]}]

##Sch name = JA4

#set_property PACKAGE_PIN G2 [get_ports {JA[3]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {JA[3]}]

##Sch name = JA7

#set_property PACKAGE_PIN H1 [get_ports {JA[4]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {JA[4]}]

##Sch name = JA8

#set_property PACKAGE_PIN K2 [get_ports {JA[5]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {JA[5]}]

##Sch name = JA9

#set_property PACKAGE_PIN H2 [get_ports {JA[6]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {JA[6]}]

##Sch name = JA10

#set_property PACKAGE_PIN G3 [get_ports {JA[7]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {JA[7]}]

##Pmod Header JB

##Sch name = JB1

#set_property PACKAGE_PIN A14 [get_ports {JB[0]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {JB[0]}]

##Sch name = JB2

#set_property PACKAGE_PIN A16 [get_ports {JB[1]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {JB[1]}]

##Sch name = JB3

#set_property PACKAGE_PIN B15 [get_ports {JB[2]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {JB[2]}]

##Sch name = JB4

#set_property PACKAGE_PIN B16 [get_ports {JB[3]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {JB[3]}]

##Sch name = JB7

#set_property PACKAGE_PIN A15 [get_ports {JB[4]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {JB[4]}]

##Sch name = JB8

#set_property PACKAGE_PIN A17 [get_ports {JB[5]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {JB[5]}]

##Sch name = JB9

#set_property PACKAGE_PIN C15 [get_ports {JB[6]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {JB[6]}]

##Sch name = JB10

#set_property PACKAGE_PIN C16 [get_ports {JB[7]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {JB[7]}]

##Pmod Header JC

##Sch name = JC1

#set_property PACKAGE_PIN K17 [get_ports {JC[0]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {JC[0]}]

##Sch name = JC2

#set_property PACKAGE_PIN M18 [get_ports {JC[1]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {JC[1]}]

##Sch name = JC3

#set_property PACKAGE_PIN N17 [get_ports {JC[2]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {JC[2]}]

##Sch name = JC4

#set_property PACKAGE_PIN P18 [get_ports {JC[3]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {JC[3]}]

##Sch name = JC7

#set_property PACKAGE_PIN L17 [get_ports {JC[4]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {JC[4]}]

##Sch name = JC8

#set_property PACKAGE_PIN M19 [get_ports {JC[5]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {JC[5]}]

##Sch name = JC9

#set_property PACKAGE_PIN P17 [get_ports {JC[6]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {JC[6]}]

##Sch name = JC10

#set_property PACKAGE_PIN R18 [get_ports {JC[7]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {JC[7]}]

##Pmod Header JXADC

##Sch name = XA1_P

#set_property PACKAGE_PIN J3 [get_ports {JXADC[0]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {JXADC[0]}]

##Sch name = XA2_P

#set_property PACKAGE_PIN L3 [get_ports {JXADC[1]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {JXADC[1]}]

##Sch name = XA3_P

#set_property PACKAGE_PIN M2 [get_ports {JXADC[2]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {JXADC[2]}]

##Sch name = XA4_P

#set_property PACKAGE_PIN N2 [get_ports {JXADC[3]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {JXADC[3]}]

##Sch name = XA1_N

#set_property PACKAGE_PIN K3 [get_ports {JXADC[4]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {JXADC[4]}]

##Sch name = XA2_N

#set_property PACKAGE_PIN M3 [get_ports {JXADC[5]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {JXADC[5]}]

##Sch name = XA3_N

#set_property PACKAGE_PIN M1 [get_ports {JXADC[6]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {JXADC[6]}]

##Sch name = XA4_N

#set_property PACKAGE_PIN N1 [get_ports {JXADC[7]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {JXADC[7]}]

##VGA Connector

#set_property PACKAGE_PIN G19 [get_ports {vgaRed[0]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {vgaRed[0]}]

#set_property PACKAGE_PIN H19 [get_ports {vgaRed[1]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {vgaRed[1]}]

#set_property PACKAGE_PIN J19 [get_ports {vgaRed[2]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {vgaRed[2]}]

#set_property PACKAGE_PIN N19 [get_ports {vgaRed[3]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {vgaRed[3]}]

#set_property PACKAGE_PIN N18 [get_ports {vgaBlue[0]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {vgaBlue[0]}]

#set_property PACKAGE_PIN L18 [get_ports {vgaBlue[1]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {vgaBlue[1]}]

#set_property PACKAGE_PIN K18 [get_ports {vgaBlue[2]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {vgaBlue[2]}]

#set_property PACKAGE_PIN J18 [get_ports {vgaBlue[3]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {vgaBlue[3]}]

#set_property PACKAGE_PIN J17 [get_ports {vgaGreen[0]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {vgaGreen[0]}]

#set_property PACKAGE_PIN H17 [get_ports {vgaGreen[1]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {vgaGreen[1]}]

#set_property PACKAGE_PIN G17 [get_ports {vgaGreen[2]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {vgaGreen[2]}]

#set_property PACKAGE_PIN D17 [get_ports {vgaGreen[3]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {vgaGreen[3]}]

#set_property PACKAGE_PIN P19 [get_ports Hsync]

#set_property IOSTANDARD LVCMOS33 [get_ports Hsync]

#set_property PACKAGE_PIN R19 [get_ports Vsync]

#set_property IOSTANDARD LVCMOS33 [get_ports Vsync]

##USB-RS232 Interface

#set_property PACKAGE_PIN B18 [get_ports RsRx]

#set_property IOSTANDARD LVCMOS33 [get_ports RsRx]

#set_property PACKAGE_PIN A18 [get_ports RsTx]

#set_property IOSTANDARD LVCMOS33 [get_ports RsTx]

##USB HID (PS/2)

#set_property PACKAGE_PIN C17 [get_ports PS2Clk]

#set_property IOSTANDARD LVCMOS33 [get_ports PS2Clk]

#set_property PULLUP true [get_ports PS2Clk]

#set_property PACKAGE_PIN B17 [get_ports PS2Data]

#set_property IOSTANDARD LVCMOS33 [get_ports PS2Data]

#set_property PULLUP true [get_ports PS2Data]

##Quad SPI Flash

##Note that CCLK_0 cannot be placed in 7 series devices. You can access it using the

##STARTUPE2 primiTIve.

#set_property PACKAGE_PIN D18 [get_ports {QspiDB[0]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {QspiDB[0]}]

#set_property PACKAGE_PIN D19 [get_ports {QspiDB[1]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {QspiDB[1]}]

#set_property PACKAGE_PIN G18 [get_ports {QspiDB[2]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {QspiDB[2]}]

#set_property PACKAGE_PIN F18 [get_ports {QspiDB[3]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {QspiDB[3]}]

#set_property PACKAGE_PIN K19 [get_ports QspiCSn]

#set_property IOSTANDARD LVCMOS33 [get_ports QspiCSn]