1 导言

数字信息在有噪信道中传输时,会遭到噪声搅扰的影响,误码总是不可避免的。为了在已知信噪比的状况下到达必定的误码率目标,在合理规划基带信号,挑选调制、解调办法,并选用频域均衡或时域均衡办法的基础上,还应选用过失操控编码等信道编码技能,使误码率进一步下降。卷积码和分组码是过失操控编码的2种首要办法,在编码器复杂度相同的状况下,卷积码的功用优于分组码,因而卷积码简直被运用在一切无线通信的规范之中,如GSM ,IS95和CDMA2000的规范中。

现在,VHDL言语已成为EDA范畴首选的硬件规划言语,越来越多的数字体系规划运用 VHDL言语来完结。原因是经过VHDL描绘的硬件体系“软核”便于存档,程序模块的移植和AS C规划源程序的交给更为便利。因而,他在IP核的运用等方面担任着不可或缺的人物。在某扩频通信体系中,咱们运用VHDL言语规划了(2,1,6)卷积码编解码器,并经过了在FPGA芯片上的验证试验。

2 卷积编码器

卷积码一般记作(n0,k0,m),其编码功率为k0/n0,m称为束缚长度。(n0 ,k0,m)卷积码可用k0个输入、n0个输出、输入存储为m的线性有限状况移位存放器及模2加法计数器电路来完结,卷积码的编码办法有3种运算办法:离散卷积法;生成矩阵法;多项式乘积法。此外,卷积码的编码进程还可以用状况图、码树图和网格图来描绘。本文规划的编码器考虑到硬件电路的完结,挑选了多项式乘积法。本体系所选卷积编码器如图1所示,该卷积编码器为(2,1,6)自正交卷积编码器。

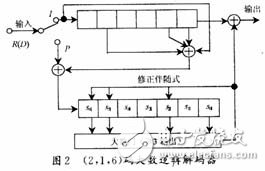

3 大数逻辑解码器

卷积码的解码可分为代数解码与概率解码2类。大数逻辑解码器是代数解码最首要的解码办法,他既可用于纠正随机过错,又可用于纠正突发过错,但要求卷积码是自正交码或可正交码。 本文所选(2,1,6)体系自正交卷积码的大数逻辑解码器如图2所示。

图2中,I端输入信息码元,P端输入校验码元。解码器把接收到的R(D)中的每一段信息元送入编码器中求出本地查验元,与其后边收到的查验元模2加。若两者共同,则求出的随同式重量si为0,否则为1。把加得的值送入随同式存放器中存放。当接收完7个码段后开端对第 0码段纠错,若此刻大数逻辑门的输出为1,则阐明第0码 段的信息元有错。这时正好第0子组的信息元移至解码器的输出端,然后纠正他们。一起,纠错信号也反应至随同式 存放器批改随同式,以消去此过错对随同式的影响。假如大数判定门没有输出,则阐明第0子组的信息元没有过错,这时从编码器中直接把信息元输出 。

4卷积码编解码器的VHDL规划

4.1VHDL规划的长处与规划办法

与传统的自底向上的规划办法不同,VHDL规划是从体系的整体要求动身,选用自顶向下( toptodown)的规划办法。其程序结构特点是将一项工程 规划(或称规划实体),分红外部(即端口)和内部(即功用、算法)。在对一个规划实体界说了外部端口后,一旦内部开发完结,其他的规划就可以直接调用这个实体。

本规划所用VHDL规划渠道是Altera的MAX+PlusⅡ EDA软件。MAX+PlusⅡ界面友爱,运用快捷;他支撑VHDL,原理图,V言语文本文件,以及波形与EDIF等格局的文件作为规划输入;并支撑这些文件的恣意混合规划;具有门级仿真器,可以进行功用仿真和时序仿真,可以发生精确地仿真成果;支撑除APEX20K,APXⅡ,Mercury,Excalibur和Stratix系列之外的一切Altera FPGA/CPLD大规模逻辑器材。规划中选用的FPGA器材是Altera的FLEX系列芯片FLEX 10K20。用MAX+PlusⅡ软件进行VHDL规划的进程是:

(1)用Text Editor编写VHDL程序。

(2)用Compiler编译VHDL程序。

(3)用Waveform Editor,Simulater仿真验证VHDL程序。

(4)用TIming Analyzer进行芯片的时序剖析。

(5)用Floorplan Editor组织芯片管脚方位。

(6)用Programer下载程序至芯片FLEX10K20。

在实践的开发进程中,以上个过程需重复进行,直至将既定的VHDL规划经过一切的测验停止 。

4.2卷积编码器VHDL顶层建模(top level)及体系 功用仿真

4.2.1卷积编码器各功用模块及顶层建模端口的VHDL描绘

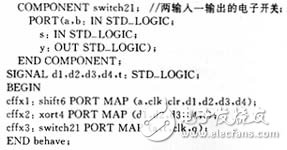

LIBRARY IEEE;

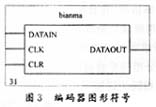

用MAX+PlusⅡ编译后生成的编码器图形符号如图3所示。

4.2.2卷积编码器VHDL顶层建模的VHDL仿真波形

卷积编码器VHDL仿真波形如图4所示。仿真前设置输入信息序列datain=“1111”,速率为32 kP/s,对应时钟为31. 25μs。仿真成果表明,卷积编码输出dataout =“1111101 0010000000001”,相应速率为64 kP/s,与理论剖析成果共同。

4.3卷积解码器VHDL顶层建模的VHDL端口描绘

4.3.1卷积解码器各功用模块及顶层建模端口的VHDL描绘

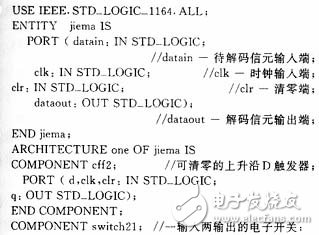

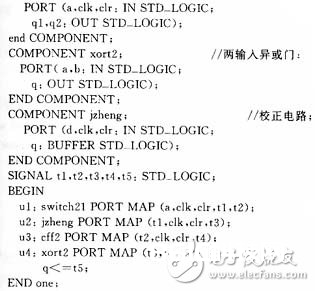

LIBRARY IEEE;

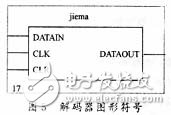

用MAX+PlusⅡ编译后生成的解码器图形符号如图5所示。

4.3.2卷积解码器VHDL顶层建模的VHDL仿真波形

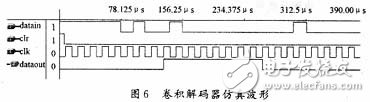

卷积解码器VHDL仿真波形如图6所示。其间待解码信元datain=“11111010010000000001” ,速率为64kP/s,对应时钟为15.625μs。仿真成果表明,解码信元输出dataout =“111 1”,相应速率为32kP/s。实践仿真还验证了当卷积解码器输入的待解码信元中有错码时的纠错状况,与理论剖析成果共同。

5结语

将经过仿真的VHDL程序下载到FPGA芯片FLEX10K20上,并在实践扩频体系中用于过失操控 ,取得了较为满足的作用。