首要小编就几个要害技能再给咱们介绍一下。

差分时钟技能

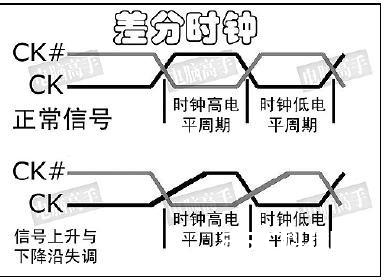

差分时钟是DDR的一个重要且必要的规划,但咱们对CK#(CKN)的效果知道很少,很多人理解为第二个触发时钟,其实它的实在效果是起到触发时钟校准的效果。

因为数据是在CK的上下沿触发,构成传输周期缩短了一半,因而必需求确保传输周期的安稳以确保数据的正确传输,这就要求CK的上下沿距离要有准确的操控。但因为温度、电阻功用的改动等原因,CK上下沿距离或许发生变化,此刻与其反相的CK#(CKN)就起到纠正的效果(CK上升快下降慢,CK#则是上升慢下降快),如下图一所示。

图一 差分时钟暗示图

数据选取脉冲(DQS)

就像时钟信号相同,DQS也是DDR中的重要功用,它的功用首要用来在一个时钟周期内准确的差异出每个传输周期,并便于接纳方准确接纳数据。每一颗8bit DRAM芯片都有一个DQS信号线,它是双向的,在写入时它用来传送由主控芯片发来的DQS信号,读取时,则由DRAM芯片生成DQS向主控发送。彻底能够说,它便是数据的同步信号。

在读取时,DQS与数据信号一起生成(也是在CK与CK#的交叉点)。而DDR内存中的CL也便是从CAS宣布到DQS生成的距离,数据真实呈现在数据I/O总线上相关于DQS触发的时刻距离被称为tAC。实践上,DQS生成时,芯片内部的预取现已结束了,因为预取的原因,实践的数据传出或许会提早于DQS发生(数据提早于DQS传出)。因为是并行传输,DDR内存对tAC也有必定的要求,关于DDR266,tAC的答应规模是±0.75ns,关于DDR333,则是±0.7ns,其间CL里包含了一段DQS的导入期。

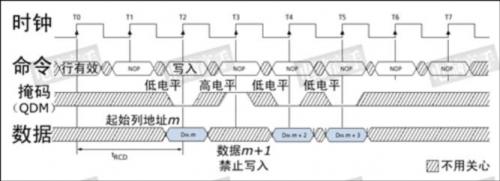

DQS 在读取时与数据同步传输,那么接纳时也是以DQS的上下沿为准吗?不,假如以DQS的上下沿差异数据周期的风险很大。因为芯片有预取的操作,所以输出时的同步很难操控,只能约束在必定的时刻规模内,数据在各I/O端口的呈现时刻或许有快有慢,会与DQS有必定的距离,这也便是为什么要有一个tAC规则的原因。而在接纳方,全部有必要确保同步接纳,不能有tAC之类的误差。这样在写入时,DRAM芯片不再自己生成DQS,而以发送方传来的DQS为基准,并相应拖延必定的时刻,在DQS的中部为数据周期的选取切割点(在读取时切割点便是上下沿),从这儿分离隔两个传输周期。这样做的长处是,因为各数据信号都会有一个逻辑电平坚持周期,即便发送时不同步,在DQS上下沿时都处于坚持周期中,此刻数据接纳触发的准确性无疑是最高的,如下图二所示。

图二 数据时序

数据掩码技能(DQM)

不是DDR所特有的,但关于DDR来说也是比较重要的技能,所以一起介绍下。

为了屏蔽不需求的数据,人们选用了数据掩码(Data I/O Mask,简称DQM)技能。经过DQM,内存能够操控I/O端口撤销哪些输出或输入的数据。这儿需求着重的是,在读取时,被屏蔽的数据仍然会从存储体传出,只是在“掩码逻辑单元”处被屏蔽。

DQM由主控芯片操控,为了准确屏蔽一个P-Bank位宽中的每个字节,每个64bit位宽的数据中有8个DQM信号线,每个信号针对一个字节。这样,关于4bit位宽芯片,两个芯片共用一个DQM 信号线,关于8bit位宽芯片,一个芯片占用一个DQM信号,而关于16bit位宽芯片,则需求两个DQM引脚。SDRAM 官方规则,在读取时DQM宣布两个时钟周期后收效,而在写入时,DQM与写入指令相同是当即收效,如下图三和四别离显现读取和写入时突发周期的第二笔数据被撤销。

图三 读取时数据掩码操作

图四 写入时数据掩码操作

所以DQM信号的效果便是关于突发写入,假如其间有不想存入的数据,就能够运用DQM信号进行屏蔽。DQM信号和数据信号一起宣布,接纳方在DQS的上升与下降沿来判别DQM的状况,假如DQM为高电平,那么之前从DQS中部选取的数据就被屏蔽了。

有人或许会觉得,DQM是输入信号,意味着DRAM芯片不能宣布DQM信号给主控芯片作为屏蔽读取数据的参阅。其实,该读哪个数据也是由主控芯片决议的,所以DRAM芯片也无需参加主控芯片的作业,哪个数据是有用的就留给主控芯片自己去挑选。

好了,前面介绍了DQS的功用,那么咱们在测验时依据DQS和DQ的波形是怎么差异数据的读写操作的?

在DDRx里边常常会被一些缩写误扰,如OCD、OCT和ODT,我想有相同困扰的大有人在,现在笔者来介绍一下咱们的这些困扰吧。

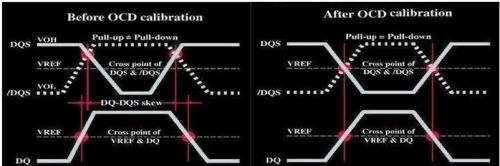

片外驱动调校OCD(Off-Chip Driver)

OCD是在DDR-II开端参加的新功用,并且这个功用是可选的,有的材料上面又名离线驱动调整。OCD的首要效果在于调整I/O接口端的电压,来补偿上拉与下拉电阻值,然后调整DQS与DQ之间的同步确保信号的完好与可靠性。调校期间,别离测验DQS高电平和DQ高电平,以及DQS低电平和DQ高电平的同步状况。假如不满意要求,则经过设定突发长度的地址线来传送上拉/下拉电阻等级(加一档或减一档),直到测验合格才退出OCD操作,经过OCD操作来削减DQ、DQS的歪斜然后进步信号的完好性及操控电压来进步信号质量。详细调校如下图五所示。

图五 OCD

不过,因为在一般状况下对运用环境安稳程度要求并不太高,只需存在差分DQS时就根本能够确保同步的准确性,并且OCD 的调整对其他操作也有必定影响,因而OCD功用在一般台式机上并没有什么效果,其长处首要表现在对数据完好性十分灵敏的服务器等高端产品范畴。

ODT(On-Die Termination,片内完结)

ODT也是DDR2相关于DDR1的要害技能打破,所谓的完结(端接),便是让信号被电路的终端吸收掉,而不会在电路上构成反射,构成对后边信号的影响。望文生义,ODT便是将端接电阻移植到了芯片内部,主板上不再有端接电路。在进入DDR年代,DDR内存对作业环境提出更高的要求,假如从前宣布的信号不能被电路终端彻底吸收掉而在电路上构成反射现象,就会对后边信号的影响构成运算犯错。因而现在支撑DDR主板都是经过选用完结电阻来处理这个问题。因为每根数据线至少需求一个完结电阻,这意味着每块DDR主板需求很多的完结电阻,这也无形中增加了主板的生产本钱,并且因为不同的内存模组对完结电阻的要求不或许彻底相同,也构成了所谓的“内存兼容性问题”。 而在DDR-II中参加了ODT功用,当在DRAM模组作业时把完结电阻器关掉,而关于不作业的DRAM模组则进行完结操作,起到削减信号反射的效果,如下图六所示。

图六 ODT端接暗示图

ODT的功用与制止由主控芯片操控,在开机进行EMRS时进行设置,ODT所完结的信号包含DQS、DQS#、DQ、DM等。这样能够发生更洁净的信号质量,然后发生更高的内存时钟频率速度。而将完结电阻规划在内存芯片之上还能够简化主板的规划,降低了主板的本钱,并且完结电阻器能够和内存颗粒的“特性”相符,然后削减内存与主板的兼容问题的呈现。

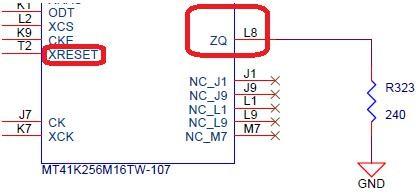

重置(Reset)

重置是DDR3新增的一项重要功用,并为此专门预备了一个引脚。这一引脚将使DDR3的初始化处理变得简略。当Reset指令有用时,DDR3 内存将中止一切的操作,并切换至最少数活动的状况,以节约电力。在Reset期间,DDR3内存将封闭内涵的大部分功用,一切数据接纳与发送器都将封闭,且一切内部的程序设备将复位,DLL(推迟锁相环路)与时钟电路将中止作业,甚至不答理数据总线上的任何动态。这样一来,该功用将使DDR3到达最节约电力的意图,新增的引脚如下图七所示。

图七 Reset及ZQ引脚

ZQ校准

如上图七所示,ZQ也是一个新增的引脚,在这个引脚上接有一个240欧姆的低公役参阅电阻。这个引脚经过一个指令集,经过片上校准引擎(ODCE,On-Die Calibration Engine)来主动校验数据输出驱动器导通电阻与ODT的完结电阻值。当体系宣布这一指令之后,将用相应的时钟周期(在加电与初始化之后用512个时钟周期,在退出自改写操作后用256时钟周期、在其他状况下用64个时钟周期)对导通电阻和ODT电阻进行从头校准。

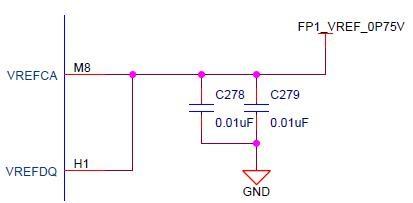

VREFCA VREFDQ

关于内存体系作业十分重要的参阅电压信号VREF,在DDR3体系中将VREF分为两个信号。一个是为指令与地址信号服务的VREFCA,另一个是为数据总线服务的VREFDQ,它将有用的进步体系数据总线的信噪等级,如下图八所示。

图八 VREFCA VREFDQ

现在来说说DDR3和DDR4最要害的一些技能,write leveling以及DBI功用。

Write leveling功用与Fly_by拓扑

Write leveling功用和Fly_by拓扑密不可分。Fly_by拓扑首要运用于时钟、地址、指令和操控信号,该拓扑能够有用的削减stub的数量和他们的长度,可是却会导致时钟和Strobe信号在每个芯片上的飞翔时刻偏移,这使得操控器(FPGA或许CPU)很难坚持tDQSS、tDSS 和tDSH这些参数满意时序标准。因而write leveling应运而生,这也是为什么在DDR3里边运用fly_by结构后数据组能够不必和时钟信号去绕等长的原因,数据信号组与组之间也不必去绕等长,而在DDR2里边数据组仍是需求和时钟有较宽松的等长要求的。DDR3操控器调用Write leveling功用时,需求DDR3 SDRAM颗粒的反应来调整DQS与CK之间的相位联系,详细方法如下图九所示。

图九 Write leveling

Write leveling 是一个彻底主动的进程。操控器(CPU或FPGA)不断的发送不一起延的DQS 信号,DDR3 SDRAM 颗粒在DQS-DQS#的上升沿采样CK 的状况,并经过DQ 线反应给DDR3 操控器。操控器端重复的调整DQS-DQS#的延时,直到操控器端检测到DQ 线上0 到1 的跳变(阐明tDQSS参数得到了满意),操控器就锁住此刻的延时值,此刻便完成了一个Write leveling进程;一起在Leveling 进程中,DQS-DQS#从操控器端输出,所以在DDR3 SDRAM 侧有必要进行端接;同理,DQ 线由DDR3 SDRAM颗粒侧输出,在操控器端有必要进行端接;

需求留意的是,并不是一切的DDR3操控器都支撑write leveling功用,所以也意味着不能运用Fly_by拓扑结构,一般这样的主控芯片会有相似以下的描绘:

DBI功用与POD电平

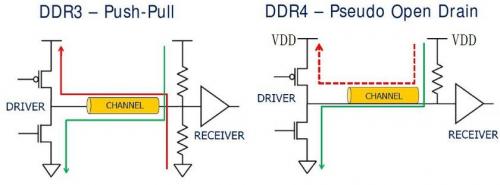

DBI的全称是Data Bus Inversion数据总线回转/倒置,它与POD电平密不可分,它们也是DDR4差异于DDR3的首要技能打破。

POD电平的全称是Pseudo Open-Drain 伪漏极开路,其与DDR3比照简略的示例电路如下图十所示。

图十 POD暗示电路

从中能够看到,当驱动端的上拉电路导通,电路处于高电平时(也即传输的是“1”),此刻两头电势差平等,相当于回路上没有电流流过,但数据“1”仍是照样被传输,这样的规划削减了功率耗费。

正是因为POD电平的这一特性,DDR4规划了DBI功用。当一个字节里的“0”比特位多于“1”时,能够使能DBI,将整个字节的“0”和“1”回转,这样“1”比“0”多,比较原(回转前)传输信号更省功耗,如下表一所示。

表一 DBI示例

以上便是DDRx的一些首要的要害技能介绍,能够用如下表二所示来总结下DDRx的特性比照。

表二 DDRx SDRAM特性比照

更多有关DDR技能文章,欢迎拜访与非网DDR专区