前语

跟着智能体系的前进和“ 物联网”的开展,以及人与物之间互联互通的增强,大多数新产品现在均选用了根据SoC 的开发渠道。此类渠道便于企业以更快的速度将产品推向商场,进步体系级功率,并且最重要的是便于完结继续的创新和产品差异化。

为完结出资报答最大化,规划团队有必要精心挑选完结产品差异化的办法,一同还有必要满意日益增长的商场需求和苛刻的本钱方针要求。真实的渠道差异化依赖于新的软件特性与新的硬件特性的组合。鉴于加速产品上市这一要求实践上在各层面均存在差异化,因而需求东西和环境可以在不影响架构和功用的条件下,用传统ASSP 编程环境所具有的完好性和易用性完结软硬件的差异化。

就当时的硬件差异化而言,许多渠道开发人员运用FPGA 完结恣意(Any-to-Any)互连。其间的可编程逻辑用于将渠道的处理器衔接到PCIe® 和以太网等规范接口上。此外,许多体系也将FPGA 作为用于完结要害功用和算法加速的协处理器。与在规范处理器上运转比较,可编程逻辑的并行架构可供给高达100 倍以上的功用优势。

2011 年推出的Zynq®-7000 全可编程SoC 和现在新推出的Zynq UltraScale+™MPSoC,别离选用先进的28nm 工艺节点和16nm 工艺节点,将强壮的ARM® 处理体系和可编程逻辑完美结合在了一同。跟着这两款产品的面世,赛灵思现可供给彻底代替传统处理器和特定范畴专用SoC 的业经验证的代替产品。Zynq SoC和MPSoC 可以在下降资料清单本钱的一同进步体系功用并下降体系功耗。

赛灵思SDSoC 开发环境介绍

Zynq SoC 和MPSoC 与软件工程师和FPGA 硬件工程师一起组成的规划团队可谓天合之作。但其关于硬件资源有限或短缺的团队来说,运用起来很有难度,由于需求具有RTL(VHDL或Verilog)开发专业知识才干充分发挥该器材的优势。为处理这一难题,让更多的规划团队可以运用Zynq 器材的优势,赛灵思推出了一种全新的C/C++ 开发环境SDSoC™。SDSoC开发环境是赛灵思SDxTM 系列开发环境的第三大成员,可以让更广泛的嵌入式软件开发人员发挥软硬件“ 全可编程”器材的威力。

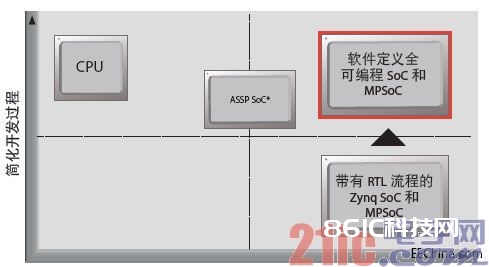

SDSoC 带来的软件界说机会

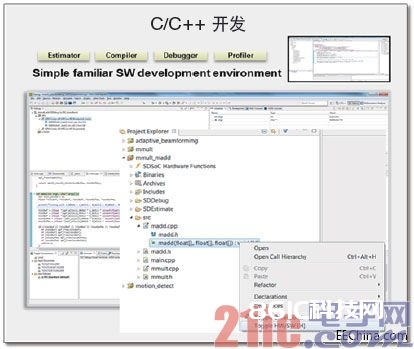

C/C++ 环境供给相似ASSP 的编程体会

功用功耗比和恣意互连

* 要点范畴(例如图画/ 视频、SDR 等)

注:软件可编程器材往往与FPGA 结合运用,以完结衔接和协处理功用

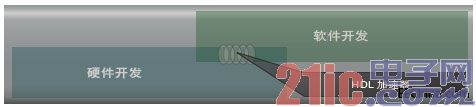

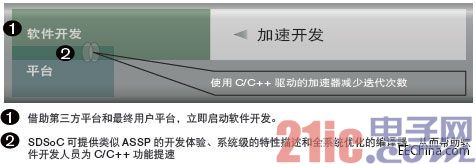

SDSoC 开发环境可经过两种方法加速Zynq SoC 和MPSoC 开发进程。第一种是,软件开发人员凭借赛灵思渠道、第三方渠道

或最终用户渠道,可以比运用传统硬件/ 传统软件开发流程更快地发动开发。第二种是,SDSoC 可以消除在将可编程逻辑用作

软件加速器时软件团队和硬件团队之间常发生的重复改变,真实加速全体体系开发进程。

传统开发进度

软件界说开发进程

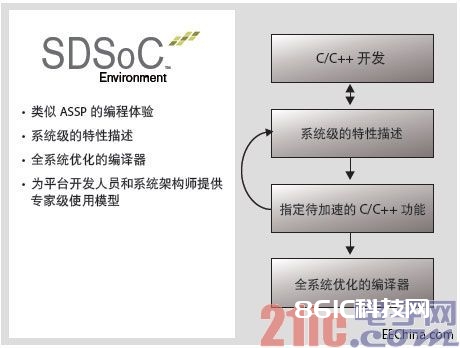

SDSoC 开发环境可供给高度简化、相似ASSP C/C++ 的编程体会,包括简洁易用的Eclipse 集成规划环境(IDE)和用于异构Zynq 渠道布置的归纳开发渠道。SDSoC 配有业界首款C/C++ 全体系优化的编译器,可供给体系级的特性描绘、可编程逻辑内主动软件加速、主动体系衔接生成,以及用于加速编程速度的各种库。此外,SDSoC 还可为客户和第三方渠道开发人员供给专门的流程,以便在SDSoC 开发环境中运用这些渠道。

SDSoC 开发环境

相似ASSP 的编程体会

SDSoC 可供体系和嵌入式软件开发人员运用,其供给的Eclipse IDE 可用于开发运转于裸机或Linux 和FreeRTOS 等操作体系上的C/C++ 运用。SDSoC 可用于开发各种完好的异构多处理体系,包括运转在ARM/NEON 处理器上的软件和可编程逻辑中的软件加速器,还能将现有的HDL IP 模块重复用作C 言语可调用的库。与传统的独自以硬件为中心的流程和以软件为中心的流程不同,这两种流程可能会导致开发推迟、体系架构与功用的不确认性,而SDSoC 在开发人员了解的嵌入式结构中完结快速体系特性描绘和可编程逻辑软件加速。

这款简洁易用的IDE 可供给项目创立导游,供用户挑选方针渠道和操作体系,并运用模板创立功用完全的SDSoC 项目,作为构建自己运用的起点。

此外,SDSoC 还可为软件团队供给简略的GUI 选项,用于挑选在可编程逻辑中加速的功用。SDSoC 编译器将生成预备在方针渠道板上运转的一切必备硬件和软件。

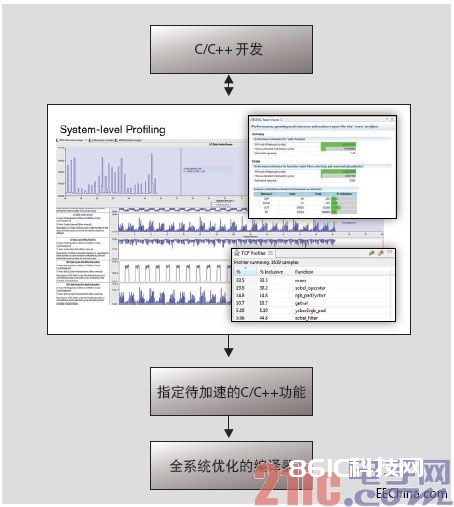

体系级的特性描绘

以赛灵思软件开发套件(SDK)现在供给的高档软件特性描绘为根底,SDSoC 增添了体系级特性描绘,用于快速体系(软/ 硬件)功用预算。此外,还能快速生成并探究体系级架构,以完结最佳整体体系功用与功耗。

SDSoC 选用根据PC 采样的非侵入式编译器和规范的GPROF 编译器,能协助用户装备其本身软件运用,以辨认占用时刻最多且适用于硬件加速的功用。

此外,SDSoC 还增添了快速体系(软/ 硬件)功用和器材运用率预算功用,可以敏捷完结体系级架构探究,以完结最佳功用、资源运用率和功耗。用户可在可编程逻辑中设定待加速的功用,并且SDSoC 还能调用C/C++ 代码来陈述软件周期、硬件周期、数据传输预算、整体运用加速以及硬件资源运用率等状况。

充分运用根据渠道的功用预算流程,软件开发人员可以在数分钟内敏捷预算出将一项或多项软件功用转移到硬件中用于加速所发生的功用影响,而实践的硬件生成则需求一小时乃至更长时刻。

在方针渠道上,SDSoC 运用由ARM CPU 供给的功用计数器,一同主动刺进AXI 功用监控器(APM)到可编程逻辑中以收集硬件功用数据,可为缓存、存储器、软件加速器和总线运用率供给主动功用丈量。运转在渠道上的软件可收集功用数据,SDSoC 就运用该数据协助辨认体系中的功用瓶颈。这种快速的功用反应能完结最佳代码分区,以满意体系级功用和功耗需求,一同将开发流程缩短数周时刻。

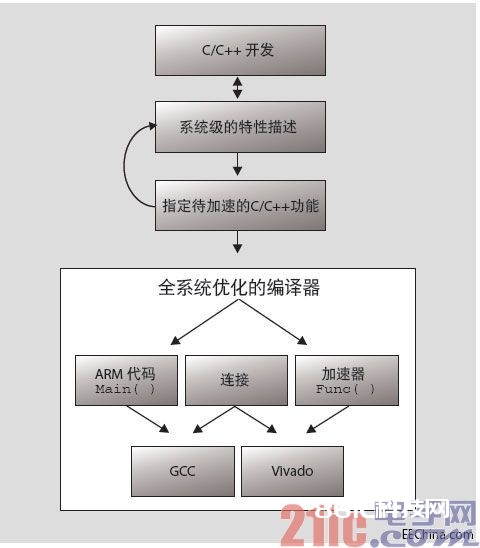

全体系优化的编译器

SDSoC 还具有针对ARM 处理体系和可编程逻辑的全体系优化的编译器。SDSoC 旨在协助体系架构师和软件团队运用“golden

C/C++ source”,经过生成最佳体系衔接,快速完结宏架构和微架构的装备。这样既能得到最佳体系衔接和存储器接口,还能快速完结规划空间探究,便于开发人员归纳权衡功用、吞吐量、时延,一同坚持较短的规划迭代时刻。

该编译器充分运用根底的高层次归纳编译器技能,已有逾千名编程人员运用该技能生成了根据C/C++ 的高功用IP。将该编译器与链接器结合运用,并根据方针渠道以及在可编程逻辑中生成的用户指定的主动软件加速功用,将程序转换到完好的软硬件体系中。

根据程序语法、程序剖析、调度组织、体系衔接的特性化硬件建模,SDSoC 能在可编程逻辑中生成用于软件的加速器。SDSoC 充分运用渠道的板支撑包(BSP)、方针软件加速功用、IP 和优化库及体系衔接生成功用,构建规划的可编程逻辑部分。该编译器可主动把体系编译为完好的软硬件体系,包括用于可编程逻辑的比特流和用于装备方针渠道的ARM 处理体系ELF 文件。

可编程逻辑中每个加速功用都可以作为独立的线程运转。SDSoC 可生成与之同步和保存原始程序语义所需的软硬件组件,一同可完结使命级的并行和用流水线完结的通讯和核算,以获取高功用。

C/C++ 运用源码可包括多个加速功用,特定功用的多个实例以及对主程序各不同部分中的加速器功用的调用。为取得最佳功用,SDSoC 还供给赛灵思优化库和赛灵思联盟成员供给的备选库。

经过从“single golden source”生成完好的嵌入式运用,SDSoC 可在运用层重构C/C++ 代码,便于软件开发人员迭代规划和架构改变,然后明显缩短在渠道上运转作业程序所需的时刻。

面向渠道开发人员的专家级运用模型

SDSoC可为体系架构师和渠道开发人员供给专家级的运用模型。经过将体系级的特性描绘和功用剖析功用与主动体系衔接生成功用完美结合,该东西可协助架构师界说、探究并生成各种架构,为自己的运用渠道找到最为抱负的规划完结计划,并传递给嵌入式软件开发人员,用于在运用渠道顶层构建完好的运用。

凭借主动体系衔接生成功用,架构师可以快速界说、探究并生成宏体系架构和微体系架构,用以确认Zynq处理体系、存储器和根据可编程逻辑的加速器之间的最佳互联架构。

将赛灵思Vivado® 规划套件与SDSoC 结合运用,可用于创立特定运用渠道。该渠道创立功用还可以将现有的RTL 和IP 装备用作C 言语可调用的库。这对需求凭借规划重用来加速渠道开发的团队大有裨益。

SDSoC 可为根据Zynq 全可编程 SoC 的开发板(比如ZC702、ZC706 等)、第三方和特定商场渠道(BSP)(如Zedboard、MicroZed 和ZYBO),以及视频成像开发套件等供给板支撑包(BSP)。这些BSP 中包括的元数据可让SDSoC 进行渠道笼统,以便嵌入式软件开发人员和体系架构师进步出产力,并加速产品开发进程。

SDSoC 开发环境可供给相似ASSP 的C/C++ 编程体会,以进步运用开发、体系架构界说和渠道创立的出产功率。 SDSoC 结合Zynq 全可编程SoC 和MPSoC,使嵌入式软件开发人员可以加速智能体系开发进程。

定论

SDSoC 开发环境可供给相似ASSP 的C/C++ 编程体会,以进步运用开发、体系架构界说和渠道创立的出产功率。 SDSoC 结合Zynq 全可编程SoC 和MPSoC,使嵌入式软件开发人员可以加速智能体系开发进程。