跟着我国航空航天技术的迅速发展,对地上遥控遥测接纳机的实时性和高速数据传输功用的要求越来越高。越来越多的遥测遥控地上信道处理器都选用了实时才干更强的高速DSP/FPGA架构规划方案。依据DSP/FPGA架构的规划方案表现出强壮的处理才干和高度的灵敏性。可是,在研制中发现对FPGA以及DSP/FPGA之间的接口调试很费时间和精力。究其原因是FPGA在线调试功用的支撑很限制,所以本文规划一种通用的适于DSP/FPGA架构的遥测接纳机的调试和测控通讯接口,然后方便在研制中进行调试和牢靠的传输测控中所需的实时参数。现有文献的一般做法是运用网络接口来完结数据和操控指令的传输,可是在树立衔接之后,数据传输中,一旦呈现掉电或重启就会丢掉数据,甚至会呈现程序跑飞现象。通用串行总线(USB)因具有传输速度快、支撑热插拔、易于扩展以及即插即用等长处,现已成为计算机与外部设备进行数据交换的常用接口。USB操控器是一种集成了USB总线协议的微操控器,使用USB操控器,用户能够在不深入了解USB协议的状况下规划完好的USB接口,这也促进了USB接口的广泛使用。

为了满意更高的测控及数据传输速率的要求,提出并规划一种依据CY7C68013A的通用测控通讯接口。该体系安稳牢靠、普适性好,而且可传输高质量的图画数据,具有很好的使用远景。

1 体系整体规划

该体系整体结构图如图1所示,体系大致可分为3个部分。其间FPGA首要完结通讯接纳机的信号捕获盯梢、载波康复、守时同步、图画数据下传、测控指令上传以及USB芯片端点FIFO的读写操控。PC端的操控终端首要完结图画数据的接纳和处理、测控指令的生成、GUI交互界面的更新、重要参数的记载和备份。Cypress FX2LP芯片首要完结数据的双向传递以及与PC间的“问答”逻辑的完结。Cypress FX2LP芯片一方面要装备端点相关寄存器和读写缓存中的数据,另一方面经过端点0“答复”PC终端程序关于内部缓存中数据状况状况的查询,而且在数据不满意传输指定格局的时分,还要将数据包修正成契合传输设定的格局的数据包。

FPGA选用Xilinx公司的Spartan-6系列芯片,考虑到遥测指令和图画数据的优先等级,选用中止形式操控器对USB的端点FIFO进行读写操控。当没有遥测指令需求上传的时分,FPGA中的FIFO读写操控器不断的将图画数据写入到USB的端点FIFO中;当FIFO读写操控器检测到USB端有遥测指令需求上传的时分,即暂缓图画数据的写入,将图画数据缓存在内部RAM中,开释读写总线,然后敞开读取FIFO的操控进程将遥测指令读入到FPGA的暂存FIFO中。

2 体系硬件规划

2.1 CY7C68013A芯片简介

CY7C68013A为Cypress公司的一款高功用的USB2.0微操控器,其内部集成了USB2.0收发器、增强型的8051核、智能串行接口引擎(SIE)、4个片上FIFO和16KBRAM、通用可编程接口(GPIF)。该芯片支撑全速(12 Mbps)和高速(480Mbps)两种速率的数据传输。其内嵌的增强的8051处理器支撑两个USART、3个守时器/计数器、扩展的中止体系以及I2C协议总线外设。CY7C68013A支撑3种接口形式和外部器材进行通讯,别离是:Ports形式,GPIF Master形式和Slave FIFO形式。

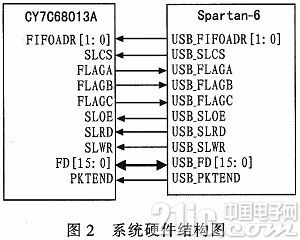

2.2 FPGA接口模块规划

在本体系中的CY7C68013A选用异步SlaveFIFO的作业形式。图2给出了CY7C68013A和Spartan-6的硬件衔接图。其间,USB_FLAGA(B/C)为CY7C68013A输出的状况标志信号,在USB固件中能够灵敏的将它们装备为端点FIFO的状况满、空或许恣意可编程的标志位;USB_SLOE、USB_ SLRD、USB_WR组合完结对CY7C68013A端点FIFO的读写时序操控;USB_FD为双向的数据总线;USB_PKEND为数据打包操控信号。

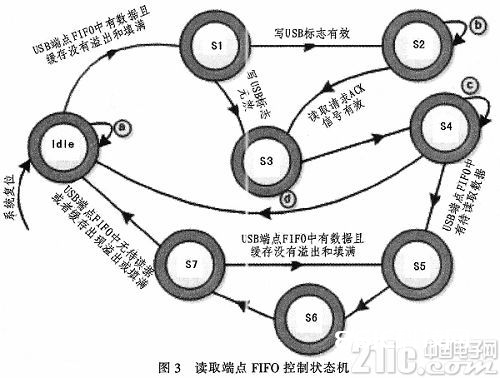

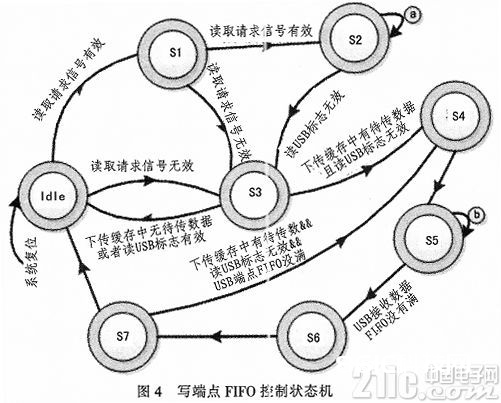

FPGA接口模块规划首要包含上行缓存、下传缓存、双向FIFO逻辑操控逻辑规划。其间双向的FIFO逻辑操控完结对CY7C68013A的端点FIFO进行数据的读写操作,而且完结从下传缓存中读取数据以及把上传的数据写入到上传缓存的时序操控。本规划中选用两个并行的状况机来操控,两个状况机别离完结从USB端点FIFO读取数据并写入到上行缓存,从下行缓存中读取数据并将数据写入到相应的端点FIFO中。考虑到下行图画数据和上行遥测操控指令的优先级,将两个状况机之间的信息交互规划成在中止形式下运转,以此来处理对数据总线的同享问题。

读取USB端点FIFO操控状况机如图3所示。图中小圆圈标示的状况转化条件的含义为:a标明USB端点FIFO中没有需求读取的数据或许上行缓存堵塞;b标明没有检测到读取恳求ACK的有用信号;c标明检测到USB端点FIFO中无待读取数据;d标明在状况S4的状况下,检测到USB端点FIFO中无待读数据的次数超越预先设定的阈值VT。该操控状况机共包含了8个状况。其间,Idle为初始状况;S2状况完结是否接纳到读取恳求ACK信号,假如收到则转入S3进入读取数据的流程,反之,则停留在该状况等候回应;S3状况为读取数据预备地址信号,并输出地址信号;S4状况再次承认是否有数据需求读取;S5完结从USB端点FIFO中读取数据到内部寄存器中;S6完结将内部寄存器的数据写入到上行缓存中;S7完结判别是否需求(能)持续读取数据,若需求(能)持续读取,转入状况S5,反之,回到Idie状况等候下次读取的发动。

写端点FIFO操控状况机如图4所示。图中小圆圈标示的状况转化条件的含义为:a标明读取USB端点FIFO的标志有用,阐明数据总线被占用;b标明检测到USB端点接纳数据FIFO中的数据已填满。该状况机中共包含了8个状况,其间Idle为初始状况,判别是否有读取数据恳求信号,若有转入对读取恳求中止处理状况S1,反之,转入状况S3开端数据的写入进程;S2状况等候读取数据完毕,开释数据总线,转入状况S3;S4从下行缓存中读取数据,存入到内部寄存器中;S6将内部寄存器中的数据写入到USB端点FIFO中;S7判别是否需求(而且数据总线闲暇、端点FIFO中未满)持续读取数据,若需求(能)持续读取,转入状况S4,反之,将打包信号USB_PKTEND置为有用而且回到Idle状况发动下一次写状况机的运转。

航空航天测控设备由于其特其他使用环境,常常遭受强磁场、空间强粒子流或许单粒子翻转效应等特别搅扰的影响。所以在上面的状况机的规划中,对重要的触发信号和标志位信号进行了屡次间隔性冗余维护承认。如在读取操控状况机中,在S4状况下再次对USB端点FIFO中是否有需求读取的数据进行判别,是为了避免由于PCB电气特性不安稳或许偶尔的空间电磁搅扰导致之前发动读取数据的进程为误判,而在此再次承认该信号的有用性,这样规划增强了体系的容错性和抗搅扰才干。相似的容错思维在写端点FIFO操控状况机的S1状况也能够表现出来。

2.3 USB驱动程序

Cypress FX2开发包中供给了通用的驱动程序,通用驱动程序完结与外设和用户使用程序的通讯和操控,微处理器依据新的设置装置通用驱动程序,从头枚举外设为一个新的USB设备。

3 体系软件规划

3.1 固件程序规划

CY7C68013A芯片的固件程序运转在芯片内部,首要完结对芯片作业形式的装备以及处理主机的USB设备恳求。Cypress供给了固件程序的开发结构,开发人员只需求按使用布景和需求对所给结构内的程序做细化和修正即可。USB传输可分成数据传输和操控传输,其间数据传输由大端点(EP2/4/6/8)完结,操控传输由小端点(EPO)完结。在固件程序中,TD_Poll()为数据处理程序,处在主函数的While()循环中。该函数包含完结特别任务的代码,设备运转时将被重复调用。

在本体系中,咱们将EP2装备为Bulk传输形式的OUT端点,其端点缓存为512Byte,两级缓存;EP6装备为Bulk传输形式的IN端点,其端点缓存为512Byte,四级缓存。而且把EP6FIFO装备为AUTIN形式,其AUTOINLEN装备为512Byte。固件程序还必须完结对PC操控终端发送来的USB操控传输恳求的呼应。端点0是CY7C68013A中仅有的操控端点,它是一个可完结双向操控传输的端点,只要它才干处理SETUP指令。完结主机USB操控传输恳求的固件程序段,只需求在所给固件结构下的函数DR_VendorCmnd()中回来EP2468STAT寄存器的值即可完结。

3.2 操控上位机规划

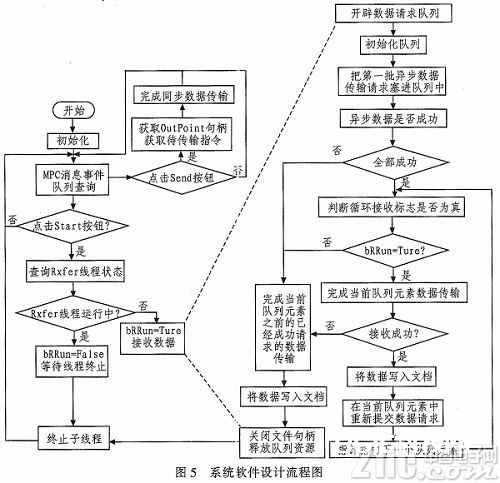

该测控接口的上位机软件规划选用MFC编程,MFC封装了大部分的windows API函数,选用音讯循环机制处理事情。在MFC结构生成的工程中,添加上Cypress供给的CyAPI库文件,即可在工程中调用库中现已封装好的类的成员变量以及成员函数。在上位机的规划中选用了多线程编程,体系软件规划的流程图如图5所示。

在上位机软件规划中,主线程首要完结在音讯循环机制下检测面板上的点击事情,以及对子线程做出的相应的操控。在主线程的初始化中,首要生成CCyUSBDevice目标,然后读取硬件装备信息以及设备的必要辨认信息并显现在前操作面板上,最终树立RXfer子线程。在主线程中,当检测到Send按钮被点击时。即开端发送上行指令。此处选用同步数据传输,确保了数据传输的准确性。当主线程中检测到Start按钮被点击时,依据RXfer线程的不同状况,履行相应的操作。在RXfer子线程中,首要完结下行数据的接纳、下行数据写入数据文档以及办理行列中的恳求等作业。鄙人行数据接纳线程中,咱们选用了异步数据传输方法。在异步传输方法下,上位机软件宣布数据恳求之后,不需求等候回应,即可当即宣布下一次的数据恳求,这样可极大的进步上位机软件的数据吞吐速率,确保数据传输的高效率。屡次的异步数据恳求是使用数据恳求行列来完结的,在线程函数的开端,拓荒恰当长度的数据恳求行列,而且给他们分配相应的内存空间,然后进入到线程的循环体中。在循环体中,完结当时的行列元素中的恳求数据传输并把相应数据写入数据文档之后,当行将新的数据恳求塞入到该行列元素中,而且把指针更新到下一个行列元素。当数据恳求失利、承受数据不成功或许循环接纳数据标志位False时,首要完结行列中其他现已成功恳求数据传输的数据,然后封闭文件句柄,开释相应的资源,最终停止线程。

4 体系测验成果

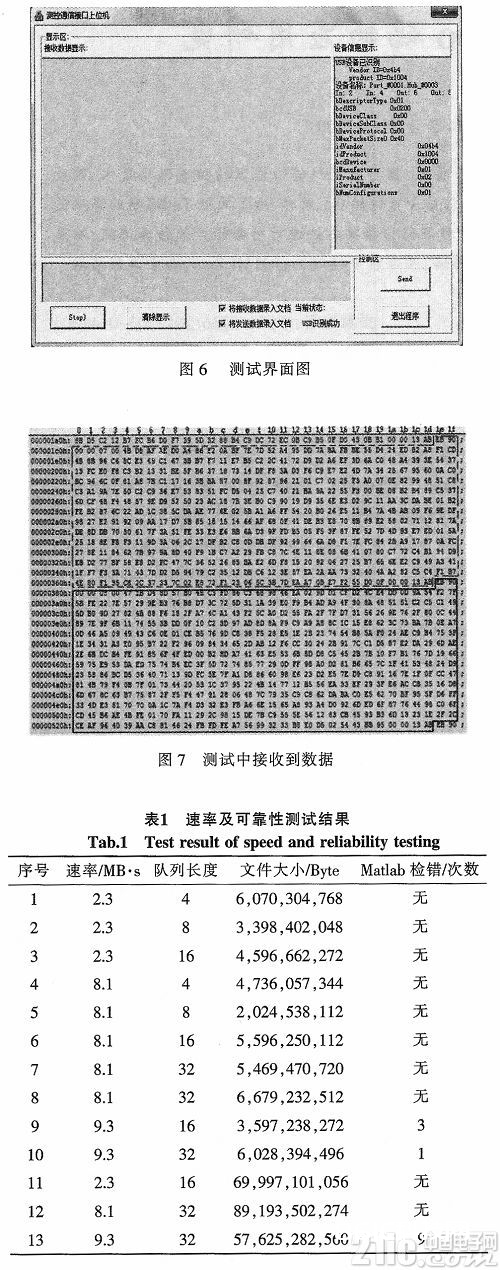

该通用测控通讯接口用于实践测控数据的下传,实践测验面板如图6所示。在进行测验时,首要运转该测验使用软件,完结初始化之后,在设备信息显现框中显现USB设备信息,其间包含设其他PID和VID、EndPoint装备状况、设备描述信息等信息。然后经过点击“start”按钮,树立起RXfer线程,开端接纳下行传输数据。若需发送指令,在Send按钮左面的输入框中输入恰当的遥测遥控指令,然后点击Send即可发送。测验体系中所接纳到的数据如图7所示。在此数据中选用了契合CCSDS航天测控规范数据格局,帧头为EB90,接下来的三个Byte为帧计数(图中显现的是000007),帧结束标志位13AB,帧结束标志的前两个Byte为RS译码陈述输出(译码前数据是否犯错,过错是否可纠)。

对该通用测控通讯接口的速率和牢靠性进行了测验,测验成果如表1所示。比照表中数据看出,该接口的最高的牢靠的传输速率可达为8.1MB/s,对2.3MB/s和8.1MB/s的速率进行了牢靠性测验,测验的成果都显现,在该速率下所规划的测控通讯接口能够完结数据的牢靠传输。

5 定论

该测控通讯接口体系选用USB2.0协议芯片CY7C68013A和FPGA搭建了硬件渠道,在FPGA状况机规划中选用中止形式的双状况机和要害标志冗余规划的思维,软件规划选用多线程的规划思维,进步了通讯接口的牢靠性和传输速率。该测控通讯接口已用于实践测控通讯体系中,实践使用标明该测控通讯接口具有速率高、安稳牢靠、人机界面友爱等特色,到达体系规划要求,具有推广使用的价值。