PC机发送字符给单片机操控发光管亮,一同将其传回PC机,其间单片机的发送和接纳都选用查询方法

1、USART的首要特点

通用同步和异步串行接纳器和转发器(USART) 是一个高度灵敏的串行通讯设备。首要特点为:

全双工操作( 独立的串行接纳和发送存放器)

异步或同步操作

主机或从机供给时钟的同步操作

高精度的波特率发生器

支撑5, 6, 7, 8, 或9 个数据位和1 个或2 个中止位

支撑的奇偶校验操作

数据过速检测? 帧过错检测

噪声滤波,包括过错的开端位检测,以及数字低通滤波器 三个独立的中止:发送完毕中止, 发送数据存放器空中止,以及接纳完毕中止

多处理器通讯形式

倍速异步通讯形式

2、异步串行收发器

USART 分为了三个首要部分: 时钟发生器,发送器和接纳器。操控存放器由三个单元同享。时钟发生器包括同步逻辑,经过它将波特率发生器及为从机同步操作所运用的外部输入时钟同步起来。XCK ( 发送器时钟) 引脚只用于同步传输形式。发送器包括一个写缓冲器,串行移位存放器,奇偶发生器以及处理不同的帧格局所需的操控逻辑。写缓冲器能够坚持接连发送数据而不会在数据帧之间引进推迟。由于接纳器具有时钟和数据康复单元,它是USART 模块中最杂乱的。康复单元用于异步数据的接纳。除了康复单元,接纳器还包括奇偶校验,操控逻辑,移位存放器和一个两级接纳缓冲器UDR。接纳器支撑与发送器相同的帧格局,并且能够检测帧过错,数据过速和奇偶校验过错。

3、时钟发生

1)USART支撑4种形式的时钟

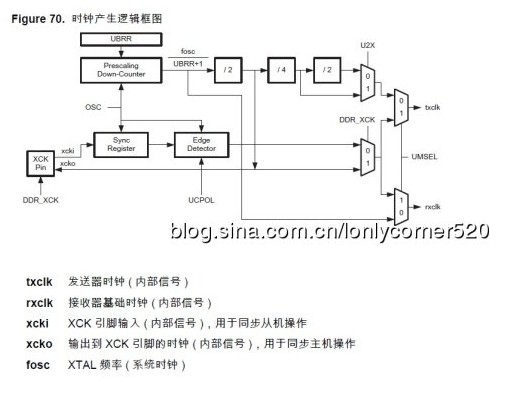

时钟发生逻辑为发送器和接纳器发生根底时钟。USART 支撑4 种形式的时钟:正常的异步形式,倍速的异步形式,主机同步形式,以及从机同步形式。USART 操控位UMSEL和状况存放器C (UCSRC) 用于挑选异步形式和同步形式。倍速形式( 只适用于异步形式) 受控于UCSRA 存放器的U2X。运用同步形式 (UMSEL = 1) 时,XCK 的数据方向存放器(DDR_XCK)决议时钟源是由内部发生(主机形式)仍是由外部出产(从机形式)。仅在同步模式下XCK 有用。

2)内部时钟用于异步形式和同步主机形式

USART 的波特率存放器UBRR 和降序计数器相连接,一同构成可编程的预分频器或波特率发生器。降序计数器对体系时钟计数,当其计数到零或UBRRL 存放器被写时,会主动装入UBRR 存放器的值。当计数到零时发生一个时钟,该时钟作为波特率发生器的输出时钟,输出时钟的频率为fosc/(UBRR+1)。发生器对波特率发生器的输出时钟进行2、8或16 的分频,详细情况取决于作业形式。波特率发生器的输出被直接用于接纳器与数据康复单元。数据康复单元运用了一个有2、8或16个状况的状况机,详细状况数由UMSEL、U2X 与 DDR_XCK 位设定的作业形式决议。Table 60 给出了核算波特率(位/秒)以及核算每一种运用内部时钟源作业形式的UBRR值的公式。

3)倍速作业形式

经过设定UCSRA 存放器的U2X 能够使传输速率加倍。该位只对异步作业形式有用。当作业在同步形式时,设置该位为“0”。设置该位把波特率分频器的分频值从16 降到8,使异步通讯的传输速率加倍。此刻接纳器只运用一半的采样数对数据进行采样及时钟康复,因而在该形式下需求更准确的体系时钟与更准确的波特率设置。发送器则没有这个要求。

4)外部时钟(这些东西感觉都是扯淡的~~呵呵)

同步从机操作形式由外部时钟驱动,如Figure 70 所示。

输入到XCK 引脚的外部时钟由同步存放器进行采样,用以进步稳定性。同步存放器的输出经过一个边缘检测器,然后应用于发送器与接纳器。这一进程引进了两个CPU 时钟周期的延时,因而外部XCK 的最大时钟频率由以下公式约束:fsck要留意fosc 由体系时钟的稳定性决议,为了避免因频率漂移而丢掉数据,主张保存满足的裕量。

5)同步时钟操作

运用同步形式时(UMSEL = 1)XCK 引脚被用于时钟输入( 从机形式) 或时钟输出( 主机模式)。时钟的边缘、数据的采样与数据的改动之间的联系的基本规律是:在改动数据输出端TxD 的XCK 时钟的相反边缘对数据输入端RxD 进行采样。

4、帧格局

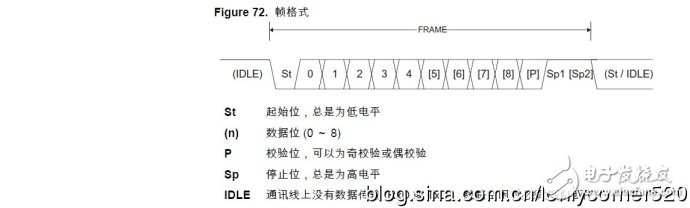

串行数据帧由数据字加上同步位( 开端位与中止位) 以及用于纠错的奇偶校验位构成。

1)数据帧格局

? 1 个开端位

? 5、 6、 7、 8 或9 个数据位

? 无校验位、奇校验或偶校验位

? 1或2 个中止位

数据帧以开端位开端;紧接着是数据字的最低位,数据字最多能够有9 个数据位,以数据的最高位完毕。假如使能了校验位,校验位将紧接着数据位,最终是完毕位。当一个完好的数据帧传输后,能够当即传输下一个新的数据帧,或使传输线处于闲暇状况。Figure72 所示为或许的数据帧结构组合。括号中的位是可选的。

数据帧的结构由UCSRB 和 UCSRC 存放器中的UCSZ2:0、 UPM1:0、USBS 设定。接收与发送运用相同的设置。设置的任何改动都或许损坏正在进行的数据传送与接纳。USART的字长位UCSZ2:0确认了数据帧的数据位数;校验形式位UPM1:0用于使能与决定校验的类型; USBS 位设置帧有一位或两位完毕位。接纳器疏忽第二个中止位,因而帧过错(FE) 只在第一个完毕位为”0” 时被检测到。

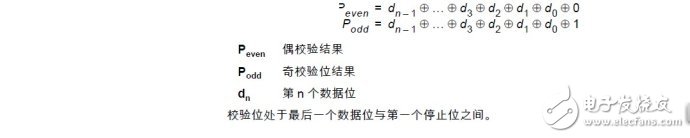

2)校验位的核算

校验位的核算是对数据的各个位进行异或运算。假如挑选了奇校验,则异或成果还需求取反。校验位与数据位的联系如下:

留意:校验位坐落最终一个数据位与第一个中止位之间。

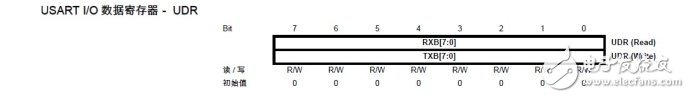

5、USART的存放器及设置

USART 发送数据缓冲存放器和USART 接纳数据缓冲存放器同享相同的I/O 地址,称为USART 数据存放器或UDR。将数据写入UDR 时实践操作的是发送数据缓冲器存器(TXB),读UDR 时实践回来的是接纳数据缓冲存放器(RXB) 的内容。在5、6、7 比特字长形式下,未运用的高位被发送器疏忽,而接纳器则将它们设置为0。只要当UCSRA存放器的UDRE标志置位后才能够对发送缓冲器进行写操作。假如UDRE没有置位,那么写入UDR 的数据会被USART 发送器疏忽。当数据写入发送缓冲器后,若移位存放器为空,发送器将把数据加载到发送移位存放器。然后数据串行地从TxD 引脚输出。接纳缓冲器包括一个两级FIFO,一旦接纳缓冲器被寻址FIFO 就会改动它的状况。因而不要对这一存储单元运用读- 修正- 写指令(SBI 和CBI)。运用位查询指令(SBIC 和SBIS)时也要当心,由于这也有或许改动FIFO 的状况

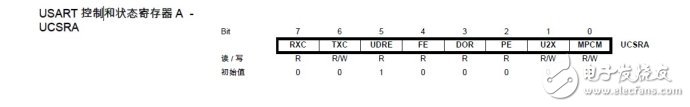

2)USART操控和状况存放器A

? Bit 7 – RXC: USART 接纳完毕

接纳缓冲器中有未读出的数据时RXC 置位,不然清零。接纳器制止时,接纳缓冲器被刷新,导致RXC 清零。RXC 标志可用来发生接纳完毕中止( 见对RXCIE 位的描绘)。? Bit 6 – TXC: USART 发送完毕发送移位缓冲器中的数据被送出,且当发送缓冲器 (UDR) 为空时TXC 置位。履行发送结束中止时TXC 标志主动清零,也能够经过写1 进行铲除操作。TXC 标志可用来发生发送完毕中止( 见对TXCIE 位的描绘)。? Bit 5 – UDRE: USART 数据存放器空UDRE标志指出发送缓冲器(UDR)是否准备好接纳新数据。UDRE为1阐明缓冲器为空,已准备好进行数据接纳。UDRE标志可用来发生数据存放器空中止(见对UDRIE位的描绘)。复位后UDRE 置位,标明发送器现已安排妥当。? Bit 4 – FE: 帧过错假如接纳缓冲器接纳到的下一个字符有帧过错,即接纳缓冲器中的下一个字符的第一个中止位为0,那么FE 置位。这一位一向有用直到接纳缓冲器(UDR) 被读取。当接纳到的中止位为1 时, FE 标志为0。对UCSRA 进行写入时,这一位要写0。? Bit 3 – DOR: 数据溢出数据溢出时DOR 置位。当接纳缓冲器满( 包括了两个数据),接纳移位存放器又有数据,若此刻检测到一个新的开端位,数据溢出就发生了。这一位一向有用直到接纳缓冲器(UDR) 被读取。对UCSRA 进行写入时,这一位要写0。? Bit 2 – PE: 奇偶校验过错当奇偶校验使能(UPM1 = 1),且接纳缓冲器中所接纳到的下一个字符有奇偶校验过错时UPE 置位。这一位一向有用直到接纳缓冲器 (UDR) 被读取。对UCSRA 进行写入时,这一位要写0。? Bit 1 – U2X: 倍速发送这一位仅对异步操作有影响。运用同步操作时将此位清零。此方位1 可将波特率分频因子从16 降到8,然后有用的将异步通讯形式的传输速率加倍。? Bit 0 – MPCM: 多处理器通讯形式设置此位将发动多处理器通讯形式。MPCM 置位后, USART 接纳器接纳到的那些不包含地址信息的输入帧都将被疏忽。发送器不受MPCM设置的影响。

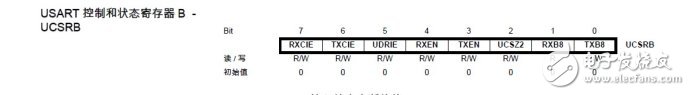

3)USART操控和状况存放器B

? Bit 7 – RXCIE: 接纳完毕中止使能

置位后使能RXC 中止。当RXCIE 为1,大局中止标志位SREG 置位, UCSRA 存放器的RXC 亦为1 时能够发生USART 接纳完毕中止。? Bit 6 – TXCIE: 发送完毕中止使能置位后使能TXC 中止。当TXCIE 为1,大局中止标志位SREG 置位,UCSRA 存放器的TXC 亦为1 时能够发生USART 发送完毕中止。? Bit 5 – UDRIE: USART 数据存放器空中止使能置位后使能UDRE 中止。当UDRIE 为1,大局中止标志位SREG 置位,UCSRA 存放器的UDRE 亦为1 时能够发生USART 数据存放器空中止。

? Bit 4 – RXEN: 接纳使能

置位后将发动USART 接纳器。RxD 引脚的通用端口功用被USART 功用所替代。制止接纳器将改写接纳缓冲器,并使 FE、DOR 及PE 标志无效。

? Bit 3 – TXEN: 发送使能

置位后将发动将发动USART 发送器。TxD 引脚的通用端口功用被USART 功用所替代。TXEN 清零后,只要比及一切的数据发送完成后发送器才能够真实制止,即发送移位存放器与发送缓冲存放器中没有要传送的数据。发送器制止后,TxD引脚康复其通用I/O功用。

? Bit 2 – UCSZ2: 字符长度

UCSZ2与UCSRC存放器的UCSZ1:0结合在一同能够设置数据帧所包括的数据位数(字符长度)。

? Bit 1 – RXB8: 接纳数据位 8

对9 位串行帧进行操作时,RXB8 是第9 个数据位。读取UDR 包括的低位数据之前首要要读取RXB8。

? Bit 0 – TXB8: 发送数据位8

对9 位串行帧进行操作时,TXB8 是第9 个数据位。写UDR 之前首要要对它进行写操作。