1、 前语

近年来,跟着嵌入式中心芯片的飞速开展,改变了传统嵌入式体系的规划办法,嵌入式体系逐步由板级向芯片级过渡,即片上体系——SOC。片上体系是寻求产品体系最大容纳的集成器材,是当时嵌入式运用领域的技能热门。SOC的呈现使集成电路开展成为集成体系,整个电子整机的功用可以集成到一块芯片中,降低了规划本钱,缩短了开发周期。因而,本文规划了一个依据FPGA的嵌入式体系,既能满意嵌入式体系教育实验的需求,一起也可作为嵌入式产品开发渠道。

2、 体系硬件规划

本体系要完结的功用包括:可以运转嵌入式操作体系;支撑NIOS II开发;支撑USB通讯;支撑RS-232串口通讯;支撑以太网通讯;支撑JTAG接口在线调试与下载。

2.1 体系硬件框图

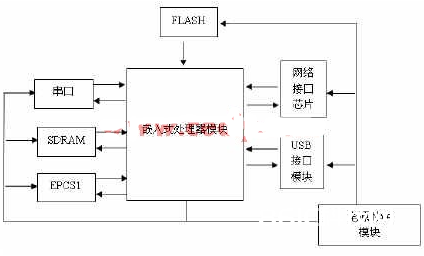

针对所需的功用,规划出体系的相应硬件渠道,硬件渠道首要是由嵌入式处理器模块、存储器模块、包括以太网接口、USB接口和电源等外部接口电路模块组成。体系硬件结构框图如图1 所示。

图1 体系硬件结构图

2.2 嵌入式处理器模块

嵌入式处理器是整个体系的操控办理中心,首要功用是完结整个体系的操控和使命调试办理。在本体系中嵌入式处理器选用ALTERA公司的Cyclone系列的EP1C12Q240C8芯片,其选用QFP封装,具有12060个逻辑单元(LE)、52个M4K 存储块、悉数RAM位数为239616、两个锁相环,以及249个可用的I/O脚, 其装备存储器选用EPCS1,编译后体系速度可以到达100MHz,支撑ALTERA 公司的SOPC内核NIOS II体系的开发,NIOS II开发环境编译后的可履行文件可以经过JTAG接口下载到开发板上的FLASH中去,可以支撑一些嵌入式操作体系,比方MicroC/OS操作体系和Clinux操作体系。

2.3存储器模块

2.3.1 专用串行装备器材EPCS1接口电路

EPCS系列器材是Altera公司供给的一种依据FLASH存储器的专用串行装备器材,其具有串行接口,接口只需求四个引脚,可以存储Stratix II 系列、Cyclone系列的FPGA的装备信息,并在体系上电或许需求重新装备FPGA时,向FPGA发送装备信息。本体系用的串行装备器材EPCS1巨细为1M字节,重复擦写次数可多达十万,可以轻松完结掉电维护

2.3.2 Flash存储器接口电路

Flash存储器具有低功耗、大容量、擦写速度快、可整片或分扇区在体系编程(烧写)、擦除等特色,因而在各种嵌入式体系中得到了广泛的运用。

体系中用了一片AMD29LV320D FLASH存储器,其单片存储容量为32M位(4M字节),作业电压为2.7V~3.6V,16位数据宽度。AMD29LV320D仅需3V电压即可完结在体系的编程与擦除操作,经过对其内部的指令寄存器写入规范的指令序列,可对Flash进行编程(烧写)、整片擦除、按扇区擦除以及其他操作。

Flash存储器在体系中一般用于寄存程序代码,体系上电或复位后从此获取指令并开端履行,由于,在进行体系全体设计时,可以经过运用Quartus II对引脚进行装备,所以关于AMD29LV320D FLASH的三个功用引脚nCE、nOE、nWE,可以各接一个EP1C12Q240C8的通用I/O脚即可。

2.3.3 SDRAM存储器接口电路

与Flash存储器相比较,SDRAM不具有掉电坚持数据的特性,但其存取速度大大高于Flash存储器,且具有读/写的特点,因而,SDRAM在体系中首要用作程序的运转空间、数据及仓库区。当体系发动时,CPU首先从复位地址0x0处读取发动代码,在完结体系的初始化后,程序代码调入SDRAM中运转,以进步体系的运转速度。一起,体系及用户仓库、运转数据也都放在SDRAM中。

体系中用了一片HY57V641620 SDRAM存储器,其存储容量为4组x16位(8M字节),作业电压为3. 3V,常见封装为54脚TSOP,兼容LVTTL接口,支撑主动改写(Auto-Refresh)和自改写(Self-Refresh), 16位数据宽度。可满意运转MicroC/OS操作体系、或许Clinux操作体系及各种相对较杂乱的算法的运转要求。

要在体系中运用SDRAM,要求微处理器具有改写操控逻辑,或在体系中别的参加改写操控逻辑电路。经过Altera公司供给的NIOS II开发东西可以将SDRAM操控器添加到NIOS CPU中,然后下载到EP1C12Q240C8中运转,因而可以便利地运用EP1C12Q240C8的通用I/O口与SDRAM相衔接,同样在进行体系全体规划时经过Quartus II界说引脚。

2.4 外部接口模块

2.4.1以太网接口规划

体系选用realteck公司推出多年RTL8019AS网络芯片。RTL8019AS芯片是一款运用广泛的10M网络芯片,支撑以太网II 和IEEE802.3 10Base5,10Base2,10BaseT、支撑可编程输出的4-确诊 LED。运用RTL8019AS可以在NIOS II体系中便利的树立起完好的网络服务器,可以经过网络从FPGA芯片构成的软嵌入式体系中收发数据。

RTL8019AS与EP1C12Q240C8经过外部总线进行衔接。首要是把RTL8019AS的数据总线(SDO~SD15)、地址总线(SAO~SA5,SA8)、读使能(IORB)、写使能(IOWB)、中止输出信号(INTO)和中止输入信号(RSTDRV)与EP1C12Q240C8的通用I/O脚衔接即可。

2.4.2 USB接口规划

体系选用Cypress公司的SL811HS芯片作为USB接口芯片,它是一种USB主机操控器,它能与全速或低速USB外围设备通讯。SL811HS能与各种微处理器、微操控器、FPGA以及DSP,ISA等各种总线进行接口,适用于各种要求装备USB主机或设备的嵌入式体系。

在USB接口电路规划中,SL811HS的8位数据线直接和FPGA芯片的8位数据线相连。其间需求留意的是,SL811HS的AO引脚和低8位地址线的最低位AO相连,即与锁存器的地址输出端的最低位相连。

2.4.3 串行接口规划

RS232是运用最为广泛的UART接口,可以便利的完结与计算机的数据通讯;一起在调试依据FPGA的嵌入式操作体系时分,可以作为辅佐调试接口,成果输出到主机的超级终端上面。由于FPGA的通用I/O引脚可以在后期经过Quartus II软件界说,所以只需选取EP1C12Q240C8的恣意四个引脚与电平转化器MAX3232C相连,经过MAX3232C 接RS232规范串行接口(DB9),可与PC机进行串行通讯。

2.4.4 电源接口规划

体系需求运用1.5V、3.3V和5V三种直流电源,其间,EP1C12Q240C8内核运用1.5V电源,EP1C12Q240C8的I/O口、MAX3232C、LCD接口等器材运用3.3V电源,RTL8019AS运用5V电源。为简化体系电源电路的规划,要求整个体系的输入电压为高质量的5V直流电压电源,本体系选用电压转化芯片B1117来得到1.5V和3.3V的电压。

2.4.5 体系时钟电路规划

体系时钟模块为实验体系供给时钟信号,使其作业在指定的频率下,是体系不行短少的部分。本体系的时钟信号由50MHz的有源晶振发生,为了使体系有安稳的时钟输入,要对晶振的输入电压经过简略的LC滤波电路做滤波处理,使其电压愈加安稳,尽可能减小搅扰。

2.4.6 复位电路规划

在体系中,复位电路首要完结体系的上电复位和体系在运转时用户的按键复位功用。本体系依据实践需求,经过Quartus II软件对复位信号进行延时规划,然后在外部再加以需求简略的电路来完结。

2.4.7 JTAG接口规划

JTAG(Joint Test AcTIon Group)是一种国际规范测验协议,首要用于芯片内部测验及对体系进行仿真、调试 。JTAG技能是一种嵌入式调试技能,它在芯片内部封装了专门的测验电路,可以经过专用的JTAG测验软件对芯片内部节点进行测验。EP1C12Q240C8有四个专用引脚TMS、TDI、TCK、TDO与Altera公司的专用下载电缆——Byte Blaster II经过一个十针的插座相连,用于下载以及在线调试。

3、 体系软件规划

本体系首要的开发调试东西有SOPC Builder、Quartus II和 NIOS II IDE。SOPC Builder是一个主动化的体系开发东西,它可以极大地简化高性能SOPC的规划作业;Quartus II是Altera公司推出的CPLD/FPGA开发东西,Quartus II供给了彻底集成且与电路结构无关的开发包环境,具有数字逻辑规划的悉数特性,首要用于system-on-a-programmable-chip (SOPC)的规划环境;NIOS II IDE是NIOS II系列嵌入式处理器的根本软件开发东西。一切软件开发使命都可以NIOS II IDE下完结,包括修改、编译和调试程序。

3.1.体系软件装备

选用NIOS处理器开发规划与选用传统的处理器开发规划不同,开发者有必要先装备处理器结构、设置接口等内容。也就是说,开发者有必要依据实践需求构建一个处理器,而传统的处理器具有固定接口、片内RAM和外部设备。体系规划所需的详细软件装备如下:

(1)用SOPC Builder体系归纳软件来进行NIOS软核的软件装备,包括NIOS CPU装备、片上ROM及RAM设置、FLASH设置、SDRAM设置、JTAG调试装备、参加定时器、参加外部RAM总线——Avalon三态总线桥、通讯接口、按键PIO与LED PIO设置、指定基地址和装备NIOS软核,这样整个NIOS软核现已装备结束,之后需求编译,并生成图形文件,成为Quartus II规划的一部分。

(2)运用Quartos II软件来选取详细的Altera可编程器件系列,并对SOPC Builder生成的HDL规划文件进行布局布线;再运用Quartos II软件选取方针器材并对NIOS II体系上的各种I/O口分配管脚,别的还要依据要求进行硬件编译选项或时序束缚的设置。在编译的进程中,Quartos II从HDL源文件归纳生成一个合适方针器材的网表。最终生成装备文件。

(3)运用Quartos II编程器和Altera下载电缆,将装备文件下载到开发板上。当校验完当时硬件规划后,再将新的装备文件下载到开发板上的非易失存储器里。

3.2.嵌入式实时操作体系MicroC/OS-II的运用规划

现在比较盛行的嵌入式操作体系首要有MicroC/OS-II , MicroCLinux,VxWorks等,考虑到体系资源以及NIOS II IDE 开发环境包括MicroC/OS-II实时操作体系,为规划者供给快速地树立依据NIOS II处理器的MicroC/OS-II运用程序的才能,, 故本体系的操作体系选用MicroC/OS-II 。MicroC/OS-II 是一种可固化、可取舍、占先式的多使命实时操作体系内核。它为每个使命分配独自的仓库, 供给多种体系服务可进行中止办理。

创立一个依据NIOS II处理器的MicroC/OS-II软件进程包括以下过程:创立一个新的NIOS II IDE工程;设定MicroC/OS-II软件工程库;树立并运转NIOS II 下的MicroC/OS-II软件工程。

一、 创立一个新的NIOS II IDE工程

创立一个新的NIOS II IDE工程的办法比较简略,根本上依照导游就能完结,要留意的是在 Project Template(工程模板)挑选中, 要挑选 the MicroC/OS-II Tutorial,在New System Library Dialog Box 页面中的Select Type of system library栏中要挑选MicroC/OS-II。

二、设定MicroC/OS-II的过程

(1). 在NIOS II IDE的C/C++ Projects视图中,右键在体系库上单击std_system_lib。

(2). 在弹出的菜单中挑选ProperTIes翻开ProperTIes对话框。

(3). 单击System Library显现system library选项。

(4).单击在RTOS 下面的RTOS OpTIons。弹出MicroC/OS-II RTOS Options对话框。

(5).单击“+”在在左面的面板中,翻开MicroC/OS-II目录。MicroC/OS-II是高度映射可设定的。你选定的对话框中的选项被保存在os_cfg.h文件中。选定的MicroC/OS-II选项被包括在二进制中。经过单击MicroC/OS-II下每一个选项查看你所能挑选的选项。

(6).挑选默认设置单击OK。你将回来体系库选项对话框,然后单击OK完结设置。

三、树立并运转NIOS II 下的MicroC/OS-II软件工程

在这一部分,在嵌入式体系中规划并运转一个MicroC/OS-II程序,经过在嵌入式操作体系MicroC/OS-II下编写2个相互调用使命来测验本体系的运转状况。

1.翻开ucosii_tutorial.c

2.头文件参加如下代码

#include “system.h”

#include “altera_avalon_pio_regs.h”

#include “alt_types.h”

3.参加相关界说

#define TASK_STK_SIZE 1024

#define TaskStart_ID 0

#define Task1_ID 1

#define Task2_ID 2

#define TaskStart_Prio 1

#define Task1_Prio 4

#define Task2_Prio 3

OS_STK TaskStk[N_TASKS][TASK_STK_SIZE];

OS_EVENT *AckMbox;

OS_EVENT *TxMbox

4.在初始化函数 initCreateTasks函数中参加如下代码

OSTaskCreateExt(TaskStart, 0, &TaskStk[0][TASK_STK_SIZE-1], TaskStart_Prio, TaskStart_ID, &TaskStk[0][0], TASK_STK_SIZE, 0, OS_TASK_OPT_STK_CHK );

OSTaskCreateExt(Task1, 0, &TaskStk[1][TASK_STK_SIZE-1], Task1_Prio, Task1_ID, &TaskStk[2][0], TASK_STK_SIZE, 0, OS_TASK_OPT_STK_CHK );

OSTaskCreateExt(Task2, 0, &TaskStk[2][TASK_STK_SIZE-1], Task2_Prio, Task2_ID, &TaskStk[3][0], TASK_STK_SIZE, 0, OS_TASK_OPT_STK_CHK );

5.添加履行2使命相互调用的代码

void Task1(void * pParam)

{ //往接纳音讯行列发送A

char txmsg;

INT8U err;

txmsg = ‘A’;

while(1)

{

OS_ENTER_CRITICAL();

printf( “Hello from task1\n” );

OS_EXIT_CRITICAL();

OSMboxPost(TxMbox, &txmsg);

OSMboxPend(AckMbox, 0, &err);

OSTimeDly(2);

}

}

void Task2(void * pParam)

{

char *rxmsg;

INT8U err;

while(1)

{

rxmsg = OSMboxPend(TxMbox, 0, &err);

OS_ENTER_CRITICAL();

printf( “Hello from task2\n” );

OS_EXIT_CRITICAL();

OSTimeDly(2);

OSMboxPost(AckMbox, (void*)1);

}

}

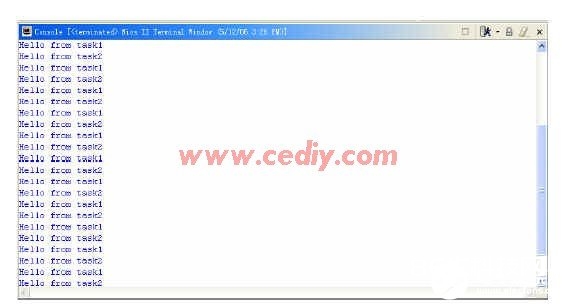

6、 挑选Run As 》 NIOS II Hardware (Run menu中)创立程序,下载它到实验板中并运转。下载完结后,当履行这两个使命时,使命一回来:“Hello from task1”;而使命二回来:“Hello from task2”,两个使命之间相互调用。

得到测验成果如图2:

图2 MicroC/OS体系测验成果

从测验成果中可以看出,使命一和使命二被重复的调用,这与预期中履行的成果相同,阐明体系可以在FPGA中安稳运转。

四、结束语

本文介绍的依据FPGA的嵌入式体系规划到达了预期作用, CPU 自身是以软核的方法完结, 其功用可依据需求进行定制, 十分灵敏。嵌入式MicroC/OS-II 操作体系的32 位嵌入式微处理器进行中心操控,运用它强壮的运算处理才能,不只减少了体系所用的器材数量和体系的尺度,更进步了体系的可靠性和灵敏性。该规划为嵌入式体系规划供给了一条新思路,表现了FPGA的灵敏性、高集成性等特性,大大降低了本钱,缩短了开发时刻。

责任修改:gt