片上体系(SoC)开发不再仅仅是简略的硅芯片开发进程。现代设备许多运用了各种软件,包含软件栈、中间件、发动代码和驱动程序。你大可悠然自如地比及硅芯片开发完结后,再将其放在电路板上开端进行软件的开发。可是在剧烈的市场竞赛中,时刻便是生命。开发进度日益急迫,若能在硅芯片制作完结前便着手进行软件开发,将成为一个巨大的竞赛优势。要做到这一点,需求满意以下三个要求:首要,需求一套可供寄存器传输级(RTL)规划高速运转、且在硅芯片或开发板准备就绪前就能在上面正常运转软件的仿真体系;此外,还需求一个高速、根据业务的协同建模通道将仿真器与根据作业站的软件调试东西进行衔接;终究,还需求供给契合软件开发者需求的软件调试环境。

为一种硬件还没有成型的产品开发软件时,首要需求一个能运转代码的环境。一般有两种挑选:物理环境或虚拟环境。大多数项目都是根据某个现有规划,即在原有版别中增加某些功用,使原有版别功用更强、速度更快、功用更好。这种情况下,有或许从接手项目的原有规划版别中直接获取现成的电路板,或许能取得该电路板的软件环境以进行软件开发,用自己的调试环境来对其进行验证。到目前为止,最简略的做法便是在现成的电路板上运转。假如是开发一个全新的软件,你能够运用一块开发板,命运好的话,或许还能找到相似的开发板。还有一种可行的办法,即在一个虚拟电路板上运转,如虚拟机(QEMU)。QEMU是一个开源体系仿真器,可随意模仿各种ARM板。ARM公司也供给一个虚拟渠道,称作“根底模型”(可在其网站上免费取得),相似于QEMU,可运转ARM代码。二者都有引入调试器的东西。

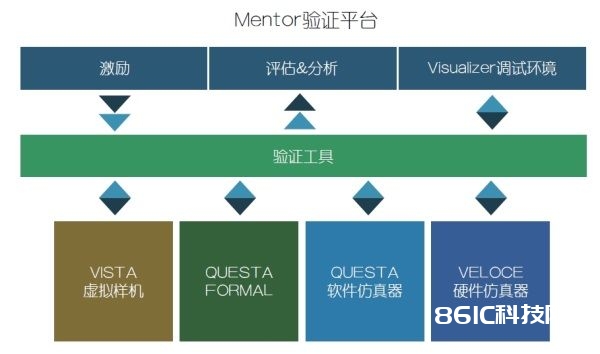

图1:Mentor公司验证渠道将先进的仿真器解决方案、硬件加速器渠道以及强壮的调试环境整合在一个全球同享的高功用数据处理中心资源里。

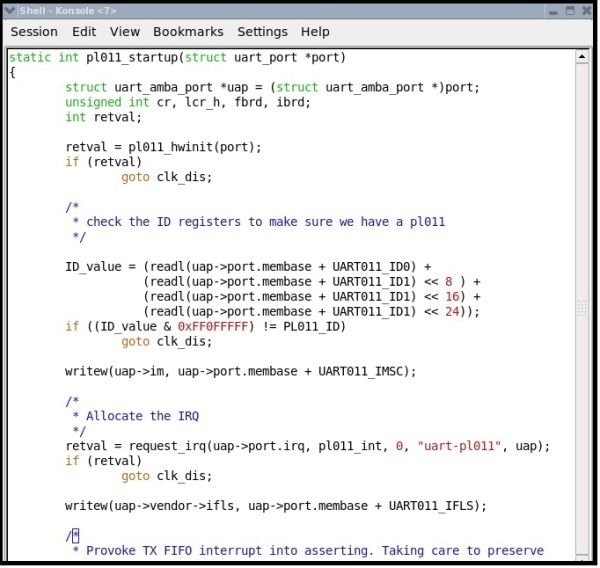

有了可运转和调试代码的环境,就能够开端编程了。某些情况下,你将需求拜访一些还未成型的全新外围设备,应对此问题的一个解决方案是创立一个模型。咱们先从一个十分简略的比如下手:读取这个新外围设备的ID寄存器。许多外围设备都有ID寄存器,这是一个只读寄存器,读取时回来固定的已知数值。这就如同让驱动程序多了少许自傲,让其意识到设备在与正确的外围设备通讯。很早以前,在驱动程序初始化时,读取寄存器并将其与预期进行比较便是一件较为灵敏的作业。以下是一个ARM pl011串口驱动程序的比如:

图2:校验一个新外围设备的ID寄存器

驱动程序代码运用宏readl和writel对寄存器进行读写。这些在linux内核中界说的驱动程序被作为一种拜访硬件的办法。但假设发动了一个新的驱动程序,你就能够在本地进行从头界说,以得到所需的呼应。例如:

你无需拜访实践硬件,便能开端进行软件开发。当然,你也能够采纳极点的做法,运用这种办法来建模一个完好的外围设备,但无论如何请不要测验最简略的外围设备,由于那样很简单发生毛病。一旦呈现握手失利而采样依然在进行,体系或许会丢掉某些回来值。

假设处于虚拟环境,如QEMU或ARM快速模型(AFM)—根底模型的付费版别,你能够引入愈加杂乱的模型。AFM衔接了System-C,比较于存根代码(stub-code),这是一种更适宜于建模硬件行为的环境。QEMU也能够扩展模型,但经历不是随便而来的,需求经过屡次实践。与许多开源项目相同,代码便是文档。若运用了QEMU,但又不想在一团糟的C代码中苦苦挣扎并测验理出条理,那么一旦你需求逾越存根代码,你或许想要越过这个阶段。

许多情况下,无法运用存根代码进行验证,乃至连你为软件运转所创立的更杂乱的System-C模型也力不从心。例如,你无从得知硬件团队和软件团队在设备中运用的是否为同一个寄存器映射。经过一个不会做出任何意料之外的反响的寄存器,你底子无从验证其设置是否正确。假如你一起编写驱动程序和相应的外围设备模型,那么也只能证明你对二者的了解是相吻合的。

虚拟样机体系,如Mentor Graphics的Vista,可用于创立你所需的更杂乱化的模型。一般情况下,这些模型的处理速度十分快,软件运转也很顺利。假如硬件团队创立了虚拟样机模型,那么在该模型上运转软件时,便能验证软硬件团队的规划观念是否相符。一般情况下,二者的规划观念是存在差异的。若能尽早发现这些差异,则在规划周期的后期可防止不少费事,让你不至于抓狂。在一个软硬件都很简单调试的东西中,要完成这一点其实并不难。

虚拟样机有一个你所开发的软件外围设备的完好功用模型。你将能以创立终极目标体系相同的办法来创立自己的软件,还能拜访外设的寄存器,就像在实在的硬件上运转相同。此外,经过虚拟样机能够直接检查这些外设寄存器,在无任何搅扰的情况下,调试进程变得更简单。你将能充分地编写驱动程序并验证其运转是否正常。你乃至还能够大略核算出一共所需求的时刻。可是,准确的验证时刻的核算,还需比及与硬件更匹配的软件面世。

需求记住的是,虚拟样机并不是真实的硬件,而仅仅一个模型。模型(以程序的方式)需求由规划师来编写,但规划师所编写的程序偶然会呈现过错。还需求注意的是,硬件在一个很笼统的层面上建模,这能够引发实践硬件的奇妙、却又至关重要的差异。因而,即便驱动程序彻底验证了虚拟样机,你的作业依然没有结束,还需求在更具体的硬件环境中进行验证。

硬件团队现已创立了可履行的硬件模型,作为正常开发周期的一部分。他们在寄存器传输级(RTL)运用一种硬件描绘言语(HDL)来描绘自己的规划。终究,经过一系列运转编译器和分析器来运转该规划的HDL描绘,创立掩模组以用于制作硅芯片。HDL可在仿真软件上运转,并供给待出产硬件的时钟周期的准确运转状况。仅有的问题是,大部分以HDL描绘的实体规划模仿器只能以几十或几百赫兹的频率运转,无法到达兆赫,乃至连千赫都很困难,关于软件程序员来说,这种频率低得简直毫无用处。相同的HDL可用于编写可编程逻辑器(FPGA)或硬件加速器,如Mentor Graphics的Veloce.FPGA和硬件加速器可完成HDL所描绘的行为,但它们的运转速度是兆赫级的。关于软件工程师来说,这一速度依然不行,可是至少是可用的。

一旦你现已运用了存根代码和虚拟样机的悉数功用,假设有一个是可用的,那么下一步便是在一个愈加准确的硬件模型上验证你编写的代码,具体来说,便是RTL.开端这一过程的最佳办法是将虚拟机(QEMU或AFM)与硬件的RTL模型结合起来,在软降仿真器或硬件加速器中运转。Mentor Graphics的产品Warpcore使这种办法成为或许。它将虚拟机与RTL履行环境进行了结合,仅在RTL被拜访时才运转RTL仿真器。将虚拟机与仿真环境相结合,以几百赫兹的频率运转,看似张狂,可是在不过度运转硬件的情况下,这种做法是可行的。假如硬件只运转一百万个时钟左右,履行作用会很好。一般情况下,仿真器更易于树立、拜访和调试。一旦你需求使硬件运转超越一百万个时钟周期,则需求运用硬件加速器以完成更优秀的功用。