VC5509A包括I2C外设接口,可以便利的与ADXL345通讯。在调试中,运用了实验室克己的DSP主板SDUST VC5509A V1.1。该板的JP2扩展接口引出了I2C总线。该主板上也运用I2C总线完结与AIC23B的装备,但因为I2C总线可挂置多个外设,所以无需再衔接一片ADXL345,不会有影响。

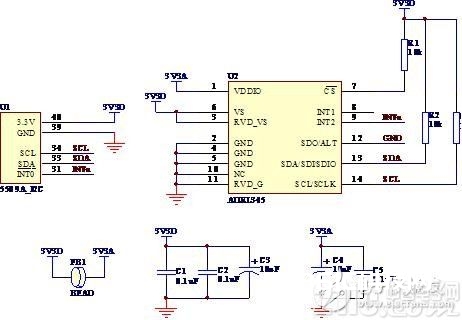

因为ADXL345不容易焊接,所以在买芯片时也购买了飞拓电子的PCB板。在该PCB板上现已增加了去耦电容、上拉电阻等。下图为VC5509A主板与ADXL345模块的连线示意图。

ADXL345与5509A主板连线(I2C)示意图

剖析原理图,ADXL345需求3.3V供电,直接运用5509A主板来供给,而不运用345小板上的5V转化,所以5V引脚空缺即可。CS引脚悬空,因为在模块中现已将其上拉,标明选用I2C形式通讯。将SDO下拉,I2C地址为0x53(若上拉,I2C地址为1D)。将INT1n输出与主板的INT0n相连,将SDA和SCL线对应衔接。图中标示的U1引脚为5509A主板上扩展口JP2对应的引脚编号。

下图为完好的原理图:

ADXL345与5509A主板连线(I2C)原理图

调试关键小结:

1)ADXL345的中止默许是高电平有用,而5509A默许是低电平有用,所以开端要修正一下。经过设置DATA_FORMAT(0x31)寄存器中的DATA_INVERT位,将其置1即标明低电平有用。

2)修正CPLD代码,将INT0输出由1改为高阻抗。

3)可经过读取寄存器DEVID,来判别I2C读是否正常。该寄存器的数据固定为0xE5,若数据读取正确,则标明I2C读取函数编写无误。

4)接连读取寄存器,会呈现总线忙的过错,需求在读取数据结束后增加一必要的延时。

5)调试总结发现,尽管5509A的手册中写明外部中止是低电平有用的,但实践应为下降沿有用。因为ADXL345运转状况的不确定性,在使能中止前,INT1输出就可能现已拉低了。这时即使使能外部中止,也无法按料想的进入中止子程序。需求想办法将INT1 铲除一次,这样才有时机触发中止。所以在中止使能后,经过读取寄存器的方法来完成铲除中止,以触发中止循环。

6)发现CSL中的I2C读写函数适当耗费时刻。调查其大约占用380000个指令周期,在144MHz的速率下,大约耗费2.6ms。而设定的ADXL345的数据输出速率为200Hz,远远跟从不上。在每个中止中,至少需求7个读写指令,单纯这部分的耗时就达到了18.2ms。也就是说当运用I2C总线时,ADXL345的数据输出速率最高只能设为50Hz。

7)最终测验,将速率设置为25Hz,经过示波器调查中止,大约40ms中止一次,对应25Hz。中止的低电平时刻根本共同,阐明可以规则的进入中止。将速率设置为50Hz,调查中止,大约20ms中止一次,对应50Hz。进入中止也比较规则。当设置为100Hz时,中止不再呈现周期性,低电平坚持时刻也不共同。阐明呈现了中止嵌套的现象。与揣度共同。