仿真测验是EDA规划进程中验证逻辑功用正确性的重要手法.因为验证的复杂度随规划规划成指数添加,关于占用5000以上逻辑单元(约十万等效门)以上的EDA规划而言,其鼓励信号的注人与仿真成果的剖析难以手动进行.规划者一般需求凭借EDA开发环境外的其他工程东西,或结合其他高档程序规划言语来完结.

但是,上述研讨中的鼓励数据虽具有可装备的特色,但注人这些数据的触发办法却短少可装备才能.例如龙芯2号的仿真验证[41运用了可装备的随机程序生成器 CPRG(Configurable Random Program Generator)来发生测验向量,然后大大进步了功率和测验覆盖率.但因为仅运用了守时触发的办法,该体系仅在仿真初始化阶段进行注人,相似的事例还有.这种守时触发的仿真办法与仿真进程短少交互,因而与实在体系存在较大不同.特别是关于需求依据仿真进程中某个信号的状况来注人毛病或搅扰信号,以检测电路的容错才能的事例,选用守时触发办法往往难以达到所需的验证作用.

选用事情触发办法能够处理守时触发的种种坏处.但是要完结触发事情的可装备,有必要先完结测验台代码的可装备一 个典型的比如是信号处理体系.Husmann等选用了Perl脚本编写的装备办理模块来办理事前编写的测验台和测验向量,并保护仿真成果记载.装备办理的引人使得该体系具有必定的灵活性.但因为测验台仍需事前编写,不能称为彻底的可装备仿真验证体系.

本文提出一种针对十万门以上规划集成电路的可装备仿真测验办法,运用装备脚本作为输入,经过CTG(Configurable Testbench Generator)主动发生测验台代码,完结了触发事情的彻底可装备.本办法生成的测验体系中注人逻辑与数据文件别离,依然能够经过Matlab等工程软件生成测验向量.试验标明该办法可防止重复编码带来的低功率和可靠性的下降,并节约保存仿真状况所需的存储空间.

1 可装备的仿真验证体系

1.1 基干CTG的仿真验证环境

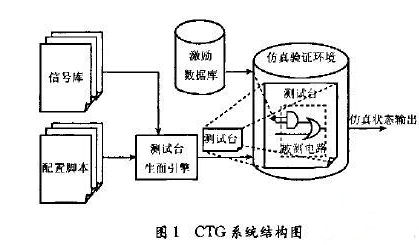

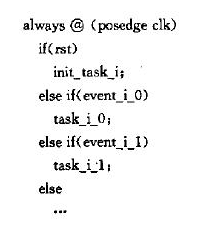

依据可装备测验台生成器 CTG的仿真验证环境是完结可装备的事情触发办法的条件,它包括信号库、装备脚本、测验台生成引擎、鼓励数据库和仿真验证环境,如图1所示.信号库界说了待测体系的信号调集.装备脚本界说了鼓励、触发办法、事情与记载点,这些信息构成测验台生成规矩,完结了触发事情的可装备.测验台生成引擎是体系的中心,它依据装备脚本指定的规矩主动发生测验台代码,测验台代码中包括对被测电路的引证.鼓励数据库包括所需注人的数据以及其所对应的相关于触发点的注人时刻,鼓励数据依然能够依照上述的办法发生,对此本文不作深人评论.

1.2 数据结构

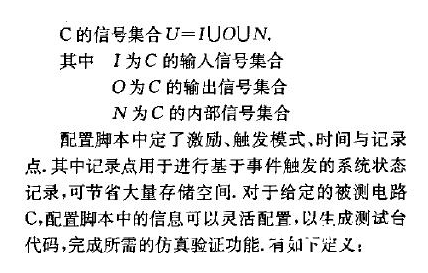

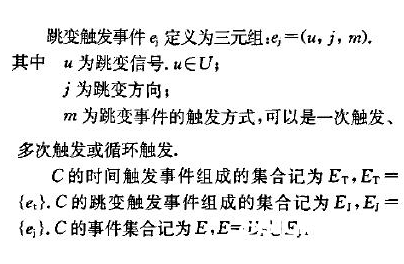

用于描绘可装备测验台发生规矩的信息存储在信号库和装备脚本中,这些信息的逻辑结构如下.信号库界说了信号调集,关于给定的被测电路C,信号库中的信息固定不变.有如下界说:

界说 1 信号调集

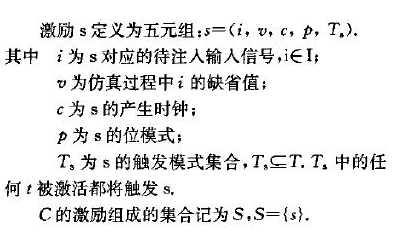

界说2 鼓励(Stimulation)

界说3 触发办法(Trigger)

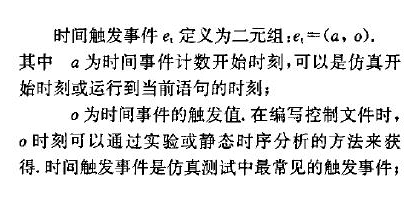

界说 4 时刻触发事情

界说5 跳变触发事情

界说6 记载点

1.3 测验台生成

1.3.1 测验台结构

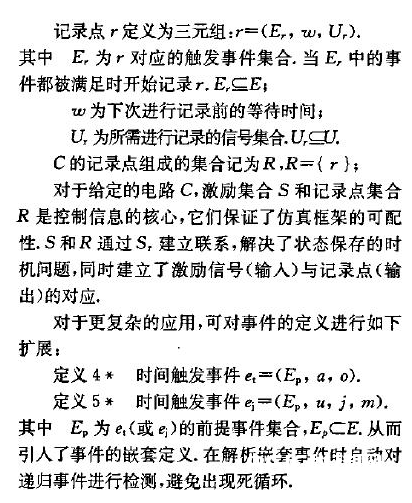

由CTG生成的测验台具有如下结构,如图 2所示

关于待注人信号sig_i,或待存储信号调集U_i,其触发条件具有如下办法:

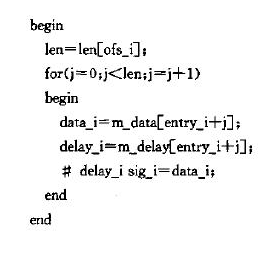

关于待注人信号sig_i,其注人使命具有如下办法:

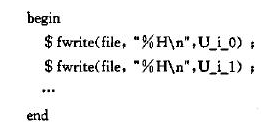

关于待存储信号调集U_i, 其存储使命具有如下基本办法:

为了便于剖析所存储的数据,实践保存数据时往往加人一些附加信息,如当时时刻、信号编号等.详细格局取决于所运用的离线剖析东西,本文对此不进行详细评论.

1.3.2 注入事情解析

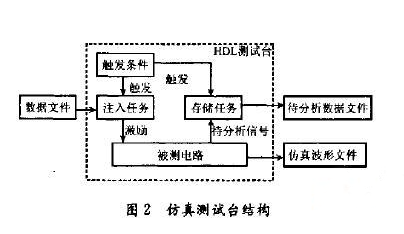

因为不能在多个always块中对同一信号赋值,因而有必要遍历鼓励调集,并依照待注人信号提取触发条件加人同一always块中.鼓励信号注人事情的解析环绕鼓励调集S打开,算法如下:

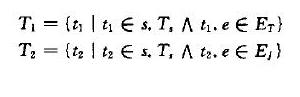

在复位状况,各鼓励s未激活,此刻s.i被驱动为指定的缺省值s.v,加人初始化使命.CTG关于S中给定的每个s=(i,v,c,P,Ts),生成如下调集:

关于T1中的各触发办法t1,CTG生成 t1.e对 应的计数器,将计数器的超时信号加人s.t触发条件的if句子中,并在if程序体中依照t1.d的设定生成对应的注人使命.

关于T2中的各触发办法t2,CTG生成t2.e.u与t2.e.j比较的表达式,加人s.i触发条件的if句子中.关于t2.e.m不为循环触发办法时还需生成对应的计数器,一同将计数器未满条件加人if句子.最终在if程序体中依照t2.d的设定生成对应的注人使命.

1.3.3 存储事情解析

体系仿真状况的保存相同受事情触发,但并不要求在同一块句子中进行存储,因而其结构相对简略.算法如下:

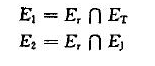

CTG关于R中给定的每个r=(Er,w,U1)生成如下调集:

关于E1中的各事情e1,CTG生成对应的计数器,将这些计数器的超时信号组成逻辑与表达式。

关于E2中的各事情e2,CTG生成e.u与e.j比较的表达式,并与超时信号与表达式一同组成逻辑与表达式.该表达式加人r.Ur触发条件的if句子中,并在if程序体中生成对应的存储使命.

2 试验验证及剖析

2.1 测验目标与试验环境

可装备仿真测验结构被用于自主研制的1553B总线协议IP核、依据类EIA架构的双核SIP处理器模型、可重构的ATPA处理器模型等仿真测验中.以1553B总线协议IP核为例:该IP核选用VerilogHDL编写,由45个模块组成.这些模块经过编译生成时序仿真库,并被包括在仿真测验台的顶层模块中.需注人的鼓励信号包括:来自外部处理器的读、写、片选信号、数据总线、地址总线、DMA呼应信号、以及 1553B总线数据.

需求保存的状况信号包括:存储器数据、1553B总线数据、要害寄存器数据(状况字、指令块指针、当时指令字)、以及体系主状况机的状况改变数据经过映射,该 IP核在 Altera的 Cyclone EPIC12器材中占用2882个逻辑单元,主时钟频率为12MHz.

仿真试验在运用IntelPentium42.6GHz处理器、512Mbyte内存的PC机上进行,运用Quartus115.0软件进行归纳与映射,运用 ActiveHDL.6.2软件进行仿真.

2.2 试验成果剖析

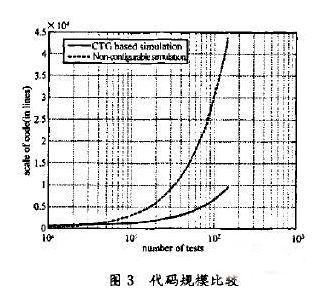

在IP核的每种典型装备下,BC办法和RT办法除了正常传输外,别离需求83套和60套毛病鼓励注人逻辑.在这145套鼓励逻辑下别离注人1024组数据进行了试验.试验体系中测验台生成引擎选用 C++言语编写,代码量约700行.仅需经过修正装备脚本便可运用CTG生成上述测验台.其间装备脚本规划在50~70行,所生成的测验台代码约为250~350行.所需编写的代码量比照如图 3所示.

从图3能够看出,跟着仿真次数的添加,运用依据CTG的仿真验证体系所需编写的代码量远小于不行装备的仿真验证体系.

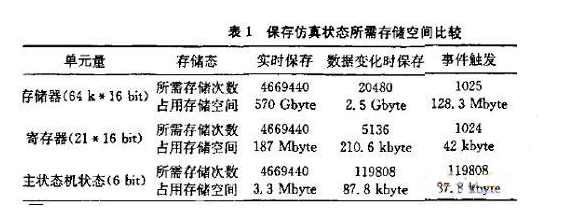

运用依据CTG的事情触发进行仿真状况存储可节约存储空间.以试验体系在BC办法下完结1024组正常数据传输为例,保存三种典型信号的仿真状况所需的存储空间比照如表 1所示(不包括存储时戳所需的空间.)

表1中的数据标明,关于不需求频频存储的仿真信号,选用事情触发机制可大大削减存储空间的开支.值得注意的是,动态发生测验台后需求从头编译仿真库,然后发生了额定的时刻开支 在2.1节介绍的试验环境中,仿真库的编译用时小于1s,仿真初始化需17s,每仿真100组数据约用时700 900由此可知仿真进程累计用时约289.2~369.8h,其间编译仿真库的开支小于145s,可忽略不计.

3 定论

本文提出的可装备仿真验证办法适用而不只限于十万门以上的超大规划 EDA规划,相关于已有研讨具有下列特色:

(1)依据事情的触发机制,更挨近实在体系

(2)可装备,主动发生测验台代码,削减编码量进步可靠性

(3)节约保存仿真状况所需的存储空间一同,因为具有可装备才能,一旦完结测验台生成引擎仅需修正信号库和装备脚本就能用于不同电路规划的仿真验证.