AD的简略常识

AD,便是将模仿量转变为数字量的进程,一般分为取样、坚持、量化、编码这4步。

因为模仿信号在时刻上接连的,而数字信号在时刻上离散的,所以转化时首要有必要按 数字信号的节拍,对被转化的模仿信号采纳样品。取样(Sample)的原理如图示。

开关受取样脉冲信号S(t)操控,S(t)=0时,开关断开,取样输出V1(t)=0;S(t)=1时,开关导通,V1(t)=V(t)。这样就把接连的模仿信号V(t)变成了一个个脉冲信号。

采样定理:取样信号S(t)的频率fs大于或等于模仿信号f(t)的最高频率Fmax(其频带的上限频率)的2倍,

则输入信号V(t)的主要特征都能够被保存下来,将来能够通过滤波处理,从V1(t)中康复本来的信号V(t)。

AD的采样频率和转化时刻。

AD的采样频率取决于发动AD的速度,发动AD转化的办法有许多,例如软件直接发动,或许使用EV的一些事情来发动,

发动的频率才是AD采样的频率,例如每隔1ms发动1次,则AD选用频率为1K。而AD时钟和AD的转化时刻有关,和AD采样频率是无关的。

2812内部ADC的特色

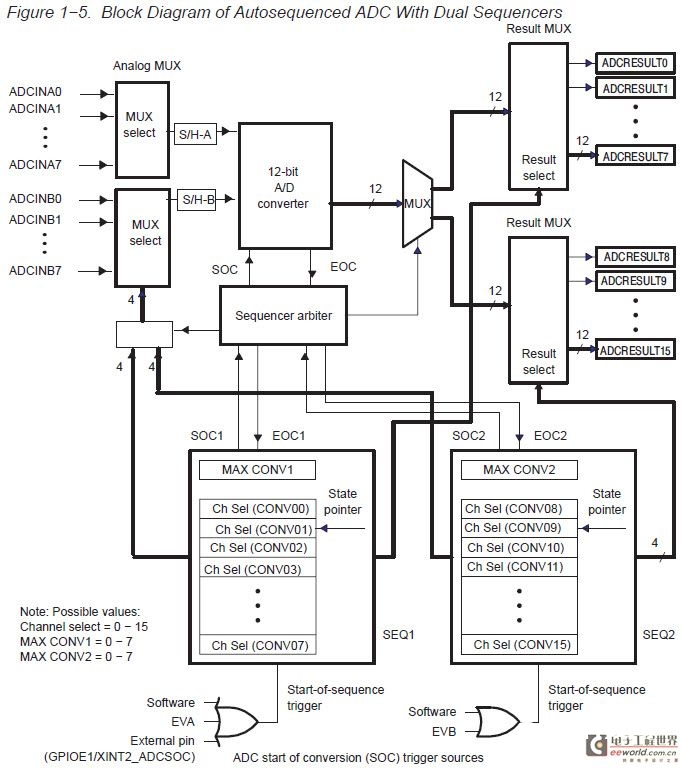

2812的ADC模块是一个12位分辨率的、具有流水线结构的模数转化器,具有16个通道。

关于每个序列发生器,一旦转化完毕,已挑选采样的通道值就会被保存到各个通道的成果寄存器中去。

总共有16个成果寄存器Result Reg0—Result Reg15,用于别离保存16个通道的转化成果。

2812 ADC的功用

1.12位的ADC内核,内置2个采样坚持器(S/H-A,S/H-B)。

2.采样形式能够为次序采样(Sequential Sampling)或许是同步采样(Simultaneous Sampling)

3.模仿输入规模为0—3V(需求留意,输入不行超越3V,不然烧坏2812)一般输入最大值在3V的70%左右,为防止如果,一般先即将采样的信号通过运放处理(基准电压源偏置),

使输入电压规模在AD正常作业采样规模之内,在信号进DSP的AD口时,最好加一嵌位二极管。

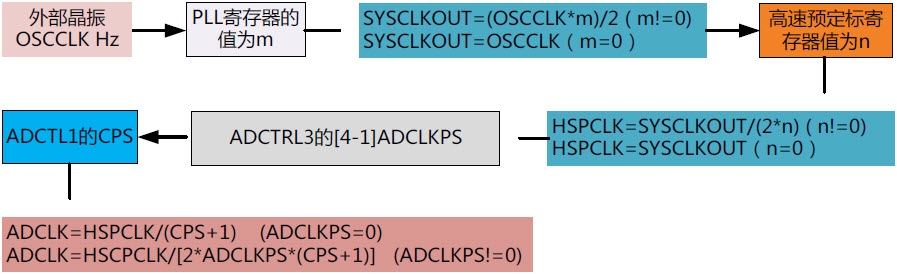

4.快速转化时刻运转在25MHZ,ADC时钟或许12.5MSPS(每秒完结12.5个百万次的采样。)

5.总共为16路输入通道,可编程多路挑选输入。16路采样输入通道被分成了两组,每组8个,别离是ADCINA0……ADCINA7和ADCINB0……ADCINB7。

A组对应于采样坚持器S/H-A,B组对应于采样坚持器S/H-B。

6.主动序列化,在单一事情段最大能够供给16个主动A/D转化。

7.序列发生器能够按两个独立的8状况序列发生器(SEQ1和SEQ2)来运转,也能够按一个16状况的序列发生器(SEQ)来运转。

8.共有16个转化成果寄存器来保存转化数值

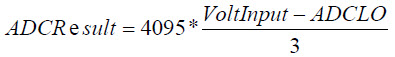

式中:ADCLO为AD转化的参阅电平,在实际使用的进程中,一般将其与GND衔接,因而此刻ADCLO的值为0。

4095=2^12-1,对应于满量程输入为3V时的转化成果

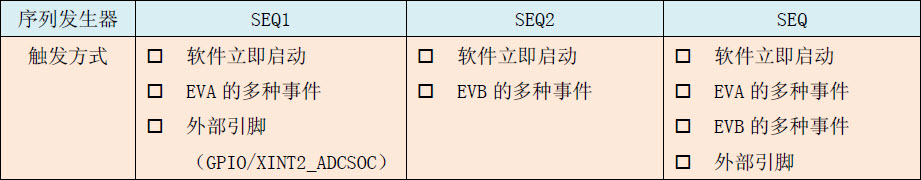

9.有多种触发办法来发动AD转化(SOC=start of conversion),包含:软件直接发动S/W,EVA的事情源,EVB的事情源和外部引脚发动。

10.序列发生器能够运转在发动/中止形式。

11.采样-坚持的收集时刻窗口能够预先设定。(ADCTRL1的位ACQ_PS3—ACQ_PS0决议了收集窗口的巨细,这一位操控了SOC脉冲的宽度,也便是一开端开关S(t)的导通时刻。

SOC脉冲的宽度是(ACQ_PS+1)*ADCLK。)

ADC时钟

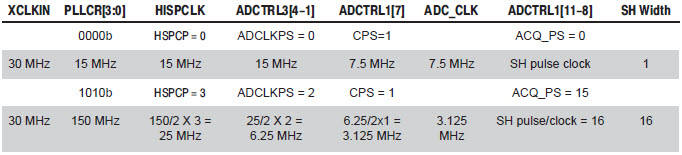

Example.Clock Chain to the ADC

ADC作业形式

次序采样、同步采样(AdcRegs.ADCTRL1.bit.SEQ_CASC位操控)—采样办法

双序列发生器形式、级联形式(AdcRegs.ADCTRL3.bit.SMODE_SEL位操控)—序列放生器的形式

也便是说在双序列发生器形式下能够选用次序采样和同步采样,在级联形式下咱们仍然能够选用次序采样和同步采样两种办法

序列发生器的接连主动序列化形式和发动/中止形式

一个序列的转化数是由MAXCONVn进行操控的,在发动一个转化序列进行转化时,AD模块将MAXCONVn的值装载进主动序列状况寄存器ADCASEQSR的序列计数器状况位SEQCNTR。

当序列发生器从状况CONV00开端并次序进行(CONV01,CONV02。。。。)时,SEQCNTR位从装入值开端递减,直到为0,完毕一个序列的转化,完结转化数为(MAXCONVn+1)。

当ADCTRL1的CONT RUN位设为0时,AD的序列发生器运转在发动/中止形式,也便是说这种形式下,序列发生器在完结1个序列的转化之后将中止作业,鄙人一次转化发动开端之前,

有必要复位序列发生器,将转化器置为CONV00。

复位的办法如下:

AdcRegs.ADCTRL2.bit.RST_SEQ1=1;//当即复位序列发生器为CONV00

AdcRegs.ADCTRL2.bit.RST_SEQ2=1;//当即复位序列发生器为CONV08

当AD的操控寄存器1的CONT RUN位设为1时,AD的序列发生器运转在接连主动序列化形式,当序列转化完毕时,转化序列主动重复开端,SOC触发时主动将MAXCONVn装入SEQCNTR,

SEQ的状况变为CONV00。在这种情况下,为了防止重写数据,有必要保证鄙人一个转化序列开端前,读取成果寄存器。