NAND FLASH在对大容量的数据存储需求中日益开展,到如今,一切的数码相机、大都MP3播放器、各种类型的U盘、许多PDA里边都有NAND FLASH的身影。

1.Flash的简介

NOR Flash:

u程序和数据可寄存在同一片芯片上,具有独立的数据总线和地址总线,能快速随机地读取,答应体系直接从Flash中读替代码履行,而无需先将代码下载至RAM中再履行

u能够单字节或单字编程,但不能单字节擦除,有必要以块为单位或对整片履行擦除操作,在对存储器进行编程之前需求对块或整片进行预编程和擦除操作。

NAND FLASH

u以页为单位进行读写操作,1页为256B或512B;以块为单位进行擦除操作,1块为4KB、8KB或16KB。具有快编程和快擦除的功用

u数据、地址选用同一总线,完结串行读取。随机读取速度慢且不能按字节随机编程

u芯片尺度小,引脚少,是位本钱(bit cost)最低的固态存储器

u芯片存储位过错率较高,引荐运用ECC校验,并包括有冗余块,其数目大约占1%,当某个存储块发生过错后能够进行标示,并以冗余块替代

uSamsung、TOSHIBA和Fujistu三家公司支撑选用NAND技能NAND Flash。现在,Samsung公司推出的最大存储容量可达8Gbit。NAND首要作为SmartMedia卡、Compact Flash卡、PCMCIA ATA卡、固态盘的存储介质,并正成为Flash磁盘技能的中心。

2.NAND FLASH和NOR FLASH的比较

1)功用比较

flash闪存对错易失存储器,能够对称为块的存储器单元块进行擦写和再编程。任何flash器材的写入操作只能在空或已擦除的单元内进行,所以大大都情况下,在进行写入操作之前有必要先履行擦除。NAND器材履行擦除操作是十分简略的,而NOR则要求在进行擦除前先要将方针块内一切的位都写为0。

由于擦除NOR器材时是以64~128KB的块进行的,履行一个写入/擦除操作的时刻为5s,与此相反,擦除NAND器材是以8~32KB的块进行的,履行相同的操作最多只需求4ms。

履行擦除时块尺度的不同进一步拉大了NOR和NADN之间的功用距离,核算标明,关于给定的一套写入操作(尤其是更新小文件时),更多的擦除操作有必要在依据NOR的单元中进行。这样,当挑选存储处理计划时,规划师有必要权衡以下的各项要素。

● NOR的读速度比NAND稍快一些。

● NAND的写入速度比NOR快许多。

● NAND的4ms擦除速度远比NOR的5s快。

●大大都写入操作需求先进行擦除操作。

● NAND的擦除单元更小,相应的擦除电路更少。

2)接口不同

NOR flash带有SRAM接口,有满足的地址引脚来寻址,能够很简单地存取其内部的每一个字节。

NAND器材运用杂乱的I/O口来串行地存取数据,共用8位总线(各个产品或厂商的办法或许各不相同)。8个引脚用来传送操控、地址和数据信息。NAND读和写操作选用512字节的页和32KB的块为单位,这一点有点像硬盘办理此类操作,很自然地,依据NAND的存储器就能够替代硬盘或其他块设备。

3)容量和本钱

NAND flash的单元尺度简直是NOR器材的一半,由于生产过程更为简略,NAND结构能够在给定的模具尺度内供给更高的容量,也就相应地降低了价格,大约只要NOR的十分之一。

NOR flash占有了容量为1~16MB闪存商场的大部分,而NAND flash仅仅用在8~128MB的产品傍边,这也阐明NOR首要应用在代码存储介质中,NAND合适于数据存储,NAND在CompactFlash、Secure Digital、PC Cards和MMC存储卡商场上所占比例最大。

4)牢靠性和耐用性

选用flahs介质时一个需求要点考虑的问题是牢靠性。关于需求扩展MTBF的体系来说,Flash对错常适宜的存储计划。能够从寿数(耐用性)、位交流和坏块处理三个方面来比较NOR和NAND的牢靠性。

在NAND闪存中每个块的最大擦写次数是一百万次,而NOR的擦写次数是十万次。NAND存储器除了具有10比1的块擦除周期优势,典型的NAND块尺度要比NOR器材小8倍,每个NAND存储器块在给定的时刻内的删去次数要少一些。

5)位交流(过错率)

一切flash器材都受位交流现象的困扰。在某些情况下(很少见,NAND发生的次数要比NOR多),一个比特位会发生回转或被陈述回转了。一位的改变或许不很显着,可是假如发生在一个要害文件上,这个小小的毛病或许导致体系停机。假如仅仅陈述有问题,多读几回就或许处理了。当然,假如这个位真的改变了,就有必要选用过错勘探/过错更正(EDC/ECC)算法。位回转的问题更多见于NAND闪存,NAND的供货商主张运用NAND闪存的时分,一起运用EDC/ECC算法。

这个问题关于用NAND存储多媒体信息时倒不是丧命的。当然,假如用本地存储设备来存储操作体系、装备文件或其他灵敏信息时,有必要运用EDC/ECC体系以保证牢靠性。

6)坏块处理

NAND器材中的坏块是随机散布的。曾经也曾有过消除坏块的尽力,但发现成品率太低,价值太高,底子不划算。NAND器材需求对介质进行初始化扫描以发现坏块,并将坏块符号为不可用。现在的FLSAH一般都供给冗余块来替代坏块如发现某个块的数据发生过错(ECC校验),则将该块标示成坏块,并以冗余块替代。这导致了在NAND Flash中,一般都需求对坏块进行编号办理,让每一个块都有自己的逻辑地址。

7)易于运用

能够十分直接地运用依据NOR的闪存,能够像其他存储器那样衔接,并能够在上面直接运转代码。由于需求I/O接口,NAND要杂乱得多。各种NAND器材的存取办法因厂家而异。在运用NAND器材时,有必要先写入驱动程序,才干持续履行其他操作。向NAND器材写入信息需求适当的技巧,由于规划师绝不能向坏块写入,这就意味着在NAND器材上从头到尾都有必要进行虚拟映射。

8)软件支撑

当评论软件支撑的时分,应该差异根本的读/写/擦操作和高一级的用于磁盘仿真和闪存办理算法的软件,包括功用优化。在NOR器材上运转代码不需求任何的软件支撑,在NAND器材进步行相同操作时,一般需求驱动程序,也便是内存技能驱动程序(MTD),NAND和NOR器材在进行写入和擦除操作时都需求MTD。运用NOR器材时所需求的MTD要相对少一些,许多厂商都供给用于NOR器材的更高档软件,这其间包括M-System的TrueFFS驱动,该驱动被Wind River System、Microsoft、QNX Software System、Symbian和Intel等厂商所选用。驱动还用于对DiskOnChip产品进行仿真和NAND闪存的办理,包括纠错、坏块处理和损耗平衡。

在掌上电脑里要运用NAND FLASH存储数据和程序,可是有必要有NOR FLASH来发动。除了SAMSUNG处理器,其他用在掌上电脑的干流处理器还不支撑直接由NAND FLASH发动程序。因而,有必要先用一片小的NOR FLASH发动机器,在把OS等软件从NAND FLASH载入SDRAM中运转才行。

9)首要供货商

NOR FLASH的首要供货商是INTEL ,MICRO等厂商,曾经是FLASH的干流产品,但现在被NANDFLASH挤的比较难过。它的长处是能够直接从FLASH中运转程序,可是工艺杂乱,价格比较贵。

NAND FLASH的首要供货商是SAMSUNG和东芝,在U盘、各种存储卡、MP3播放器里边的都是这种FLASH,由于工艺上的不同,它比NORFLASH具有更大存储容量,并且廉价。但也有缺点,便是无法寻址直接运转程序,只能存储数据。别的NAND FLASH十分简单呈现坏区,所以需求有校验的算法。

3.NAND Flash的硬件规划

NAND FLASH是选用与非门结构技能的非易失存储器,有8位和16位两种组织形式,下面以8位的NAND FLASH进行评论。

1)接口信号

与NOR Flash相比较,其数据线宽度只要8bit,没有地址总线,I/O接口可用于操控指令和地址的输入,也可用于数据的输入和输出,多了CLE和ALE来区别总线上的数据类别。

|

信号

|

类型

|

描绘

|

|

CLE

|

O

|

指令锁存使能

|

|

ALE

|

O

|

地址锁存使能

|

|

nFCE

|

O

|

NAND Flash片选

|

|

NFRE

|

O

|

NAND Flash读使能

|

|

nFWE

|

O

|

NAND Flash写使能

|

|

NCON

|

I

|

NAND Flash装备

|

|

R/nB

|

I

|

NAND Flash Ready/Busy

|

2)地址结构

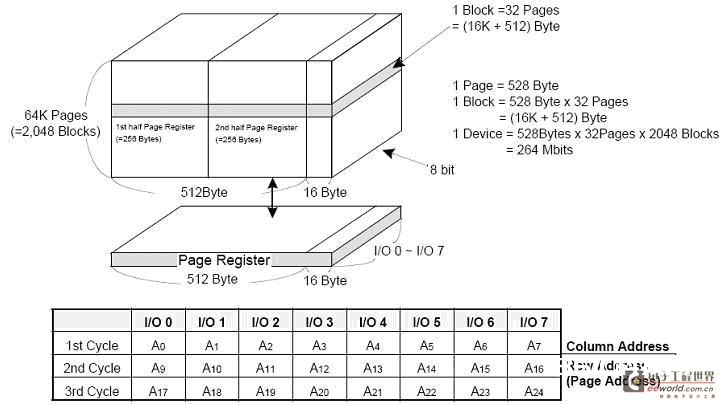

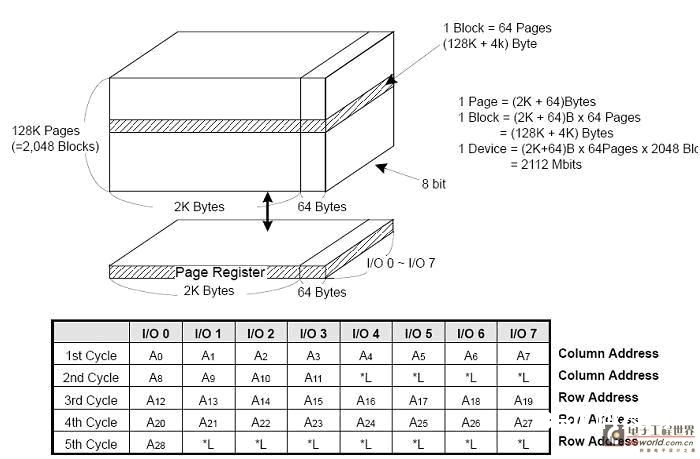

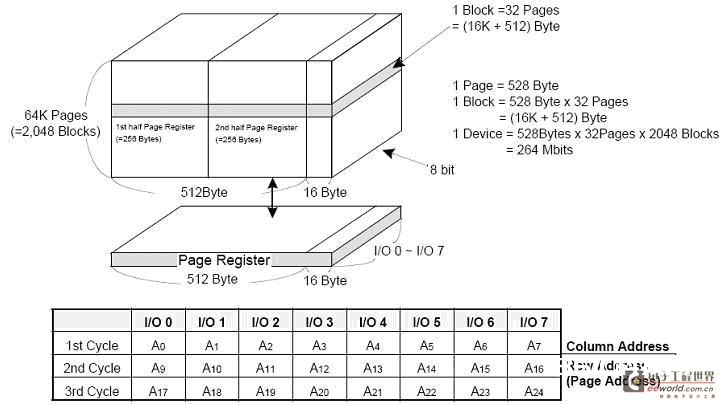

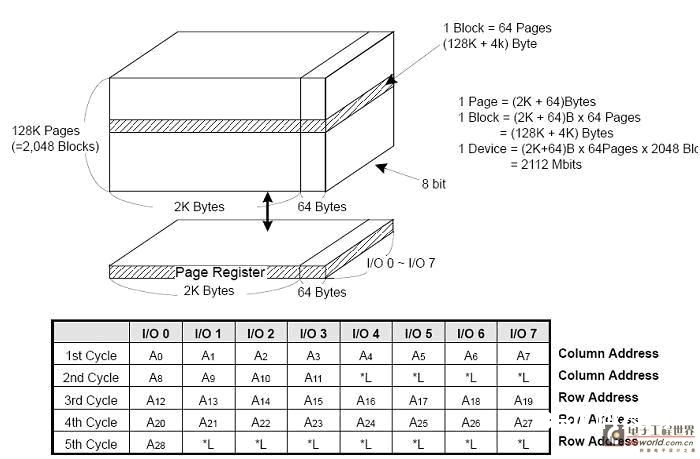

NAND FLASH首要以页(page)为单位进行读写,以块(block)为单位进行擦除。FLASH页的巨细和块的巨细因不同类型块结构而不同,块结构有两种:小块(图7)和大块(图8),小块NAND FLASH包括32个页,每页512+16字节;大块NAND FLASH包括64页,每页2048+64字节。

图7小块类型NAND FLASH

图8大块类型NAND FLASH

其间,512B(或1024B)用于寄存数据,16B(64B)用于寄存其他信息(包括:块好坏的符号、块的逻辑地址、页内数据的ECC校验和等)。NAND设备的随机读取得功率很低,一般以页为单位进行读操作。体系在每次读一页后会核算其校验和,并和存储在页内的冗余的16B内的校验和做比较,以此来判别读出的数据是否正确。

大块和小块NAND FLASH都有与页巨细相同的页寄存器,用于数据缓存。当读数据时,先从NAND FLASH内存单元把数据读到页寄存器,外部经过拜访NAND FLASH I/O端口取得页寄存器中数据(地址主动累加);当写数据时,外部经过NAND FLASH I/O端口输入的数据首要缓存在页寄存器,写指令宣布后才写入到内存单元中。

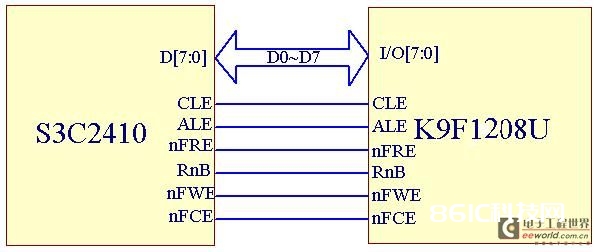

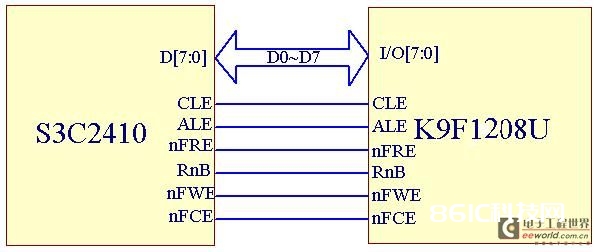

3)接口电路规划(以下以2410和K9F1208U为例)

2410处理器具有专门针对NAND设备的接口,能够很方便地和NAND设备对接,如图9所示。尽管NAND设备的接口比较简略,简单接到体系总线上,但2410处理器针对NAND设备还集成了硬件ECC校验,这将大大提高NAND设备的读写功率。当没有处理器的ECC支撑时,就需求由软件来完结ECC校验,这将耗费很多的CPU资源,使读写速度下降。

图9S3C2410与NAND FLASH接口电路示意图

3.NAND FLASH的软件编写和调试

NAND设备的软件调试一般分为以下几个过程:设置相关寄存器、NAND设备的初始化、NAND设备的辨认、NAND设备的读擦写(带ECC校验)

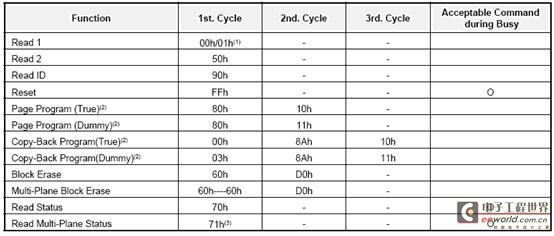

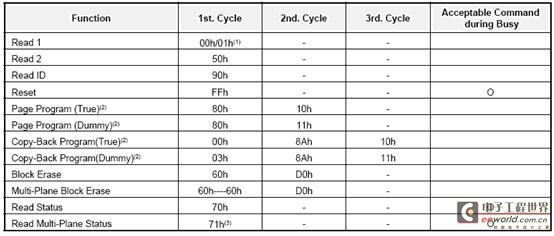

NAND设备的操作都是需求经过指令来完结,不同厂家的指令稍有不同,以下一Samsung公司的K9F1208U0M指令表为例介绍NAND设备的软件编写。

表2K9F1208U0MCommand Sets

1)依据2410寄存器界说如下的指令宏

#define NF_CMD(cmd){rNFCMD=cmd;}

#define NF_ADDR(addr){rNFADDR=addr;}

#define NF_nFCE_L(){rNFCONF&=~(1<<11);}

#define NF_nFCE_H(){rNFCONF|=(1<<11);}

#define NF_RSTECC(){rNFCONF|=(1<<12);}

#define NF_RDDATA()(rNFDATA)

#define NF_WRDATA(data) {rNFDATA=data;}

#define NF_WAITRB(){while(!(rNFSTAT&(1<<0)));}

//wait tWB and check F_RNB pin.

2)NAND设备的初始化

static void NF_Init(void)//Flash初始化

{

rNFCONF=(1<<15)|(1<<14)|(1<<13)|(1<<12)|(1<<11)|(TACLS<<8)|(TWRPH0<<4)|(TWRPH1<<0);//设置NAND设备的相关寄存器

NF_Reset();

}

static void NF_Reset(void)//Flash重置

{

int i;

NF_nFCE_L();

NF_CMD(0xFF);//reset command

for(i=0;i<10;i++);//tWB = 100ns

NF_WAITRB();//wait 200~500us;

NF_nFCE_H();

}

3)NAND设备的辨认//#define ID_K9F1208U0M0xec76

static U16 NF_CheckId(void)//Id区分

{

int i;

U16 id;

NF_nFCE_L();

NF_CMD(0x90);

NF_ADDR(0x0);

for(i=0;i<10;i++);//wait tWB(100ns)

id=NF_RDDATA()<<8;// Maker code(K9F1208U:0xec)

id|=NF_RDDATA();// Devide code(K9F1208U:0x76)

NF_nFCE_H();

return id;

}

4)NAND的擦操作

static int NF_EraseBlock(U32 block)

{

U32 blockPage=(block<<5);

int i;

NF_nFCE_L();

NF_CMD(0x60[q1]);// Erase one block 1st command

NF_ADDR(blockPage&0xff);// Page number=”0″

NF_ADDR((blockPage>>8)&0xff);

NF_ADDR((blockPage>>16)&0xff);

NF_CMD(0xd0[q2]);// Erase one blcok 2nd command

for(i=0;i<10;i++);//wait tWB(100ns)//??????

NF_WAITRB();// Wait tBERS max 3ms.

NF_CMD(0x70);//Read status command

if (NF_RDDATA()&0x1)// Erase error

{

NF_nFCE_H();

Uart_Printf(“[ERASE_ERROR:block#=%d]\n”,block);

return 0;

}

else

{

NF_nFCE_H();

return 1;

}

}

5)NAND的读操作

static int NF_ReadPage(U32 block,U32 page,U8 *buffer)//读Flash

{

int i;

unsigned int blockPage;

U8 ecc0,ecc1,ecc2;

U8 *bufPt=buffer;

U8 se[16];

page=page&0x1f;//32页

blockPage=(block<<5)+page;//1Bolck包括32页

NF_RSTECC();// Initialize ECC

NF_nFCE_L();

NF_CMD(0x00);// Read command

NF_ADDR(0);// Column = 0

NF_ADDR(blockPage&0xff);//

NF_ADDR((blockPage>>8)&0xff);// Block & Page num.

NF_ADDR((blockPage>>16)&0xff);//

for(i=0;i<10;i++);//wait tWB(100ns)

NF_WAITRB();// Wait tR(max 12us)

for(i=0;i<512;i++)

{

*bufPt++=NF_RDDATA();// Read one page

}

ecc0=rNFECC0;//运用2410自带的硬件ECC校验

ecc1=rNFECC1;

ecc2=rNFECC2;

for(i=0;i<16;i++)

{

se[i]=NF_RDDATA();// Read spare array

//读页内冗余的16B

}

NF_nFCE_H();

if(ecc0==se[0] && ecc1==se[1] && ecc2==se[2])//不知道运用哪一种软件规范?

{//比较数据成果是否正确

Uart_Printf(“[ECC OK:%x,%x,%x]\n”,se[0],se[1],se[2]);

return 1;

}

else

{

Uart_Printf(“[ECC ERROR(RD):read:%x,%x,%x, reg:%x,%x,%x]\n”,

se[0],se[1],se[2],ecc0,ecc1,ecc2);

return 0;

}

}

6)NAND的写操作

static int NF_WritePage(U32 block,U32 page,U8 *buffer)//写Flash

{

int i;

U32 blockPage=(block<<5)+page;

U8 *bufPt=buffer;

NF_RSTECC();// Initialize ECC

NF_nFCE_L();

NF_CMD(0x0[q4]);//Read Mode 1

NF_CMD(0x80);// Write 1st command,数据输入

NF_ADDR(0);// Column 0

NF_ADDR(blockPage&0xff);

NF_ADDR((blockPage>>8)&0xff);// Block & page num.

NF_ADDR((blockPage>>16)&0xff);

for(i=0;i<512;i++)

{

NF_WRDATA(*bufPt++);// Write one page to NFM from buffer

}

seBuf[0]=rNFECC0;

seBuf[1]=rNFECC1;

seBuf[2]=rNFECC2;

seBuf[5]=0xff;// Marking good block

for(i=0;i<16;i++)

{

NF_WRDATA(seBuf[i]);// Write spare array(ECC and Mark)

}

NF_CMD(0x10);// Write 2nd command

for(i=0;i<10;i++);//tWB = 100ns.

NF_WAITRB();//wait tPROG 200~500us;

NF_CMD(0x70);// Read status command

for(i=0;i<3;i++);//twhr=60ns

if (NF_RDDATA()&0x1)// Page write error

{

NF_nFCE_H();

Uart_Printf(“[PROGRAM_ERROR:block#=%d]\n”,block);

return 0;

}

else

{

NF_nFCE_H();

#if (WRITEVERIFY==1)

//return NF_VerifyPage(block,page,pPage);

#else

return 1;

#endif

}

}

以下评论一下NAND设备上所支撑的文件体系,大约现在有以下几种:

A.JFFS2(没有坏块处理,支撑大容量存储的时分需求耗费很多的内存,很多的随机拜访降低了NAND设备的读取功率)和YAFFS(速度快,但不支撑文件的紧缩和解压)

B.支撑DiskOnChip设备的TRUEFFS(True Flash File System). TRUEFFS是M-Systems公司为其产品DiskOnChip开发的文件体系,其规范并不敞开。

C.由SSFDC(Solid State Floppy Disk Card)论坛界说的支撑SM卡的DOS-FAT。SM卡的DOS-FAT文件体系是由SSFDC论坛界说的,但它有必要用在规范的块设备上。

关于很多用在各类存储卡上的NAND设备而言,他们简直都选用FAT文件体系,而在嵌入式操作体系下,还没有驱动程序能够直接让NAND设备选用文件体系,就技能视点来说,FAT文件体系不是很合适NAND设备,由于FAT文件体系的文件分区表需求不断地擦写,而NAND设备的只能有限次的擦写。

在上面现已很显着的说到,NAND设备存在坏块,为和上层文件体系接口,NAND设备的驱动程序有必要给文件体系供给一个牢靠的存储空间,这就需求ECC(Error Corection Code)校验,坏块标示、地址映射等一系列的技能手段来到达牢靠存储意图。

SSFDC软件规范中,具体界说了怎么运用NAND设备每个页中的冗余信息来完结上述功用。这个软件规范中,很重要的一个概念便是块的逻辑地址,它将在物理上或许不接连、不牢靠的空间分配编号,为他们在逻辑空间上给体系文件供给一个接连牢靠的存储空间。

表3给出了SSFDC规范中逻辑地址的标示办法。在体系初始化的时分,驱动程序先将一切的块扫描一遍,读出他们所对应的逻辑地址,并把逻辑地址和虚拟地址的映射表建好。体系运转时,驱动程序经过查询映射表,找到需求拜访的逻辑地址所对应的物理地址然后进行数据读写。

表3冗余字节界说

|

字节序号

|

内容

|

字节序号

|

内容

|

|

512

|

用户界说数据

|

520

|

后256BECC校验和

|

|

513

|

521

|

|

514

|

522

|

|

515

|

523

|

块逻辑地址

|

|

516

|

数据状况

|

524

|

|

517

|

块状况

|

525

|

前256BECC校验和

|

|

518

|

块逻辑地址1

|

526

|

|

519

|

527

|

表4给出了块逻辑地址的寄存格局,LA表明逻辑地址,P代表偶校验位。逻辑地址只要10bit,代表只要1024bit的寻址空间。而SSFDC规范将NAND设备分成了多个zone,每个zone内有1024块,但这物理上的1024块映射到逻辑空间只要1000块,其他的24块就作为备份运用,当有坏块存在时,就能够以备份块将其替换。

表4逻辑地址格局

|

D7

|

D6

|

D5

|

D4

|

D3

|

D2

|

D1

|

D0

|

|

|

0

|

0

|

0

|

1

|

0

|

LA9

|

LA8

|

LA7

|

第518523字节

|

|

LA6

|

LA5

|

LA4

|

LA3

|

LA2

|

LA1

|

LA0

|

P

|

第519524字节

|

有了以上的软件规范,就能够对NAND设备写出较规范的ECC校验,并能够编写检测坏块、符号坏块、树立物理地址和逻辑地址的映射表的程序了。

static int NF_IsBadBlock(U32 block)//检测坏块

{

}

static int NF_MarkBadBlock(U32 block)//符号坏块

{

}

int search_logic_block(void)//树立物理地址到逻,辑地址的映射表

{

}

这段代码的首要效果便是发生数组lg2ph[],这个数组的意义便是“块物理地址=lg2ph[逻辑地址]”。