摘要:PCB的有用抗搅扰规划,是电子产品规划的要害环节,影响着电路作业的牢靠性及稳定性。文章剖析了电路板存在电磁搅扰的首要原因,从电路板的选取、电路板元器材的布局、电源与地的布线和信号线的布线等方面总结出在PCB规划时有用按捺和防止电磁搅扰的办法与准则。

0 导言

印刷电路板(俗称PCB)是电子产品中电路元件的载体,供给各电路元件之间的电气衔接,是各种电子设备最根本的组成部分,它的功用直接关系到电子设备质量的好坏。跟着信息化社会的开展和电子技能的开展,电路的集成度越来越高,电路板的尺度越来越小,电路板上的元件密度越来越高,电子产品的运转速度越来越快,因而由其本身产生的电磁搅扰问题和兼容性问题显得愈加杰出,所以,怎么减小PCB板的电磁搅扰成为当今电子技能的热门话题。一个电路板的电磁兼容问题是一个电子体系能否正常作业的要害,影响着电路或体系作业的牢靠性及稳定性,为此在进行PCB规划时要有用处理电磁搅扰问题。

文章将从剖析现代智能高速电子体系中电路板存在电磁搅扰的原因,总结出在PCB规划时应考虑的减小电磁搅扰的办法与准则。

1 电路板存在电磁搅扰的原因

在由开关电源和微处理器构成的高速电子体系中,电路板的电磁搅扰首要来自于本身存在的射频搅扰源、元器材、根本回路和差模与共模噪声。

1.1 电路板上存在的射频搅扰源

在智能的高速电子体系中,电路板上的射频搅扰源首要来自微处理器体系、电源供电体系和振动器电路。

1.微处理器体系

微处理器的射频(RF)噪声产生于芯片内部并经过许多不同的或许办法耦合到外部,在一切输入、输出、电源和地一起存在,是潜在的噪声,使到微处理器的每个引脚都或许有问题。而最大的问题是来自微处理器输入和输出引脚(I/O)的噪声。这些噪声首要产生于芯片内部的时钟切换,经过输入和输出引脚衔接到内部和外部的电缆并辐射出去,首要表现为短时脉冲波形搅扰。

2.电源供电体系

电源供电体系包含电源稳压器及其稳压器和微操控器端的旁路电容。这些电路是体系中一切射频能量的源头,为芯片内的时序电路供给需求的切换电流。

3.振动器电路

振动器电路为体系供给快速的时钟信号,在数字体系中,因为振动器的输出缓冲是数字的,因而在将正弦波转化为方波时会在输出侧产生谐波。内部运转产生的任何噪声,比方时钟缓冲,都会在输出端显示出来,并经过元件耦合传达。

1.2 其他的电磁搅扰原因

1.贴片器材和通孔元器材

贴片器材(SMD)因为感抗较小和元器材放置较近、在处理射频能量时比引线芯片更好。一般,通孔元器材的引线电容在约80MHz时都会产生自振动(由容性变为理性)。因而高于80MHz的噪声要遭到操控,假如规划中选用通孔元器材就要考虑许多严峻的问题。

2.根本回路

从微处理器传送到另一芯片的每个边际跳变都是一个电流脉冲,电流脉冲流向接纳芯片,流出接纳芯片的接地引脚,然后经过地线回来到微处理器的接地引脚,就构成了一个根本回路。这样的回路在电路中处处存在,任何噪声电压和它的隶属电流经过最低阻抗途径回到它产生的当地,然后构成影响。一个回路可所以信号线和它的回来途径,电源和地之间的旁路,晶振和微处理器内的驱动器,或许是从电源供给的电压稳压器到旁路电容的回路。回路的几许面积越大,辐射就越强,因而,咱们能够经过操控回来途径的形状和阻抗来减轻噪声的传达。

3.差模与共模噪声

差模噪声是信号经过线路传输到接纳芯片,然后沿回来线路回来时产生的噪声。两条线路间存在着差分电压,这是每个信号要完结功用必定要产生的噪声。这种噪声产生的电场强度正比于频率的平方、电流的巨细和电流环路的面积,反比于观测点到噪声源的间隔。因而,减小差模辐射的办法为:下降电路的作业频率、减小信号环路的面积或减小信号电流的强度。在实际作业中最有用的办法是操控信号环路的面积。

共模噪声是电压一起沿信号线和回来线传输,两者之间没有差分电压,由信号线和回来线共有的阻抗引起的噪声。共模阻抗噪声是大多数依据微处理器的体系最常见的噪声源。这种噪声产生的电场强度正比于频率的巨细、电流的巨细和电缆的长度,反比于观测点到噪声源的间隔。减小共模辐射的办法有:下降地线阻抗,缩短线路的长度,运用共模扼流圈。

2 PCB的规划准则

因为电路板集成度和信号频率跟着电子技能的开展越来越高,不行防止的要带来电磁搅扰,所以在规划PCB时应遵从以下准则,使电路板的电磁搅扰操控在必定的范围内,到达规划要求和规范,进步电路的全体功用。

2.1 电路板的选取

PCB规划的首要任务是要适当地选取电路板的巨细,尺度过大会因元器材之间的连线过长,导致线路的阻抗值增大,抗搅扰才干下降;而尺度过小会导致元器材安置密布,不利于散热,并且连线过细过密,简单引起串扰。所以应依据体系所需元件状况,挑选适宜尺度的电路板。

电路板分为有单面板、双面板和多层板。电路板层数的选取取决于电路要完成的功用、噪声目标、信号和网线数量等。合理的层数设置能够减小电路本身的电磁兼容问题。一般的选取准则是:①关于信号频率为中低频,元器材较少,布线密度归于较低或中等时,选用单面板或双面板;②关于布线密度高、集成度高且元器材较多时选用多层板;③关于信号频率高、高速集成电路、元器材密布的选4层或层数更多的电路板。多层板在规划时可单独某一层作为电源层、信号层和接地层。信号回路面积减小,下降差模辐射,为此多层板能够减小电路板的辐射和进步抗搅扰才干。

2.2 电路板元器材的布局

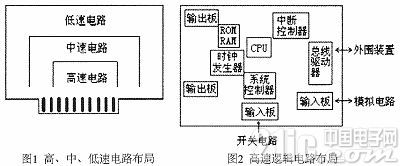

在确认PCB尺度后,应先确认特别元件的方位,最终依据电路的功用单元,分块的对电路的悉数元件进行布局。数字电路单元、仿照电路单元和电源电路单元应分隔,高频电路单元和低频电路单元也应分隔。一般,在安置高速、中速和低速电路时,应参阅图1的办法摆放元器材;在安置带有时钟、CPU、存储器、操控器和输入输出电路时,应参阅图2的办法摆放元器材。常用电路板的布局准则如下。

1.确认特别元件方位的准则:①发热元件应放置在利于散热的方位,例如PCB的边际,并远离微处理器芯片;②特别的高频元件应紧挨着放置,以缩短他们之间的连线;③灵敏元件应远离时钟产生器、振动器等噪声源;④电位器、可调电感器、可变电容器、按键开关等可调元件的布局应契合整机的结构需求,便利调理;⑤质量较重的元件应选用支架固定;⑥EMI滤波器应接近EMI源放置。

2.依据电路功用单元对电路的伞部元器材进行布局的准则:①各功用电路应按照之间的信号流向确认相应的方位,便利布线;②每个功用电路应先确认中心元件的方位,并环绕中心元件放置其他元件,尽量缩短元件之间的连线;③对高频电路,应考虑元件之间的散布参数;④放置于电路板边上的元件,应离电路板边际不小于2mm。⑤DC/DC变换器、开关管和整流器应尽量接近变压器放置,以减小对外的辐射;⑥调压元件和滤波电容器应接近整流二极管放置。

2.3 电源与地的布线准则

PCB的电源与地的布线是否合理是整个电路板减小电磁搅扰的要害所在。电源线和地线的规划是PCB中不行忽视的问题,往往也是难度最大的一项规划,规划时应遵从以下准则。

1.电源与地的布线技巧

PCB上的布线是有阻抗、容抗和感抗等散布参数的特性。为了减小PCB布线的散布参数对高速电子体系的影响,对电源与地的布线准则为:①增大走线的间隔以削减电容耦合的串扰;②电源线和地线应平行走线,以使散布电容到达最佳;③依据承载电流的巨细,尽量加粗电源线和地线的宽度,减小环路电阻,一起使电源线和地线在各功用电路中的走向和信号的传输方向共同,这样有助于进步抗搅扰才干;④电源和地应直接走线在各自的上方,然后减小感抗和使回路面积最小,尽量使地线走在电源线下面;⑤地线越粗越好,一般地线的宽度不小于3mm;⑥将地线构成闭环路以缩小地线上的电位差值,进步抗搅扰才干;⑦在多层板布线规划时,可将其间一层作为“全地平面”,这样能够削减接地阻抗,一起又起到屏蔽效果。

2.各功用电路的接地技巧

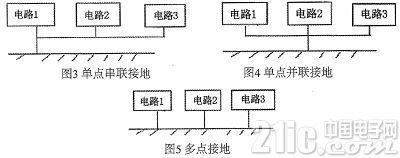

PCB各功用电路的接当地法分为单点接地和多点接地。单点接地依据衔接办法分为单点串联接地和单点并联接地两种办法,如图3和图4所示。单点串联接地因为各接地导线长度不同,各电路接地阻抗不同,电磁兼容功用下降,常用于维护接地。单点并联接地各电路有单独的接地线,因而相互之间的搅扰小,但或许延伸接地线,增大接地阻抗,常用于信号接地、仿照接地、电源接地。多点接地是指各电路都有一个接地址,如图5所示。多点接地常用于高频电路,具有接地线短,接地阻抗值较小,削减高频信号的搅扰。

为了削减接地带来的搅扰,接地也要满意必定的要求:①接地线尽或许要短,接地上要大;②防止产生不必要的接地回路,减小公共接地的搅扰电压;③接地准则是关于不同信号采纳不同接当地法,不能把一切接地采纳同一接地址;④在规划多层PCB时,要把电源层和接地层尽或许放置在相邻的层中,以便电路中构成层问的电容,减小电磁搅扰;⑤尽量防止强电和弱电信号,数字和仿照信号共地。

3.放置格栅化平面

对两层板来说,格栅化是最重要的规划技能。格栅化是在PCB上延伸地线并运用地填充形式来构建衔接到地的格栅网络,构成一个有用的地平面,和四层板相同能够减小噪声。它有两个意图:①仿照四层板的地层,为每一条信号线供给处于下方的回来途径;②下降微处理器和电压稳压之间的阻抗。规划时应留意的准则是:①每条地线延伸尽或许填充印刷电路板的空间;②在两层板上尽或许多的放置格栅;③尺度上适宜时运用尽或许多的通孔将顶层和底层的格栅衔接起来;④线路不必定要直角或相同的宽度。

4.高频去耦电容和铁氧体磁珠的运用

数字电路中,当逻辑门的状况产生改动时,会在电源上产生一个很大的尖峰脉冲,构成瞬间的噪声电压,这种状况遍及选用去耦电容或铁氧体磁珠来约束电流的忽然改动,减小辐射。一般在每个芯片的电源和地之间加上容量约为0.01μF~0.1μF的高频去耦电容,在接近芯片的电源线上放置铁氧体磁珠,以阻断来自电源线的射频电流源。规划时应尽量做到:①选用钽电容,而不要运用铝电解电容,后者具有较大的内部电感;②电容间隔芯片越近越好,去耦%&&&&&%的引线不宜太长;③铁氧体磁珠只用在+V的电源线上,不必在地线上;④铁氧体磁珠尽量接近噪声源放置。

2.4 信号线的布线准则

1.减小线路的容性和理性串扰

布线时,即便在很短的间隔内并行走线的线路之间也存在容性和理性串扰。容性耦合时,源端的上升沿会在受害者上引起一个上升沿。理性耦合时,受害者上的电压改动与源端的改动正好相反。大部分串扰都是容性的,噪声的巨细正比于并行的间隔、频率、源端电压的振幅和受害者的阻抗,反比于两条线路脱离的间隔。因而减小串扰的办法有:①使衔接到微处理器的带着射频噪声的线路远离其他信号;②应将或许成为噪声受害者的信号的回来地线走线在其下方;③不要在电路板的外部边际走噪声线路;④假如或许,将一些噪声线路走线在一起然后用地线围住;⑤使非噪声线路远离电路板上简单接纳噪声的区域,比方接插件、振动器电路、继电器和继电器驱动器。

2.合理安排回来地线数目

在计算机工业中,电缆或导线中每9条信号线至少要有1根地线,这是很遍及的经历。高速时,这个份额变到5:1。能够在规划信号线和回来线路时考虑的准则:①最好是电缆中的每条信号线都有一条回来地线,组成双绞线对;②不要超越每9条信号线有一条回来地线;③假如电缆超越一英尺长,应该每4条信号线有一条回来地线;④假如或许,应该运用一个实心金属支架作为机械支架,焊接在两块电路板之间,既作为装置支架,也作为牢靠的射频回来地线。

3.其他的布线准则

①用作导线的铜箔在90度转弯处会使导线的阻抗不接连,有或许产生反射搅扰,所以应将90度的导线改成135度的走线,这样有助于削减产生反射搅扰;②双面布线的PCB,上下两层的布线应笔直穿插,以削减耦合,有利于按捺搅扰;③选用阻隔走线,在许多不得不平行走线的电路布线时可考虑在两条信号线中加一条接地的阻隔走线;④一切线路尽量沿直流地铺设,尽量防止沿沟通地铺设;⑤选用短接线,在线路无法摆放或只要绕大圈才干走通的状况下,爽性用绝缘“飞线”衔接,不必印刷线,或许用阻容元件引线直接跨接;⑥直流电路应远离沟通电路布线,输入信号线与输出信号线应分隔;⑦信号走线不要有分支,应连接地从一个元件到下一个元件,以防止反射搅扰或谐波搅扰;⑧时钟等高频信号线应接近地线进行布线,使环路面积最小,以减小差模辐射。

3 结束语

想完全消除电子产品中的电磁搅扰是不或许的,咱们只能采纳必要办法减小电磁搅扰,使电磁搅扰操控在必定范围内,而一个杰出的印刷电路板的规划,是减小电磁搅扰的重要环节。在印刷电路板规划时,可参阅以上所说到的规划准则,但这些准则并不是原封不动,应该依据详细电路状况,灵敏使用各种抗搅扰的办法,才干最大程度地满意电磁兼容的要求,这需求规划者平常的经历堆集和总结。