摘要 IP核的广泛使用进步了电路集成的功率。因为很多功用各异的IP核集成在电路中,完善的测验机制是保证其正常作业的条件。因而,怎么对IP核进行测验成为复用IP核技能有必要处理的问题。IEEE Std 1500供给了IP核的测验完结机制,文中依据IEEE 1500研讨怎么完结IP核的Wrapper规划,试验以Hamming码译码IP核ALTECC_DECODER为测验目标,验证了IEEE 1500 Wrapper可有用地对IP核进行测验。

跟着集成电路规划的增大,为进步规划功率,IP核在电路集成规划中得到了广泛使用。虽然IP核复用能简化规划流程,防止许多底层电路的规划,但IP核集成在电路中后,已无法直接通过输入、输出端口对其进行测验,且不同类型的IP核给测验办法规划带来了困难。因而,怎么树立测验机制成为IP核复用技能有必要处理的问题。

IEEE Std 1500供给了标准化、可扩展的可测性规划办法。在将IP核集成到电路中时,为其规划依据IEEE 1500标准的Wrapper,可为集成后的IP核供给标准的测验接口,一起,IEEE 1500 Wrapper完结了IP核与互连电路的阻隔,这使得IP核的测验愈加便利、安全、高效。

Hamming码在通讯范畴使用广泛,原始数据码字在编码时被刺进若干校验码,组合后的码字被发送给接纳方,接纳方通过译码即可到达过错检测的意图。在集成电路中使用Hamming码通讯可进步可靠性,Altera公司供给了相应的编码和译码IP核:ALTECC_ENCODER、ALTECC_DECODER。本文即以译码IP核ALTECC_DECODER为试验测验目标,研讨怎么针对IP核规划IEEE 1500 Wrapper,以及怎么运用Wrapper对IP核进行测验。

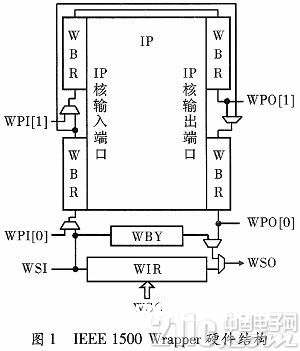

1 IEEE 1500 Wrapper硬件结构

IEEE Std 1500规矩的Wrapper硬件结构如图1所示,其间有必要包含的组成结构有:Wrapper鸿沟寄存器(Wrapper Boundary Register,WBR)、Wrapper指令寄存器(Wrapper Instruction Register,WIR)、Wrapper旁路寄存器(Wrapper Bypass Register,WBY)、Wrapper串行接口(Wrapper Serial Port,WSP);可选规划的结构有Wrapper并行测验接口(Wrapper Parallel Port,WPP)。

1.1 Wrapper接口功用界说

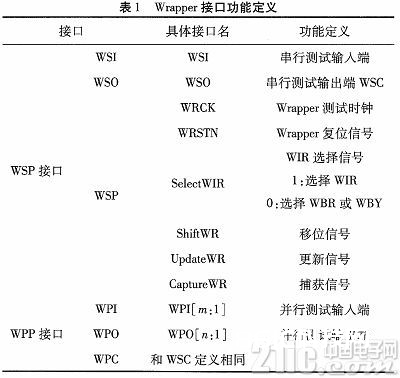

Wrapper接口主要有WSP接口和WPP接口两类。其间,WSP接口包含Wrapper串行输入端口WSI、Wrapper串行输出端口WSO、Wrapper串行操控端口WSC;WPP接口包含Wrapper并行输入端口WPI[m:1]、Wrapper并行输出端口WPO[n:1]、Wrapper并行操控端口WPC,有关Wrapper接口的功用界说如表1所示。

因为WPC端口对并行测验操作的操控和WSC端口附近,在需求为Wrapper规划并行测验接口WPP时,可省掉WPC端口的规划,相关并行测验操作由WSC接口操控。

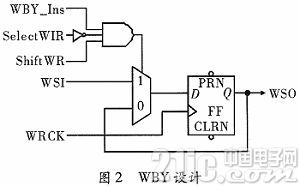

1.2 WBY规划

在测验过程中,为到达节约测验时刻的意图,关于无需测验的IP核,可使旁路寄存器WBY在Wrapper中处于有用状况。如图2所示,旁路寄存器WBY串接于WSI—WSO之间,其可为Wrapper供给一条最短的移位途径,完结对WBR链的旁路。因而,WBY一般按1 bit移位长度规划,但在必要时可增加移位长度。

图2中,WBY_Ins是指挑选WBY衔接于WSI—WSO之间的Wrapper指令,D触发器FF作业WRCK上升沿,此外,数据的移位还需满意SelectWIR=0,ShiftWR=1的条件。

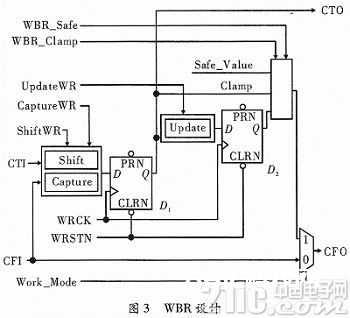

1.3 WBR规划

WBR是Wrapper履行测验操作的最主要履行部分,由一个个围绕在IP核输入、输出端口的WBR单元组成。WBR单元在呼应各项测验操作时,扮演了测验施加和呼应捕获的人物。

文献给出了典型的WBR单元规划,但因为规划简略,在实践测验使用中存在着安全性、测验操作不方便等问题。鉴于WBR单元的规划决议着测验履行的功率,许多文献均对其进行了规划研讨。

规划的WBR单元结构如图3所示。Work_Mode信号决议WBR处于正常作业形式仍是测验形式,其由WRSTN信号和Wrapper指令操控。存储单元D1衔接于CTI—CTO之间,担任呼应移位和捕获测验操作,D1存储的值即WBR单元的当时值。在移位测验操作时,上一WBR单元的数据经CTI端移入存储单元D1,D1中原先的数据移入下一WBR单元;在捕获测验操作时,CFI端的数据被捕获存储到D1中。存储单元D2担任更新测验操作,其将D1存储的WBR当时数据更新输出。本文规划的WBR单元在测验过程中支撑Safe形式和Clamp形式,在Safe形式有用时,WBR单元的CFO输出预先设定的安全值;在Clamp形式有用时,CFO输出WBR单元的当时内部数据。

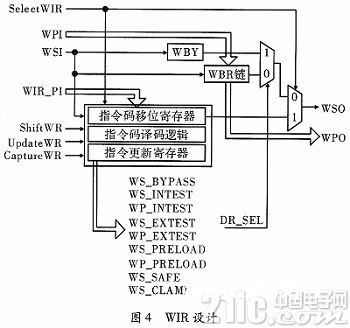

1.4 WIR规划

指令寄存器WIR用于装备Wripper的测验状况,如图4所示。WIR包含指令码移位寄存器、指令码译码逻辑和指令更新寄存器,其间指令码移位寄存器是WSI—WSO之间的一条移位通道。在测验操作开端前,首先令SelectWIR=1,设置ShiftWR=1,经WSI向指令移位寄存器中移入测验指令码,或置CaptureWR=1,经WIR_PI并行捕获测验指令码。指令码译码逻辑选用组合逻辑规划,对当时移位寄存器中的数据进行译码。在指令码移位完结后,令UpdateWR=1履行指令更新操作,指令更新寄存器依据译码成果触发新的Wrapper指令有用。

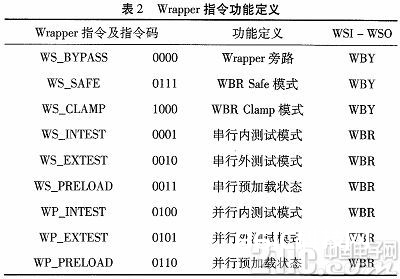

规划Wrapper指令的功用界说如表2所示,其间“串行”是指Wrapper中所有WBR单元构成一整条WBR链并作为WSI和WSO之间的一条移位通道,“并行”是指WBR单元被装备为分段链,别离衔接于WPI和WPO之间;“内测验”是指Wrapper测验目标是内部IP核,“外测验”是指Wrapper测验目标是外部互连电路。

2 IP核的Wrapper规划

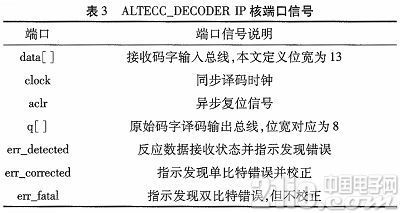

本文测验目标是依据Hamming码规矩的信号纠错译码IP核:ALTECC_DECODER,其作用是完结Hamming码的译码,并生成随同式矢量以检测接纳码字中是否存在过错。ALTECC_ DECODER IP核的端口信号阐明,如表3所示。

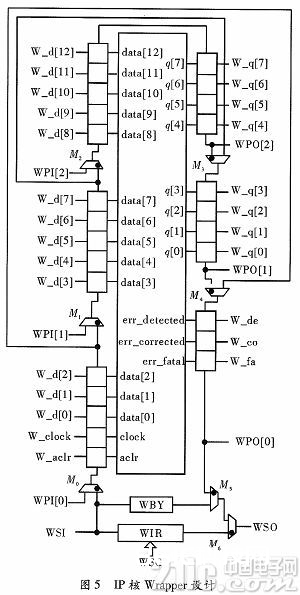

本文为ALTECC_DECODER IP核规划的IEEE1 500 Wrapper,如图5所示,IP核输入、输出端的小方框即为WBR单元。

3 试验

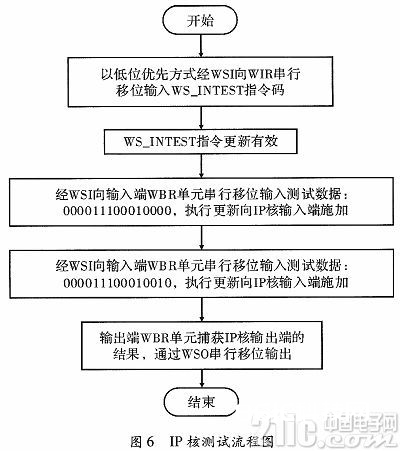

本文对ALTECC_DECODER IP核的试验测验以接纳码字0000111000100为测验数据,验证Wrapper对IP核的测验操控能否正常进行,并依据Wrapper的测验成果判别ALTCC_DECOD ER IP核的译码是否正确。在WS_INTEST指令下的Modelsim仿真测验流程图如图6所示。

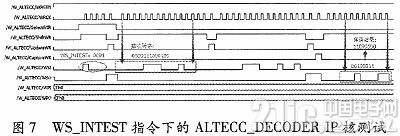

图6测验过程中,测验数据由din[12]→din[11]→* * *→din[0]→clock→aclr的次序构成,向输入端WBR单元先后串行移位输入的测验数据:000011100010000、0000111000 10010,其差异在于移入clock端WBR单元中的数据别离为0和1。测验数据串行移位输入后通过更新操作,IP核clock端的WBR单元向clock端施加了0到1的鼓励改变,IP核输出试验成果,即译码得到的原始码字,输出端WBR单元捕获IP核输出的成果后串行移位输出,串行输出的数据次序为:err_fatal→err_cotrected→err_detected→q[0]→q[1]→* * *q[7],试验测验成果,如图7所示,图中最终部分即为试验完结后串行移位输出成果。

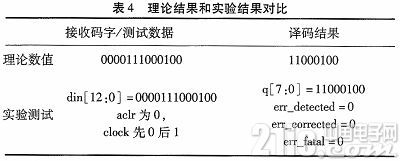

试验成果和依据Hamming码编码规矩得到的理论成果比照如表4所示。试验得到的成果为11000100,和0000111000100的理论译码成果相同,且符号信号err_detected、err_co rrected、err_fatal的输出均为0,阐明本次试验中ALTECC_DECODER IP核对接纳码字0000111000100的检测成果无误。

归纳试验剖析,为ALTECC_DECODER IP核规划的IEEE 1500 Wrapper能正常完结测验操作,并将测验成果移位输出以供数据剖析。

4 结束语

IEEE 1500 Wrapper为%&&&&&%IP核供给了标准有用的测验机制,本文在以Hamming码译码IP核ALTECC_DECODER为测验目标,研讨怎么完结IP核的Wrapper规划。文中针对现在文献中WBR存在的缺乏,规划了功用愈加完善的WBR单元,可以更好地满意测验需求。