摘要:运用低功耗COrtex—M3微操控器STM32F103VBT6和FPGA芯片规划一种依据CAN总线的运动操控器。介绍体系的体系结构、首要硬件规划和软件结构。运用FPGA高速处理才干完结操控算法,与外界通讯选用STM32和CAN总线技能,体系安稳牢靠,别的,将规划好的FPGA程序或是C程序进行封装,体系的可移植性强。

要害词:STM32;FPGA;CAN总线;运动操控

现在,运动操控正朝着高速度、高精度、开放式的方向开展,然后对履行部件提出了更高的要求。曩昔的运动操控器首要是依据单片机或许PLC加上分立数字电路规划,受制于器材自身的功用,导致电路履行速度慢、体积巨大、集成程度低,晋级难度大。而选用微处理器、DSP、FPGA等现代手法构成的只能操控体系是新一代运动操控开展的方向。本文对依据FPGA的嵌入式运动操控器进行了研讨,并应用了CAN总线,使硬件接口简略、实时性强、灵敏度高,有很强的实用价值。

1 全体方案规划战略

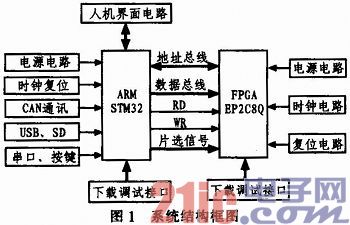

本体系以意法半导体体公司出产的依据Cortex—M3处理器STM32F103VBT6芯片中心进行通讯、数据的存储以及键盘扫描和LCD显现,它集成了CAN、SPI、USB、USART操控器,满意体系的规划要求,简化的体系的完结进程,丰厚的函数库大大缩短了用户的开发周期。而FPGA作为体系首要的履行机构,运用其高速性进行算法完结、速度操控和方位操控,体系的全体结构如图1所示。

2 运动操控器的功用模块规划

为了满意整个体系的作业,运动操控首要由通讯和数据处理两部分构成,通讯和数据存储由STM32担任进行,出于数据运算的复杂性和实时性,FPGA处理算法的完结。本规划相对巨大,模块纷歧一介绍。

2.1 CAN通讯模块的规划

2.1.1 硬件规划

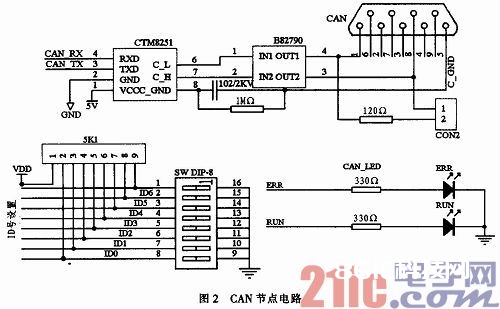

bxCAN是STM32内置的CAN操控器,支撑2.0A和2.0B CAN协议,波特率最高可达可到达1 Mbit/s,包含3个发送邮箱,3级深度的2个接纳FIFO,14个可变位宽的过滤器组,支撑时刻触发通讯形式,它的规划方针是以最小的CPU负荷来高效处理许多收到的报文,它也支撑报文发送的优先级要求(优先级特性可软件装备)。CAN硬件规划如图2所示。

以CTM8251作为收发芯片,它不仅能完结收发功用,还具有DC2500V的阻隔功用,使体系与外界阻隔开来,简化了CAN外围的硬件规划,进步了体系的性价比,图中120 Ω的电阻为可选用的终端匹配电阻,假设网络中现已存在一对匹配电阻,则该电阻能够不运用,其间B82790是个共模扼流线圈,作用是按捺共模搅扰平衡差分信号的传输;本规划中选用比较常用的拨码开关电路设置CAN网络的ID地址和波特率;LED作为通讯状况指示。

2.1.2 软件规划

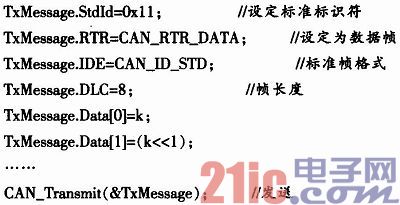

针对STM32对外设的设置,咱们只需要对相应的参数进行恰当的装备就能满意规划的要求,软件部分首要任务只需进行CAN初始化和数据发送即可。本规划初始化模块中只需要对CAN作业方法进行装备,而不需要对过滤器进行特别的装备,部分初始化程序如下:

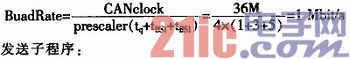

作业方法装备中最首要的是波特率的装备,本规划中选用AHB1作为CAN时钟为36 MHz,所以要得到1 Mbit/s的波特率进行了以上的设置,即SJW=tq,BS1=3tq,BS2=5tq,CAN_Prescaler=4,所以波特率的核算如下:

2.2 FPGA电路的规划

FPGA电路首要完结运动操控的相关算法,包含加减速算法、检测设备算法、插补算法等算法的完结,是整个规划的要害部分,硬件规划首要包含FPGA的供电电路、时钟电路和装备电路,都是相对比较惯例的电路,在这里不做介绍,文中首要介绍相关算法的完结。

2.2.1 加减速模块

为了在电机启动时为了在电机启动时,防止电机在运转以及换速的进程中发生冲击、超程、失步和振动等一些咱们不想见到的现象。为了使履行机构能够平稳和准确的定位,这就要求电机在开机到电机的速度到达给定的进给速度的进程中有一个加减速的进程,使其能够滑润的过渡。防止速度的突变给电机带来损害。

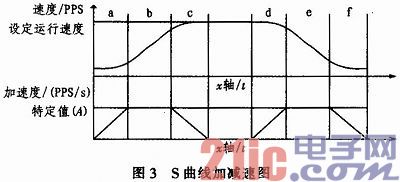

S型曲线加减速是比较抱负的操控加减速办法,但怎么确保结构的曲线滑润、准确成为许多算法工程师研讨的要点。如图3所示,在加快的进程中,有3个不同的加快度区域。在开端阶段,加快度是按线性方法以必定的加快度率K从0增加到固定的加快度值A。也就是说,这时驱动速度在a区域是按抛物线的方法增加;接着在b区域中,驱动速度是以一个安稳的加快度增加;终究,在c区域中,加快度则依照加快度率K线性削减到0。这样,S曲线的加快度进程就能够看作是由a,b,c 3个区域构成的。在减速的进程中,同加快进程相同,d,e,f区域中也是按抛物线的方法减速。

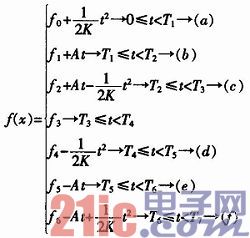

依据此本规划结构的速度、加快度、时刻的对应函数如下:

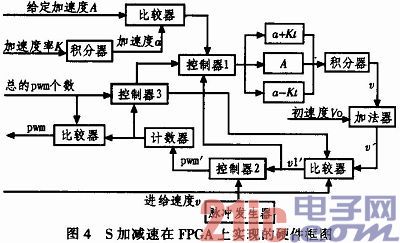

S加减速在FPGA中的完结,如图4所示。在已知给定加快度A、加快度率K、初速度V0、以及进给速度V和总的pwm脉冲数的情况下,就能够得到S加减速曲线。

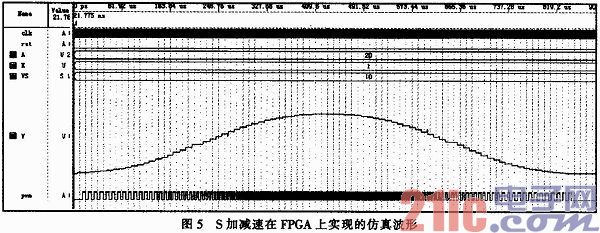

图5为本规划在Quartus II中的仿真波形,为了加快仿真的速度,特意在仿真而前对某些参数进行了修正。

本体系的加减速模块的结构满意速度和加快度曲线的结构满意速度改变平稳,加快接连等条件,开始和停止速度与要求速度共同,加快度为0,加快度率K能够依据实际需要随时调整,通用性很好。

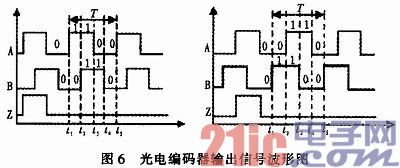

2.2.2 光电编码器模块

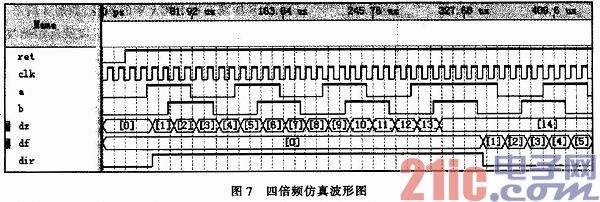

本体系选用的闭环操控,反应信号的精度直接影响定位、测速,在此选用增量是编码器进行定位操控,增量式编码器首要是运用两个相差90度的方波信号A和B,和零位脉冲信号Z进行角位移和方向判别(如图6所示),然后到达了检测方位的意图,此外,咱们将A或B信号四倍频,则计数脉冲的周期将减小到T/4,然后使角位移丈量精度进步4倍。四倍频后的编码器信号,需经计数器计数后,才干转化为相对方位。由两个与非门、一个非门逻辑、D触发器组成传统的波形转化电路,经过它来将A相、B相脉冲转化成正向计数信号dz、反向计数信号df和方向(dir)信号,经过正反方向的数字信号加减完结终究的计数,终究的仿真数据如图7所示。

3 结束语

本课题研讨是依据某品牌雕刻机操控体系规划进行的总结,旨在树立一种通用的运动操控器,经过该运动操控器以及体系其它部分的协同作业,整个操控体系实时性、牢靠性好,满意了操控要求。通讯十分安稳,相关算法还有待优化。

- STM32单片机中文官网

- STM32单片机官方开发工具

- STM32单片机参阅规划