CMOS图画灵敏器是近年来鼓起的一类固态图画传感器。CMOS图画灵敏用具有低成本、低功耗(是CCD耗的1/1000~1/100)、简略的数字接口、随机拜访、运转简易(单一的CMOS兼容电池供应)、高速率(可大于1000帧/秒)、体积小以及通过片上信号处理电路能够完结智能处理功用等特色而得到广泛运用。有些CMOS图画灵敏用具有规范的I2C总线接口,可便利运用到体系中。有些没有这类总线接口电路的专用CMOS图画灵敏器需求添加外部驱动电路。因为CMOS灵敏器的驱动信号绝大部分是数字信号,因而可选用FPCA通过Verilog HDL言语编程发生驱动时序信号。Verilog HDL言语是IEEE规范的用于逻辑规划的硬件描绘言语,具有广泛的逻辑归纳东西支撑,简练易于了解。本文就STAR250这款CMOS图画灵敏器,给出运用Verilog HDL言语规划的逻辑驱动电路和仿真成果。

1、CMOS图画灵敏器STAR250

STAR250是一款专为卫星地理导航的星跟踪器(tracker)规划的CMOS图画灵敏器。因为太空中含有很多辐射,芯片中加入了抗辐射电路以进步空间运用的可靠性。STAR250的技能指标如下:

(1)0.5μm CMOS工艺;

(2)512×512分辨率,像素巨细25μmx25μm;

(3)每个像素4个光敏二极管,进步MTF(幅值转化功用)和削减PRNU(非均一化光呼应);

(4)抗辐射规划;

(5)片上双采样电路抵消FPN(固定方式噪声);

(6)电子快门:

(7)最大30帧/秒;

(8)能够取子窗口;

(9)片上10位ADC;

(10)陶瓷JLCC-84针封装。

STAR250是有源像素的线扫描CMOS图画灵敏器。一切像素的输出都连接到列总线,并且在列总线上每例都有一个列扩大器。运用二次采样技能,操控列扩大器能够从读出信号中减去光敏单元上一次收集残留的电荷。片上ADC独立于灵敏器,能够运用也能够通过软件封闭,而用外部的ADC。STAR250为了运用便利有多种读出数据的办法(窗口办法、电子快门等),不同的读出办法有不同的时序要求。

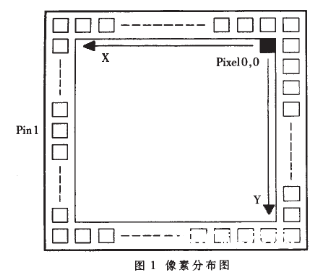

传统的计算机或打印机的图画座标系界说左上角为原点(0,0),在STAR250中界说右上角为原点(0,0),如图1。这样灵敏器输出数字信号后能够便利地转化为计算机格局的图画,便利后续的处理。窗口扫描办法是从上向下、从左向右一个像素一个像素地扫描。

2、STAR250时序信号

STAR250通过两个进程完结图画的收集。第一步是逐行扫描RESET像素。行内像素RESET后,本行自上一次RESET或读出后堆集的一切光敏电荷被排空。从RESET行像素开端新的曝光周期。第二步是本次曝光周期数据读出。以电压的方式读出,然后通过ADC转化为数字量。因为电荷选用排出式读取,CMOS图画灵敏器的像素读出不行康复,读取进程也相当于RESET像素,所以CMOS灵敏器行RESET的速度与读取速度相同。

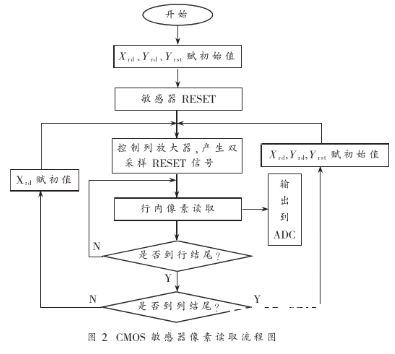

STAR250通过三个指针标定整个图画地址:Yrd当时扫描行,Yrst当时RESET行,Yrd当时读出像素。这三个指针都有相应的移位寄存器,通过设置这三个寄存器的初始值能够调整收集窗口的巨细和方位。图画收集的流程图如图2。每秒钟的图画帧数通过设置Yrd和Yrst进行操控,曝光周期也由这两个量操控。这个时刻量能够用空间间隔(行距)表明,界说DelayLines=︱Yrst-Yrd+︱。因为每一行的RESET和读取时刻是固定的,所以DelayLines假如固定那么帧率也就固定了。将DelayLines转化成像素的有用积分时刻(曝光时刻),是将Delay-Lines乘以读取一行像素所用的时刻。读取一行像素所用的时刻由四部分组成:(1)行中有用像素的个数(由行的长度界说);(2)读取一个像素所用的时刻;(3)像素累积电荷转化为数字量的时刻;(4)挑选新一行所用的时刻。例如在主时钟频率为12MHz时,像素的输出频率为主时钟的二分频6MHz,因而一行像素所需求的时刻为512×1/6MHz=85.3μs。再加上换行所需时刻,一行像素的读取时刻大约90μs左右。因而能够依据这个时刻设置DelayLines来操控曝光时刻。

3、Verilog HDL驱动时序规划

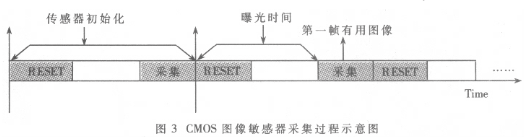

通过以上剖析可知,CMOS图画灵敏器收集时能够分为RESET进程和收集进程。时刻上两个进程是独立的,如图3。但在FPGA内部处理这两部分的电路物理上是一起存在,因而有必要将相应的信号通过置标志位的办法置为有用或无效。

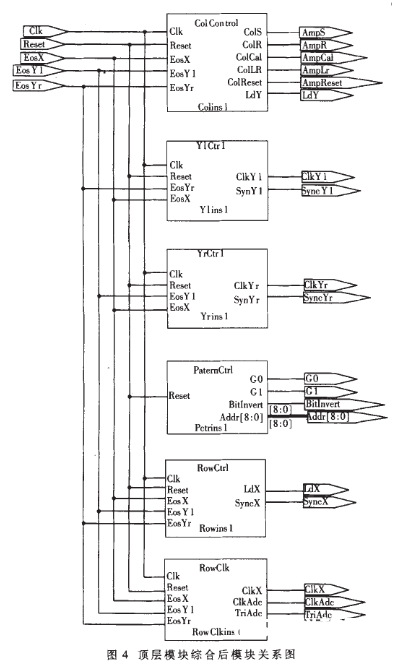

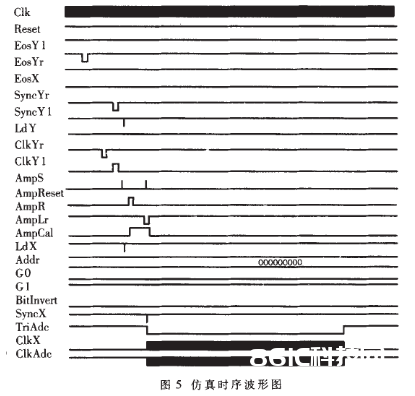

STAR250所需数字驱动信号共28个,其间SELECT信号在正常运用时,直接接PCB板的Vcc。因而需FPGA操控的驱动信号有27个。依据收集进程能够把信号区分为列扩大器信号,包含CAL、Reset、Lr、S、R、LdY。这6个信号在每一行的初始化部分都要用到,因而能够编写到一个模块(ColControl)中;方式信号(PaternCtrl)模块用来设置CMOS灵敏器的作业方式及初始地址,包含G0、G1、Bitlnvert和Addr[8:0]共12个信号。其间G0、G1用来规划输出的扩大倍数,BitInvert用于将输出取反,Addr[8:0]则设置收集的开始地址;行读出信号操控模块(YlCtrl)发生行读出地址的同步信号SyncYl及时钟驱动信号ClkYl;行RESET信号操控模块(YrCtrl)发生行RE-SET地址的同步信号SyncYr及时钟驱动信号ClkYr;像素操控模块(RowCtrl)发生行内像素初始地址的装载信号LdX及同步信号SyncX;行内时钟信号模块(RowClk)发生列内像素的时钟驱动CLKX、ADC驱动时钟信号CLkAdc及输出三态操控信号TriAdc。体系的输入信号为主时钟CLK、EosX行内像素结束信号、EosYl帧熟行结束信号、EosYr帧内RESET行结束信号、芯片的RESET信号。通过这样区分后的模块化Verilog程序就比较易写了。通过顶层模块归纳生成的网表如图4。布线仿真时序图如图5,其间时钟信号过于密布变成黑色带状,相同输出时钟CIkX及ClkAdc也是黑色带状。在时序上ClkX与ClkAdc是反相联系,在TriAdc坚持低电平时输出有用。所规划的驱动信号仿真波形与理论波形非常契合。这样就完结了STAR250的时序驱动电路规划。

运用Verilog言语设计时序逻辑具有很高的功率。结合CMOS灵敏器特性能够便利地开宣布驱动时序电路。但有必要对CMOS图画灵敏器的信号剖析精确,正确别离那些独立的信号和共用的信号,用时序逻辑规划驱动信号,用组合逻辑完结不同收集进程时刻上的别离。布线推迟是有必要考虑的,选用流水线技能能够猜测推迟,确保信号的正确性。尽管文中并未给出像素ADC输出的存储电路,但实际上直接运用TriAdc信号作为SRAM的片选,ClaAdc的低电平作为写信号,SRAM的地址在ClkAdc的上升沿添加、下降沿写入。这样就能够完结图画数据的存储。以上Verilog程序在FLEXl0kl0上布线完结。经示波器调查逻辑正确,CMOS灵敏器正常作业。

责任编辑:gt