1 导言

现场可编程门阵列FPGA是一种由用户完结芯片功用的器材,用户在规划完结之后能够进行功用仿真,也能够现场编程进行验证,有利于及早发现问题,完善规划,具有极大的灵活性和通用性。可编程器件在电子体系规划中的运用日益增多,位置也越来越重要。跟着规划的不断扩大,速度和功用不断进步,一个电子体系的大部分电路,如:操控电路、逻辑电路、接口电路、运算电路等都能够由一片可编程器材完结。

在日常日子生产中,常常需求传输低速的数据信号,供现场监测、施行操控等需求信息传输的环境运用。因为可运用的无线频率资源有限,一般需求选用有线方法传输数字信号。因而有必要研讨数字信号在基带体系中长途传输的问题。在参考文献中,作者经过仿真,探讨了数字信号经过基带体系长途传输的可行性,提出在发送端和接纳端对信号进行滤波和扩大的处理方案。在信号实践传输过程中,还受许多条件的束缚,如:为了便利接纳端提取位守时信息,需求对基带信号编码,挑选适宜的传输码型;受有线信道传输特性的影响,基带信号不该含有较多的高频和低频成分;为了减小噪声对有用信号的搅扰,需求采纳过失操控技能;为减小码间搅扰,进步频带利用率,需求选用频谱改换技能等。

针对低速数字信号的基带传输问题,在理论剖析、构建模型的基础上,对其间的数字滤波环节,选用MAXPLUSІІ软件编程,对FPGA的硬件结构和工作方法进行重构来完结,合作MAX7000S系列的FPGA芯片完结中长途基带传输。

2 发送单元规划

原始的数字信源中会呈现长期的连“0”符号,若直接传输,接纳端守时康复体系难以确保收守时信号的准确性,从获取守时信息等视点考虑,需求将原始的信息符号编制成适合于传输用的码型。编码后的信号电平为TTL电平,不适合远间隔传输,需求扩大后发送。

选用矩形脉冲传输数字信源,它的功率谱的高、低频重量都非常丰厚,具有这样特色的信号在有线信道中传输会发生严峻畸变。此外,在数字信号长途传输时,还需求尽或许地进步频带利用率,下降码间搅扰。从这些视点考虑,选用双二进制编码来改动传输信号的频谱结构,进步抗码间搅扰的才能。在实践规划中,选用运用得最广的第Ⅳ类部分呼应波形。

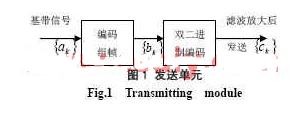

归纳考虑上述要素,基带信号发送端的组成结构如图1所示。选用根据MAXPLUSⅡ10.1软件渠道的Verilog-HDL硬件描绘言语来规划编码、装帧和双二进制编码模块。

2.1 线路码编码及帧结构规划

基带信号传输码型品种繁复,其间,双相码以其编译码简略、守时信息丰厚等特色在本地局域网中得到广泛运用,结合低速数据传输的条件,挑选双相码作为线路码型。双相码又称Manchester码,它的编码规矩是:0固定地用“01”(0相位波形)表明,1固定地用“10”(π相位波形)表明,或反之,是1B2B码。

根据Verilog-HDL言语对双相码编码建模。根据编码原理能够看到:关于“0”,它的第一位编码是“0”,第二位编码为“1”;而关于“1”,它的第一位编码为“1”,第二位编码为“0”。这样,咱们只需设置一个相位时钟phase,在其一个周期内完结双相位编码:在phase 的“1”半周,总是输出信码的原码;在“0”半周总是对原码取非后输出。

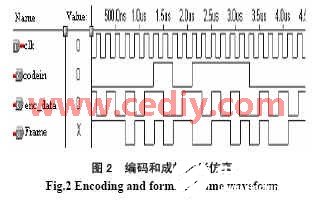

phase是经主时钟clk二分频得到的相位脉冲;codein为信码输入,时钟频率与phase相同;enc_data为编码输出。

在接纳端对双相码解调时,需求供给分组信息,以便于同步接纳;为减小噪声对信码的影响,需求进行过失操控编码,使码组具有必定的纠检错才能,等。因而在发送端需求进行帧结构规划。本规划模块中每一帧由同步头(3bit)、信息位(16bit)、奇偶校验位(1bit)构成,总计20bit,用于低速数据传输。为了使信息码与同步码有所区别,挑选“111”作为同步码。因为双相码的编码功率是50%,所以16位信息位传递的原始信码位数是8位。校验方法选用偶校验。选用软件编程完结。编码及成帧的仿真波形如图2所示[4]。图中codein是原始信码,enc_data为线路码,Frame为组帧后的成果。从图中能够看出,原始信码的一个码段“00010111…”编码后的成果为“0101011001101010…”,码速率是原始信码码速率的2倍,这一码段附加帧头和奇偶校验位成帧后为“11101010110011010100…”。

2.2 双二进制编码

双二进制编码包含预编码和相关编码两个部分。

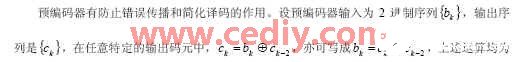

2.2.1预编码器

模2运算。预编码器完结的逻辑运算功用,选用一个异或逻辑单元和两个D触发器做延时单元即可完结。如图3所示。

这一单元在MAXPLUSⅡ软件渠道下选用图形修改法完结。

2.2.2相关编码器

选用TL082集成运算扩大器及电阻、电容构成减法电路,预编码器输出的![]() 作为减法器的输入端,完结相关编码运算,构成输出信号,它的脉冲为双极性,巨细持平。输出信号经过低通滤波、功率扩大之后发送。

作为减法器的输入端,完结相关编码运算,构成输出信号,它的脉冲为双极性,巨细持平。输出信号经过低通滤波、功率扩大之后发送。

3 接纳单元规划

接纳单元的作用与发送单元相反,它从接纳到的信号中康复出发送的数字信号。

接纳端对接纳到的信号,进行二阶有源带通滤波、扩大之后,再进行判定。因为在规划中数字信号选用单极性波形传输,因而相关编码器的输出序列 有三种或许的逻辑值: 和0。接纳端的判定规矩是: 判为1,0判为0。根据这一特色,在实践规划中先对滤波扩大后的信号进行全波整流,然后再进行抽样判定,然后简化接纳电路。

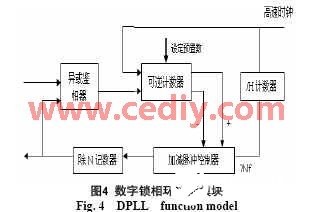

接纳端的位守时信息由根据FPGA的数字锁相环提取。FPGA在数字锁相环的规划上存在杂乱的时序合作,因而将锁相环各部分的功用分红4个模块:鉴相器、K模可逆计数器、脉冲加减计数器和N分频器,别离完结。DPLL的首要功用模块见图4。

异或鉴相器默许的确定相位是与输入信号相位相差90°的时钟信号,而位同步时钟的一个周期刚好和最小的一个码元长度持平,故将本地发生的预算信号在进行异或鉴相之前进行分频,使其半个周期的长度刚好与一个码元宽度持平。当本地预算信号的上升沿刚好与输入码流的跳变沿相对,便是正确的位同步时钟时,输入码流与分频后的信号进行异或后发生占空比为1:1的方波。当本地预算信号超前于输入码流时,鉴相输出在一个周期内0比1多;不然1比0多;由此能够判别相位的超前和滞后。

K模可逆计数器构成环路滤波器,在环路中对输入噪声起抑制作用。它对鉴相器输出信号进行可逆计数,当计数成果到达必定值时,便输出增、扣脉冲信号,操控DCO对相位进行调整。

加减脉冲操控器和除N计数器构成数控振荡器。脉冲加减电路经过“增”脉冲或“扣”脉冲完结了对输入信号频率和相位的盯梢和调整,最终使输出信号确定在输入信号的频率和相位上。除N计数器对脉冲加减电路的输出再进行N分频,得到本地预算信号。

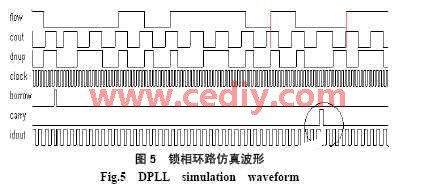

对选用Verilog-HDL言语建模的锁相环提取位守时程序进行编译和仿真,仿真波形如图5所示。

由上面的仿真波形能够看出,开始时输入码流flow的跳变沿与本地预算信号cout的上升沿没有对齐,未完结相位确定。根据鉴相器输出的相位差dnup判别,在一段时间内0比1呈现的次数多,由此阐明本地预算信号的相位超前于输入码流的相位,经过环路滤波器后,发生1bit的扣脉冲信号(在图中右侧标出),使本地预算信号相位向后延时了1bit,然后到达了相位确定的意图。

以传输64 KHz的数字基带信号为例,当环路锁守时DCO的输出频率为512KHz,经过8分频后可得位守时。

抽样判定后得到的是组帧的线路码,根据偶校验规矩,判别帧内码是否犯错,若无错,对线路码拆帧,去掉帧头和校验位,输出信码;若有错,采纳丢掉一帧的处理方法。关于采样、监测等对精度要求不高的低速数据传输场合,这种方法能够满足要求。

上述程序经过编译,适配到EPM7128方针芯片,与外围硬件电路合作,完结了数字信号长途基带传输问题。本体系理论传输间隔可达10km,在实验室条件下选用伪码进行测验,传输线选用一般五类非屏蔽双绞线,间隔约300m时,康复出的基带信号波形与直连相同,证明选用编码、抗码间搅扰及滤波扩大等技能,较好地处理了长途基带传输问题。

4 小结

本规划的立异之处是:选用FPGA编程处理了数据经过中长途基带体系传输过程中的数字滤波问题,包含编码、频谱改换、位守时提取和译码等首要数字滤波环节。所规划的体系码间搅扰小,传输作用好。因为选用可编程器材进步了体系的集成度和可靠性,下降了功耗和本钱,增强了体系的灵活性。体系中的单元模块具有较好的通用性,能够作为根本单元电路移植到其他低速中长途数据传输场合。

责任修改:gt