AP0100CS集成了ApTIna的先进图画处理管道(pipeline),具有令人惊叹的视频和低光照功用。凭借用于宽动态规模图画再现(rendering)的高档部分色彩映射(Advanced Local Tone Mapping, ALTM)功用,即便在十分困难的高对比度照明条件下也可以生成高质量的视频。AP0100CS集成了具有高档转换器功用的NTSC/PAL编码器,可以供给模仿CCTV商场所需的高TV线分辨率。

这款产品为中国商场规划人员供给了曩昔无法获取全新相机规划方案;也就是说,可以使用高端IP相机传感器的高分辨率、内涵的杰出低光照功用及WDR才能,移植应用于模仿CCTV监控范畴。这种强壮的规划灵活性将会带来令人激动的新式监控摄像机。

典型操作

A typical READ or WRITE sequence begins by the master generaTIng a start condiTIon on the bus. After the start condiTIon, the master sends the 8-bit slave address/data direction byte. The last bit indicates whether the request is for a READ or a WRITE, where a “0” indicates a WRITE and a “1” indicates a READ. If the address matches the address of the slave device, the slave device acknowledges receipt of the address by generating an acknowledge bit on the bus.

If the request was a WRITE, the master then transfers the 16-bit register address to which a WRITE will take place. This transfer takes place as two 8-bit sequences and the slave sends an acknowledge bit after each sequence to indicate that the byte has been received. The master will then transfer the 16-bit data, as two 8-bit sequences and the slave sends an acknowledge bit after each sequence to indicate that the byte has been received. The master stops writing by generating a (re)start or stop condition. If the request was a READ, the master sends the 8-bit write slave address/data direction byte and 16-bit register address, just as in the write request. The master then generates a (re)start condition and the 8-bit read slave address/data direction byte, and clocks out the register data, 8 bits at a time. The master generates an acknowledge bit after each 8- bit transfer. The data transfer is stopped when the master sends a no-acknowledge bit.

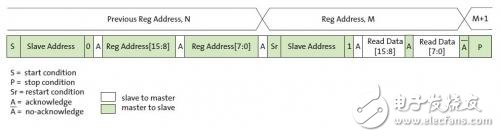

单次随机读

Figure1 shows the typical READ cycle of the host to the address. The first two bytes sent by the host are an internal 16-bit register address. The following 2-byte READ cycle sends the contents of the registers to host.

Figure 1: Single READ from Random Location

单次当时方位读取

Figure 2 shows the single READ cycle without writing the address. The internal address will use the previous address value written to the register.

Figure 2: Single Read from Current Location

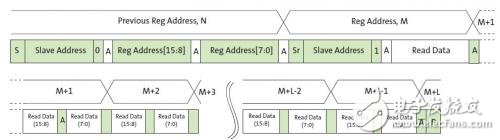

从恣意方位开端衔接读取

This sequence (Figure 3) starts in the same way as the single READ from random location . Instead of generating a no-acknowledge bit after the first byte of data has been transferred, the master generates an acknowledge bit and continues to perform byte READs until “L” bytes have been read.

Figure 3: Sequential READ, Start from Random Location

从当时方位开端衔接读取

This sequence (Figure 4) starts in the same way as the single READ from current location (Figure 2). Instead of generating a no-acknowledge bit after the first byte of data has been transferred, the master generates an acknowledge bit and continues to perform byte reads until “L” bytes have been read.

Figure 4: Sequential READ, Start from Current Location

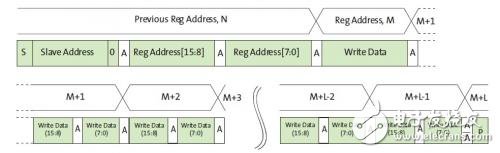

对恣意方位写入

Figure 5 shows the typical WRITE cycle from the host to the AP0100CS.The first 2 bytes indicate a 16-bit address of the internal registers with most-significant byte first. The following 2 bytes indicate the 16-bit data.

Figure 5: Single WRITE to Random Location

从恣意方位开端接连写入

This sequence (Figure 6) starts in the same way as the single WRITE to random location (Figure 5). Instead of generating a no-acknowledge bit after the first byte of data has been transferred, the master generates an acknowledge bit and continues to perform byte writes until “L” bytes have been written. The WRITE is terminated by the master generating a stop condition.

Figure 6: Sequential WRITE, Start at Random Location